在芯片前端設(shè)計(jì)工程師的日常工作中,需要用硬件描述語言Verilog HDL將各種算法/協(xié)議等實(shí)現(xiàn)后,再進(jìn)行RTL的功能仿真,以便在軟件環(huán)境中,驗(yàn)證電路的行為和設(shè)想中的是否一致。這也意味在流片前,工程師需要花大量時間利用數(shù)字仿真器來驗(yàn)證芯片,保證其功能的正確。

作為芯片驗(yàn)證必不可少的一個環(huán)節(jié),仿真技術(shù)是保證芯片功能正常的關(guān)鍵簽核(sign-off)技術(shù),通過計(jì)算機(jī)結(jié)合測試激勵來模擬芯片在真實(shí)環(huán)境下的運(yùn)行狀況,幫助工程師通過各種調(diào)試手段來判斷運(yùn)行結(jié)果是否符合預(yù)期。數(shù)字仿真器主要是針對數(shù)字電路的仿真,設(shè)計(jì)工程師需要應(yīng)用硬件描述語言來設(shè)計(jì)電路,而驗(yàn)證工程師也需要用抽象層的HDL來搭建測試環(huán)境;仿真工具需要解釋編譯這些HDL代碼,并計(jì)算出仿真結(jié)果,以便工程師檢查結(jié)果。

伴隨設(shè)計(jì)驗(yàn)證語言和方法學(xué)不斷推陳出新,各種應(yīng)用平臺也層出不窮。這一系列的技術(shù)發(fā)展都給數(shù)字仿真器帶來了前所未有的挑戰(zhàn)。設(shè)計(jì)具有競爭力的片上系統(tǒng)(SoC)需要合理地利用各種高精尖的技術(shù)。對于數(shù)字仿真器來說,它面臨的挑戰(zhàn)不僅僅是芯片規(guī)模上的增長,還有伴隨而來的一系列問題,包括:算力受限、調(diào)試效率低下、平臺單一化等。

多年來,業(yè)內(nèi)人士通常認(rèn)為一款好的數(shù)字仿真器,應(yīng)該具備以下條件:

保障仿真結(jié)果的正確性和一致性,滿足sign-off (簽核)的要求

具備對IEEE1364和IEEE1800標(biāo)準(zhǔn)語法的支持,具有語法點(diǎn)、功能點(diǎn)的合規(guī)性

仿真器核心可以實(shí)現(xiàn)高效的調(diào)度器,靈活強(qiáng)大的隨機(jī)求解器

在調(diào)試方面,工具應(yīng)當(dāng)緊密融合各種調(diào)試應(yīng)用,提高調(diào)試有效性

但更進(jìn)一步,針對產(chǎn)業(yè)發(fā)展現(xiàn)狀的痛點(diǎn),先進(jìn)的數(shù)字仿真器還應(yīng)該具備以下特質(zhì):

為了進(jìn)一步利用新的計(jì)算架構(gòu)和平臺,除了傳統(tǒng)的X86,更能無縫地支持如ARM等其他新型處理器架構(gòu)及原生云計(jì)算架構(gòu),并能有效利用并行計(jì)算支撐高性能編譯與運(yùn)算

仿真器和其他驗(yàn)證工具具有高度的融合性,及統(tǒng)一覆蓋率的數(shù)據(jù)結(jié)構(gòu),以保證各種工具覆蓋率收集的有效性

芯華章仿真器核心研發(fā)團(tuán)隊(duì)具備數(shù)十年相關(guān)領(lǐng)域研發(fā)經(jīng)驗(yàn),曾在跨國公司成功主導(dǎo)過大型仿真器項(xiàng)目,對驗(yàn)證語言、方法學(xué)、仿真器核心構(gòu)架、算法、優(yōu)化有著豐富的技術(shù)儲備。

基于對前沿技術(shù)發(fā)展趨勢的的判斷,并結(jié)合行業(yè)現(xiàn)實(shí)的挑戰(zhàn)進(jìn)行深入的研究和探索,芯華章在經(jīng)過一年多的研發(fā)積累,并得到國內(nèi)多個知名客戶配合打磨后,推出一款獨(dú)立自主、全新架構(gòu)的國內(nèi)領(lǐng)先水平仿真器——穹鼎 GalaxSim。該產(chǎn)品創(chuàng)新性地使用新的軟件框架,提供多平臺支持,并且已在多個基于ARM平臺的國產(chǎn)架構(gòu)上測試通過。

目前,穹鼎GalaxSim支持IEEE1800 SystemVerilog 語法、IEEE1364 Verilog 語法,以及IEEE1800.2 UVM方法學(xué),在語義解析、仿真行為、時序模型上,已達(dá)到主流商業(yè)仿真器水平。穹鼎GalaxSim仿真器能夠提供統(tǒng)一的覆蓋率數(shù)據(jù)庫,并兼容芯華章旗下穹瀚GalaxFV等其他驗(yàn)證工具,結(jié)合穹景GalaxPSS智能驗(yàn)證系統(tǒng)提供的豐富測試場景,可以加速覆蓋率收斂,高效地解決業(yè)界其他工具缺乏兼容性的問題,進(jìn)一步提高驗(yàn)證效率。

使用穹鼎GalaxSim的驗(yàn)證實(shí)例

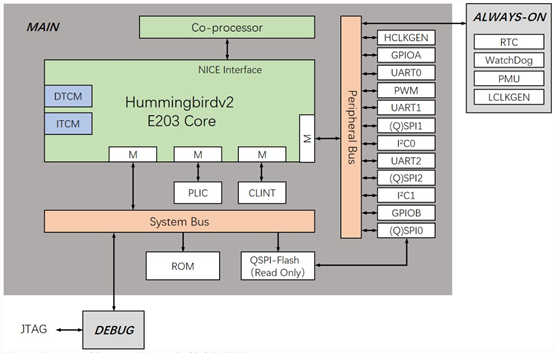

為了驗(yàn)證GalaxSim仿真的功能正確性,調(diào)試的易用便捷性,以及性能上是否能夠滿足客戶的需求,我們特地把基于Verilog語言的蜂鳥E203開源 RISC-V CPU設(shè)計(jì)運(yùn)行在芯華章的仿真器上,作為一個演示demo。

蜂鳥E203是國內(nèi)首個開源RISC-V處理器,從2018年發(fā)布至今,積累了廣泛的用戶。E203內(nèi)核采用2級流水線結(jié)構(gòu),能夠運(yùn)行RISC-V指令集,支持RV32IMAC等指令子集的配置組合,具備工業(yè)級開發(fā)標(biāo)準(zhǔn),符合當(dāng)前處理器架構(gòu)往DSA(Domain Specific Architecture)發(fā)展的新趨勢,因而具有廣泛的代表性。

開源蜂鳥E203 SoC整體框圖

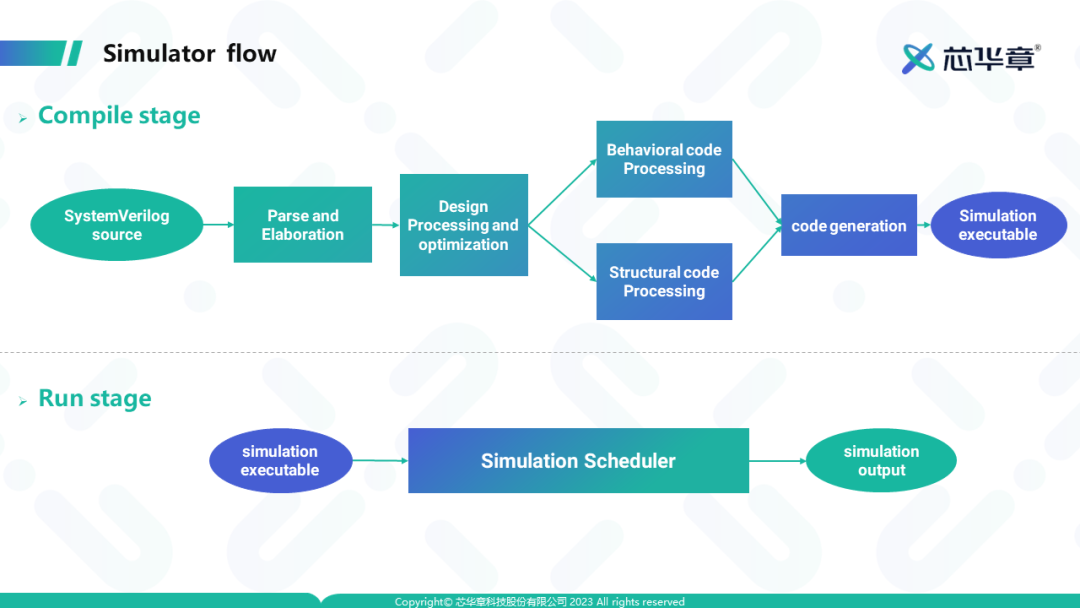

穹鼎仿真器首先需要讀取芯片設(shè)計(jì),之后經(jīng)過解析和抽象,轉(zhuǎn)換為仿真器內(nèi)部緊湊高效的數(shù)據(jù)結(jié)構(gòu),并基于新一代編譯技術(shù),快速生成原生平臺仿真程序。同時,我們打開波形調(diào)試工具,IC工程師即可以運(yùn)行仿真程序來進(jìn)行驗(yàn)證。

編譯完成后,我們執(zhí)行仿真程序。程序在運(yùn)行后,同時進(jìn)行信號波形的文件轉(zhuǎn)儲,以供調(diào)試。本次驗(yàn)證實(shí)例中的環(huán)境技術(shù)包含多款國產(chǎn)化產(chǎn)品,涉及芯片設(shè)計(jì)、處理器、服務(wù)器、操作系統(tǒng)等環(huán)節(jié)。

穹鼎 GalaxSim基于芯華章FusionVerify 智V驗(yàn)證平臺,支持自主研發(fā)的新波形格式及波形調(diào)試工具,用戶能夠方便地查看信號波形,快速定位到缺陷的時間片和異常信號,從而進(jìn)行修復(fù)。

同時,我們還用同樣的設(shè)計(jì)放在第三方仿真器上運(yùn)行。這樣,一方面對比仿真結(jié)果以探索功能的正確與否,另一方面可以對比仿真的效率,便于對比工具的性能指標(biāo)。

經(jīng)過實(shí)測和比較,GalaxSim運(yùn)行結(jié)果完全和商業(yè)仿真器一致,性能也達(dá)到預(yù)期的要求。多個客戶試用在GalaxSim上運(yùn)行蜂鳥的demo后,表達(dá)了對產(chǎn)品的高度認(rèn)可:調(diào)試工具使用流暢,用戶界面操作友好易用,且支持不同處理器架構(gòu)。

產(chǎn)品亮點(diǎn)

國內(nèi)率先提出多架構(gòu)支持的仿真器,具備:

靈活的可移植性,友好的軟硬件生態(tài)支持

支持不同的處理器計(jì)算架構(gòu),包括X86、ARM、MIPS、RISC-V、NPU、GPGPU等

傳統(tǒng)的EDA工具大多數(shù)和單一CPU構(gòu)架耦合度高,例如某些EDA工具僅支持X86的平臺。一旦需要遷移到另一種平臺上,所需要的研發(fā)工作量是巨大的。如今,處理器生態(tài)越來越多樣化,未來的平臺不再是某個單一處理器的平臺,降低EDA工具對底層CPU構(gòu)架的耦合度,可以讓用戶更加有效地把工具部署在任何平臺上,也讓產(chǎn)品有更多應(yīng)用空間。

全面支持多種HDL語法,語義解析一致性強(qiáng)

兼容Verilog標(biāo)準(zhǔn)IEEE1364

全面支持SystemVerilog、UVM標(biāo)準(zhǔn)(IEEE1800,IEEE1800.2)

原生支持,不需要修改客戶源代碼

仿真器對語法正確解析決定了它能否正確理解設(shè)計(jì)意圖,同時也可以避免相同的編碼在不同的仿真器下產(chǎn)生不同仿真結(jié)果。Verilog標(biāo)準(zhǔn)(IEEE1364)和SystemVerilog標(biāo)準(zhǔn)(IEEE1800)定義的這兩種語言的語義非常的復(fù)雜,關(guān)鍵字眾多,各種組合情況近乎無窮。穹鼎GalaxSim可以在構(gòu)建仿真器的測試用例時考慮語法的各個方面,以及各種邊界場景,做到全面完整的測試。

調(diào)試功能卓越,可觀測性表現(xiàn)形式豐富

支持VCD和FSDB 波形導(dǎo)出(配合第三方庫)

支持芯華章自研波形格式XEDB

支持快速的代碼覆蓋率(Code coverage)

調(diào)試的重點(diǎn)在于可觀測性和可控制性。穹鼎GalaxSim針對不同的場景提供各種有效的數(shù)據(jù)表現(xiàn)形式,并在不同數(shù)據(jù)形式間可以同步數(shù)據(jù)標(biāo)注(annotation)。此外,穹鼎GalaxSim降低了工具的使用門檻,可以讓初級用戶也非常快速地掌握調(diào)試技術(shù),并且提供通用語言的二次開發(fā)的接口。

穹鼎GalaxSim的優(yōu)異性能得到了生態(tài)伙伴的高度認(rèn)可。

陳 剛

中科院半導(dǎo)體所副研究員

利用芯華章仿真工具GalaxSim,我們在兩周內(nèi)就將設(shè)計(jì)調(diào)通。和其他商用仿真器對比結(jié)果顯示,芯華章GalaxSim對RTL行為仿真行為正確,在性能上,很多場景和其他商用工具已經(jīng)基本一致。我們期待和芯華章的進(jìn)一步合作。

黃 武

芯華章科技產(chǎn)品和業(yè)務(wù)規(guī)劃總監(jiān)

為了保證語法的合規(guī)性和仿真精確度,我們對產(chǎn)品進(jìn)行了嚴(yán)苛的各種測試,包括對IEEE1364、IEEE1800各個語法點(diǎn)的分析,和結(jié)合主流商業(yè)仿真器的對比測試,確保工具在語義解析、仿真行為、時序模型上保持一致,從而有效幫助用戶提高驗(yàn)證效率,加快驗(yàn)證收斂速度。

原文標(biāo)題:全新架構(gòu)數(shù)字仿真器——穹鼎Galaxsim

文章出處:【微信公眾號:芯華章科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

453文章

50410瀏覽量

421849 -

仿真器

+關(guān)注

關(guān)注

14文章

1016瀏覽量

83644 -

開源

+關(guān)注

關(guān)注

3文章

3252瀏覽量

42407

原文標(biāo)題:全新架構(gòu)數(shù)字仿真器——穹鼎Galaxsim

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

基于單片機(jī)仿真器的設(shè)計(jì)詳解

芯華章將推出支持國產(chǎn)計(jì)算機(jī)架構(gòu)的國產(chǎn)驗(yàn)證EDA工具

EDA公司芯華章推出支持國產(chǎn)計(jì)算架構(gòu)的全新仿真技術(shù)

芯華章:啟程EDA 2.0新時代

Cadence全新Spectre FX Simulator仿真器,可提供高達(dá)3倍的性能提升和卓越的精確度

STM32-DAP仿真器的使用(1)

創(chuàng)新引領(lǐng)|芯華章聯(lián)手芯來科技提升RISC-V處理器設(shè)計(jì)驗(yàn)證

打破多項(xiàng)國產(chǎn)空白 芯華章率先發(fā)布數(shù)字驗(yàn)證調(diào)試系統(tǒng)

芯華章亮相首屆中國計(jì)算機(jī)學(xué)會芯片大會

芯華章宣布傅勇出任首席技術(shù)官,強(qiáng)強(qiáng)聯(lián)手加速打造系統(tǒng)級數(shù)字驗(yàn)證解決方案

解碼國產(chǎn)EDA數(shù)字仿真器系列之一 | 從零到一 如何構(gòu)建一款先進(jìn)的數(shù)字仿真器

如何構(gòu)建一款先進(jìn)的數(shù)字仿真器?

榮登國家級創(chuàng)新平臺!芯華章高性能數(shù)字仿真器穹鼎GalaxSim入選中關(guān)村論壇“新技術(shù)新產(chǎn)品榜單”

補(bǔ)齊重要版圖,國產(chǎn)EDA廠商實(shí)現(xiàn)全流程數(shù)字芯片前端驗(yàn)證!芯華章發(fā)布硬件仿真器,EDA2.0戰(zhàn)略更進(jìn)一步

詳解芯華章全新架構(gòu)數(shù)字仿真器

詳解芯華章全新架構(gòu)數(shù)字仿真器

評論