“本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括循環語句(forever、repeat、while和for)、運算符。”

01

—

循環語句

在Verilog中存在著4種類型的循環語句(forever、repeat、while和for),其中“while”與“for”的使用方法與C語言中的基本類似。

“forever”語句

語句格式如下: forever begin //add codes end

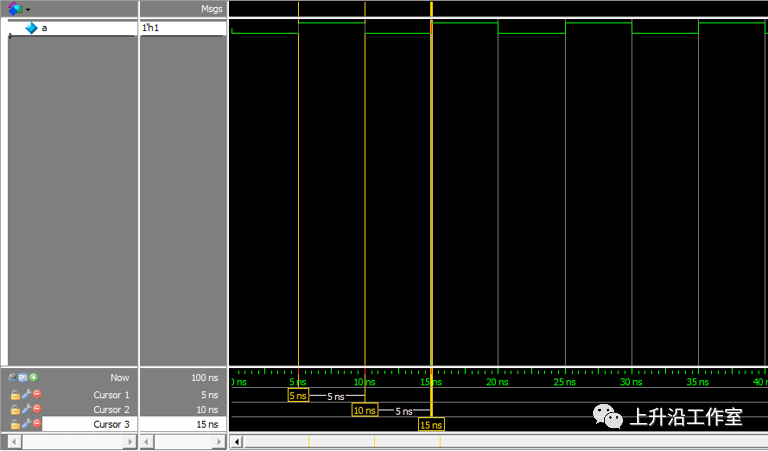

仿真效果如下:rega;initial begina = 0;foreverbegin#5 a = ~a;endend

-

“repeat”語句

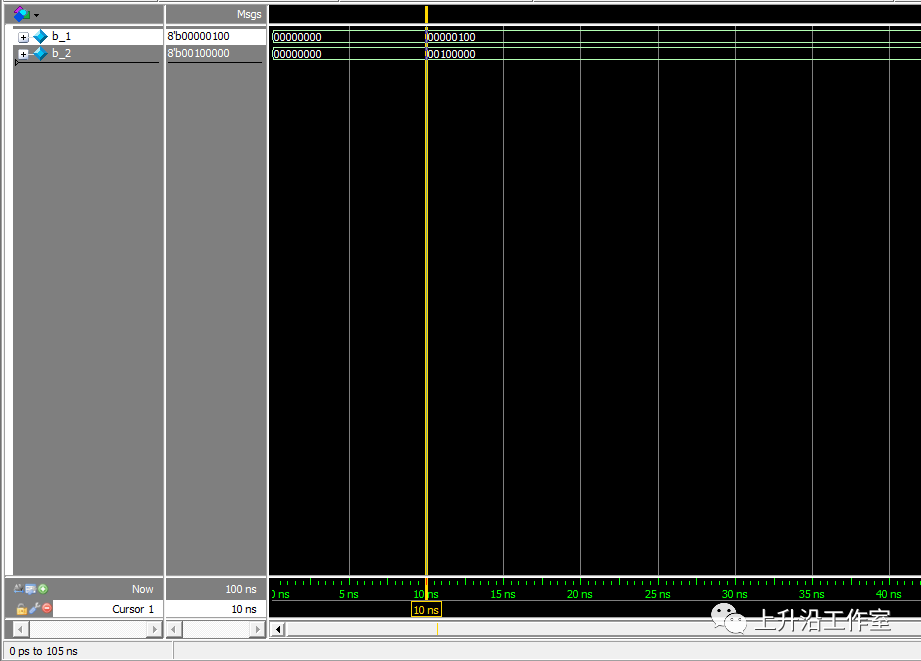

仿真結果如下:parameter times = 3;reg[7:0]b_1,b_2;initialbeginb_1 = 0;#10;b_1 = 8'b0000_0100;#10;endalways@(b_1)beginb_2 = b_1;repeat(times)beginb_2 = b_2 << 1;endend

在10ns的時候,b_1賦值為8’b0000_0100,這時候repeat語句觸發,b_2變成了8’b0010_0000,可見b_2右移了三位,也就是repeat內的語句重復執行了3次。

-

“while”語句

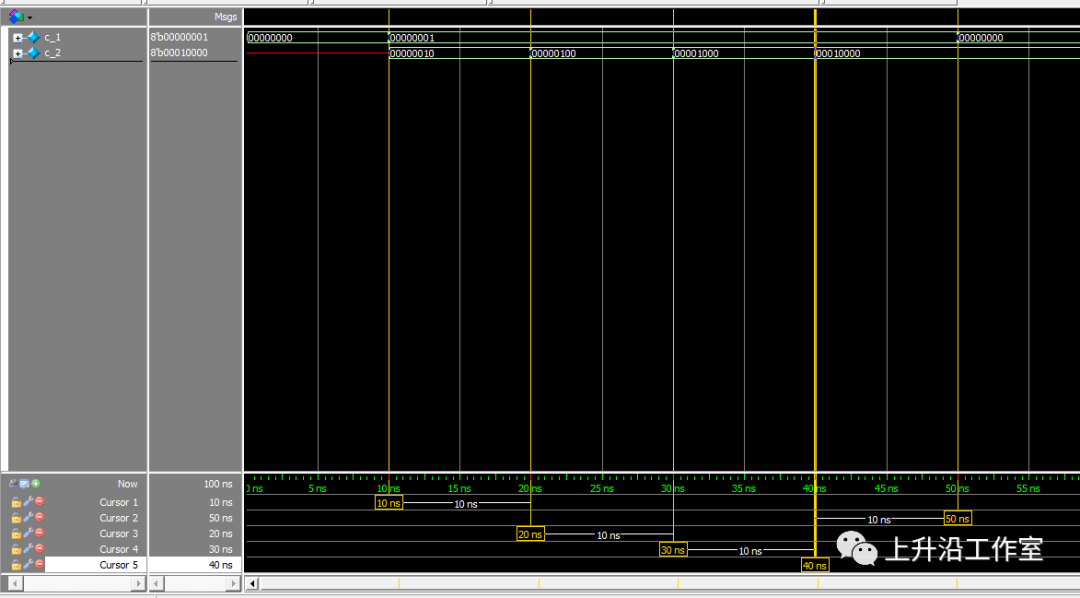

仿真結果如下:reg[7:0]c_1,c_2;initialbeginc_1 = 0;#10;c_1 = 1;c_2 = 8'b0000_0001;while(c_1)beginc_2 = c_2 << 1;#10;if(c_2 == 8'b0001_0000)c_1 = 0;elsec_1 = 1;endend

-

“for”語句

-

先求表達式1;

-

求解表達式2。若其值為真,則執行 for 語句中指定的內嵌語句,然后執行第3步;若表達式2值為假,則結束循環,轉到第5步;

-

求解表達式3;

-

轉回上面第2步繼續執行;

-

循環結束,執行 for 語句下面的語句。

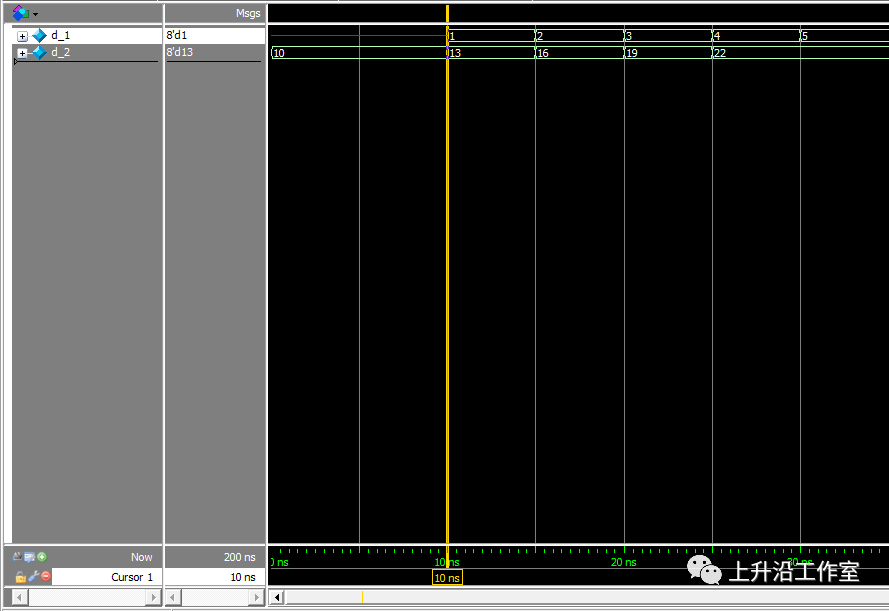

示例代碼如下:

reg [7:0] d_1,d_2;initialbegind_2 = 10;#10;for(d_1=1;d_1<5;d_1=d_1+1)begind_2 = d_2 + 3;#5;endend

02

—

運算符

-

基本算術運算符

-

+ (加法運算符);

-

- (減法運算符);

-

* (加法運算符);

-

/ (除法運算符);

-

% (模運算符或者求余運算符,要求%兩側均為整型數據,結果取第一個操作數的符號位,-10%3的結果是-1,11%-3的結果是2);

-

賦值運算符

-

=;

-

<=;

-

關系運算符

-

> (大于);

-

>= (大于等于);

-

-

<=? ? ? (小于等于);

-

== (等于);

-

!= (不等于);

-

=== (等于,可以比較含有X和Z的操作數,在仿真中用的比較多);

-

!== (不等于,可以比較含有X和Z的操作數,在仿真中用的比較多)。

-

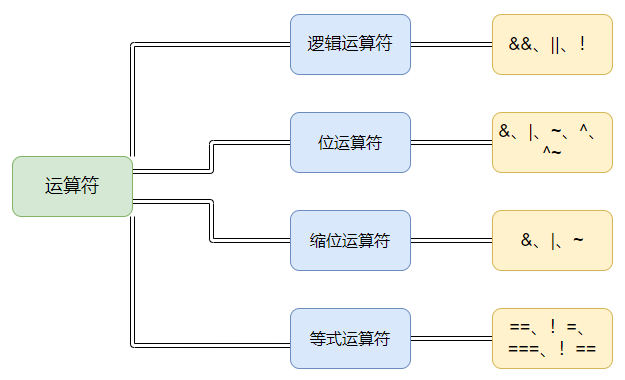

邏輯運算符

-

&& (邏輯與);

-

|| (邏輯或);

-

! (邏輯非)。

-

條件運算符

?:

例子:y=x?a:b(當x為真時,y=a,當x為假時,y=b)。

-

位運算符

位運算符的操作數是幾位,結果也是幾位。

-

~ (取反);

-

& (按位與);

-

| (按位或);

-

^ (按位異或,XOR,相同為0,不同為1);

-

^~ (按位同或,相同為1,不同為0);

-

~& (與非,先按與的操作,然后結果取反);

-

~| (或非,先按或的操作,然后結果取反)。

-

移位運算符

-

<

-

>> (右移,右移一位相當于除以2)。

-

拼接運算符

{s1,s2,s3,s4}:將兩個或者多個信號拼接起來。

-

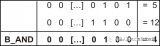

縮減運算符(一元簡約運算符)

縮減運算符對單個操作數進行與、或、非遞推運算,最后的結果是1位的二進制數。具體過程如下:

-

先將操作數的第1位和第2位進行與、或、非運算;

-

運算的結果與第3位進行與、或、非運算;

-

一次類推,知道最后一位。

審核編輯:郭婷reg [3:0] a;reg b;b = &a; 等同于 b = ((a[0]&a[1])&a[2])&a[3]。

-

Verilog

+關注

關注

28文章

1343瀏覽量

109983 -

C語言

+關注

關注

180文章

7598瀏覽量

136184

原文標題:Verilog基礎知識學習筆記(三)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

煉獄傳奇-移位和位拼運算符之戰

求一道MATLAB編程題。要求: 使用循環語句編程,但不能使用數組運算符和sum

Java基礎之Java運算符

Bitwise 邏輯運算符進行設計

python運算符是什么

什么是邏輯運算符

Verilog邏輯設計中的循環語句和運算符

Verilog邏輯設計中的循環語句和運算符

評論