全球數據量仍然處于持續的爆炸式增長當中,不僅現有的應用對數據的生成量快速增加,新的應用領域如人工智能/機器學習(AI/ML)等,也都在不斷生成更多的數據。同時,數據中心也必須要有完善的架構和基礎設施來支持如此龐大數據量的傳輸以及存儲。在中國,數據中心市場整體發展得還是非常迅速的,而且每年都有非常大幅的增長和提升。近期,中國還提出了“東數西算”工程,數據中心的發展迎來政策利好。

隨著數據總量繼續大幅爆炸式增長,數據中心正在采用新的計算模式,如分解式計算(Disaggregated Computing)或者可組合式計算(Composable Computing),這也要求同時保證數據傳輸速率的提升和數據傳輸的安全性。

Rambus在數據中心及其細分市場的收入占比達到75%以上,做為數據中心高速互連方案的芯片及IP供應商,Rambus始終站在技術和市場的前沿。最近,Rambus發布了全新的PCIe 6.0控制器IP。Rambus戰略營銷副總裁Matt Jones,和大中華區總經理蘇雷在媒體交流會中對這項新技術、新品和應用前景進行了詳細的解讀。

PCIe6調制信號重大變化:從NRZ到PAM4

自21世紀初PCIe標準正式創立以來,它就已經成為數據中心和計算應用中芯片間數據傳輸的行業標準。今年1月份,PCIe 6.0的相關規范正式出臺,標志著我們進入PCIe 6.0時代。

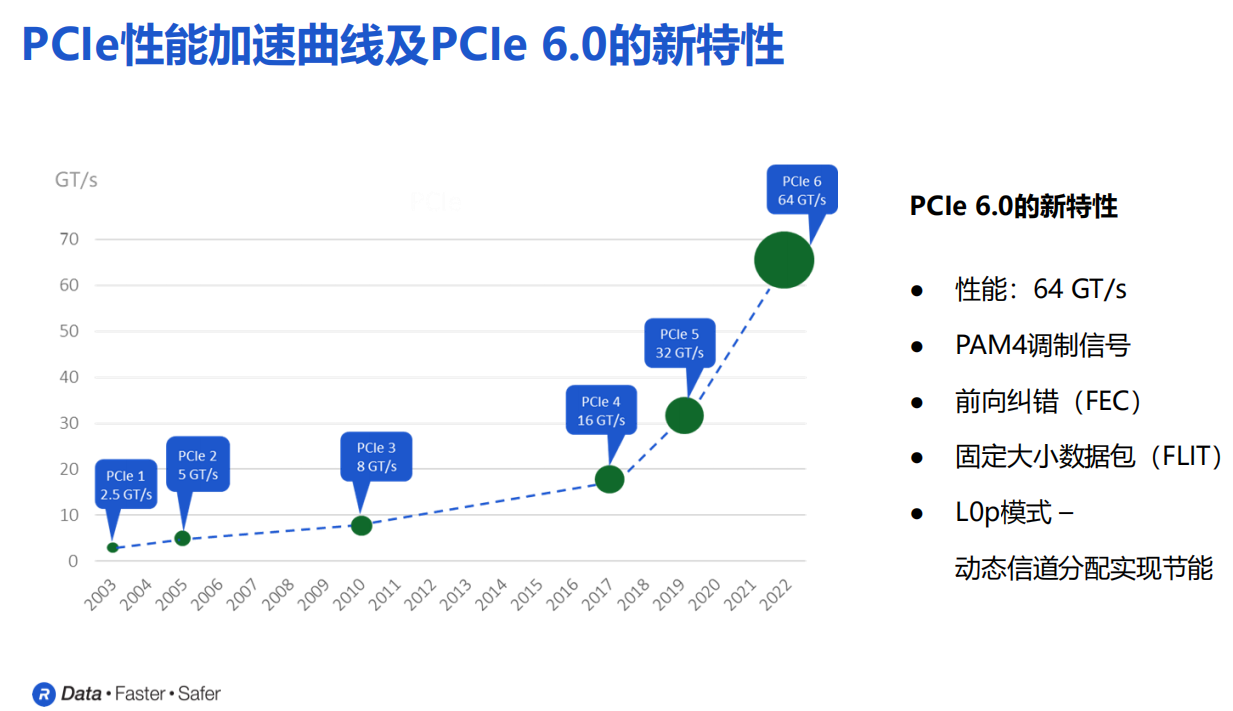

PCIe 每次的技術迭代,數據傳輸速率的性能指標基本上都是翻倍的。PCIe 1.0和2.0時代,理論數據傳輸率大概是2.5和5GT/s,但考慮到具體采用的編碼技術和信號傳導模式,實際的數據傳輸速率大概是2和4GT/s。到現在的PCIe 6.0速率高達64GT/s。

為了更好地在PCIe技術規范之下實現64GT/s的數據傳輸速率,并克服整個通道傳輸長度以及距離的限制,新規范采用了全新的PAM4調制信號,也就是四電平脈沖幅度調制。

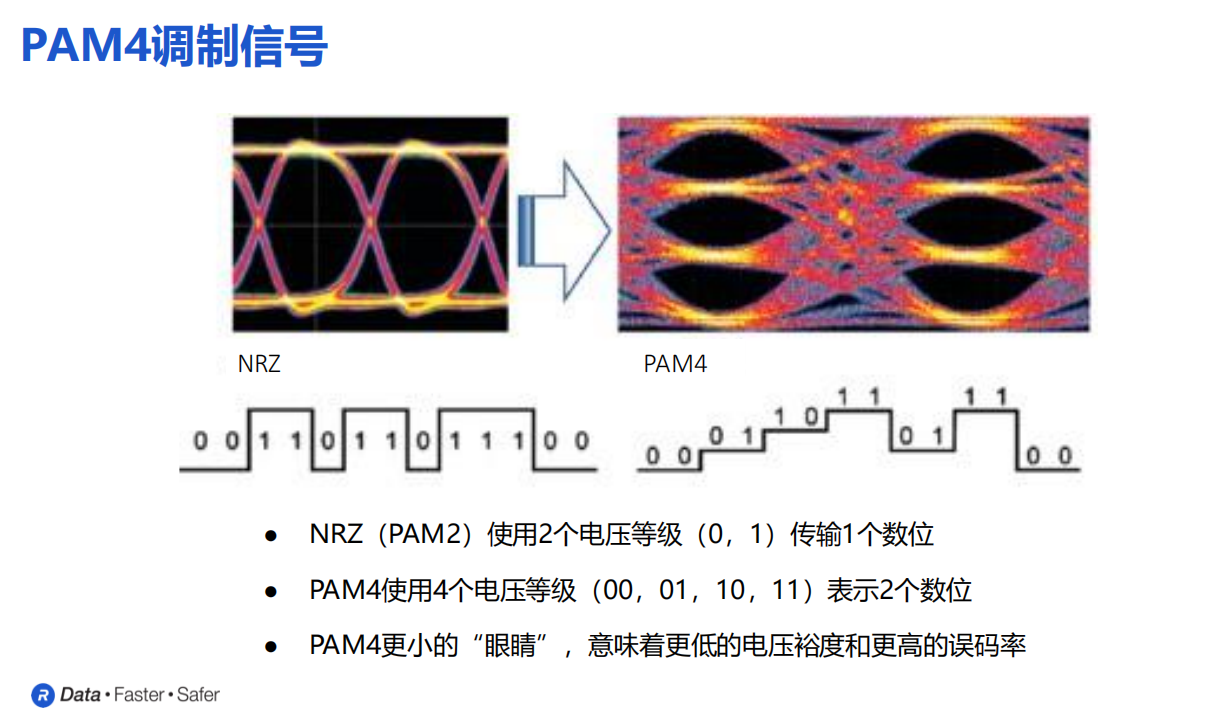

Rambus高管具體分析道,在PCIe 6.0之前,各代PCIe采用的都是NRZ調制信號,即不歸零編碼,它采用0或1兩個電壓等級,每一個時鐘周期只能傳輸1bit的信號。也就是說,它只采用了高低兩種信號電平。因此,相對于PAM4采用的四電平,我們也將NRZ稱作PAM2 。

為了實現高達64GT/s的數據傳輸速率,PCIe 6.0采用PAM4調制信號。通過PAM4,每個時鐘周期的數據傳輸可以達到2bit,而并不僅僅是單bit的數據傳輸。PAM4采用四個不同的電平等級,在每個時鐘周期表達2個數位,從00、01、10再到11,這就意味著在同樣的電壓波動范圍之內和同樣的時鐘周期內,由于PAM4的電壓等級比PAM2高了兩個,即眼圖中黑色的區域“眼睛“這個部分更多、更小了。這種變化帶來了另外兩個重要的影響,即更低的電壓裕度和更高的誤碼率,使得在設備中保證信號完整性成為了一個非常關鍵的難題。

進一步來說,考慮到PAM4要確保PCIe 6.0達到64GT/s數據傳輸速率,需要在保持數據傳輸速率的前提下解決PAM4本身的問題。為此,PCIe6.0采用了前向糾錯技術(FEC)。 FEC本質上是一種算法技術,可以在數據傳輸鏈路中確保所有信號的完整性。

同時,FEC技術的采納還改變了數據流控制單元的情況,要求我們也必須針對數據包本身的大小做出調整和改變。在PCIe6.0之前的幾代規范,包括PCIe5.0、3.0等,采用的是可變大小的數據包;但由于FEC技術的采納,PCIe 6.0必須采用固定大小數據包(FLIT),以更好地保證FEC技術的實現和操作。

數據傳輸速率的上升以及PAM4這項技術本身帶來了另一個問題,即設備的能耗可能會上升,每一比特數據傳輸造成的單位數據能耗也會增加。為了減少整體系統的能耗,PCIe 6.0采用了顛覆式的L0p模式,其本質是通過動態的信道分配,允許將每個通道進行封閉或者打開來實現系統性的節能。

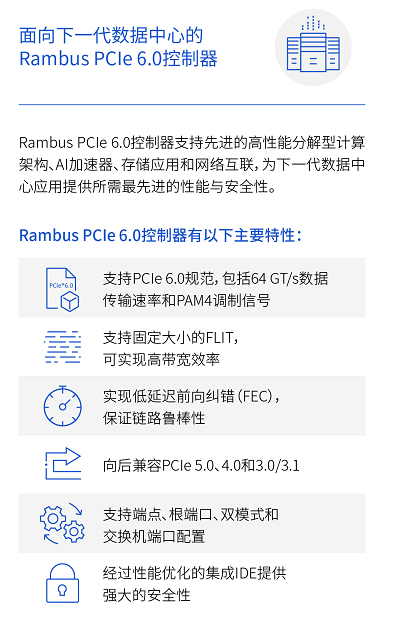

Rambus的PCIe 6.0控制器不僅數據傳輸速率高達64GT/s,更重要的一點是,該控制器還集成了完整性和數據加密(IDE)引擎,可以實現數據在不同PCIe設備的PCIe通路之間的安全傳輸。

Rambus PCIe 6.0控制器在功耗、面積以及延遲上都特別進行了相應的優化,特別在降低能耗方面,以幫助確保PCIe6.0成為數據中心解決方案的一塊關鍵基石,進而推動環保型數據中心的建設,并減少對散熱管理的需求,降低擁有成本。

同時,Rambus的PCIe 6.0控制器非常靈活,可以適用于PCIe端點、根端口、雙模式和交換機端口配置。

與客戶合作推進系統級芯片和PCIe6.0方案,助力“東數西算”工程

現在,Rambus 向中國市場正式發布Rambus PCIe 6.0控制器,同時以超過400個PCIe控制器的成功生產流片為基礎,再次擴大了Rambus在PCI Express IP授權領域的領導地位。

Rambus高管表示,RambusPCIe6.0控制器目前已經可以量產,是以RTL的提供軟性IP,然后將其合成到客戶的設計中。因此它可以跨越許多工藝節點,并具有設計上的靈活性,能夠處理跨許多代工廠解決方案和工藝節點的時序收斂和集成,不必局限于任何一個制造代工廠或工藝節點。我們已與領先的客戶合作,使用我們的控制器產品開發系統級芯片和PCIe6.0解決方案。這些解決方案的開發和制造周期大概需要3年,也就是2025年左右進入市場。

去年,Rambus發布CXL內存互連計劃,推出了一系列面向數據中心的新的解決方案,目標是讓數據中心架構進入下一個更高效節能的新階段。Rambus高管表示,未來,CXL會推出池化的概念,也將幫助下一代的數據中心變得更加高效化、節能化,以一種新的架構來迎合數據中心的未來需求,可以很好地滿足“東數西算”的部分需求。因此,Rambus也正在和數據中心領域的一些合作伙伴緊密聯系,看如何用以Rambus的產品賦能其數據中心建設。

緊跟PCIe技術迭代,不斷強化數據中心業務

PCIe從PCIe 5.0到6.0的迭代,以及從NRZ到PAM4的變化,是PCIe規范在物理實現方面的一個重大變化。Rambus高管認為,從NRZ到PAM4的巨大變化一定程度上為PCIe技術未來的發展留下了足夠的空間和期待。比如說下一代PCIe標準,暫時稱呼為PCIe 7.0,基于歷史期望,數據速率還需要繼續翻倍,因此PCIe 6.0的PAM4可能會升級為“PAM6/PAM8”,以在未來獲得更高的數據傳輸速率。

當然,畢竟現在PCIe 6.0還剛剛發布,處于正在走向成熟的階段,對PCIe 7.0還沒有完整的定義和規劃。等到PCIe7.0真的到來,相信我們會對它的數據傳輸速率等都會有更加全面的了解。

著眼于現在,PCIe 6.0控制器將成為ASIC供應商的重要基石,幫助他們為AI/ML加速器建立起一個更加完善的PCI生態系統,并支持不斷發展的數據中心中PCIe 6.0級數據傳輸的基礎設施。

-

IP

+關注

關注

5文章

1661瀏覽量

149337 -

Rambus

+關注

關注

0文章

59瀏覽量

18789

發布評論請先 登錄

相關推薦

IaaS+on+DPU(IoD)+下一代高性能算力底座技術白皮書

華為云華東(蕪湖)數據中心正式開服

東盟能源和華為主編的《東盟下一代數據中心建設白皮書》正式發布

港燈打造了面向未來的下一代電力數據中心網絡

芯原推出面向下一代數據中心的全新VC9800系列IP

平臺賦能,算力共建,智貫東西 “2023 英特爾算力大會暨東數西算大會”成功舉辦

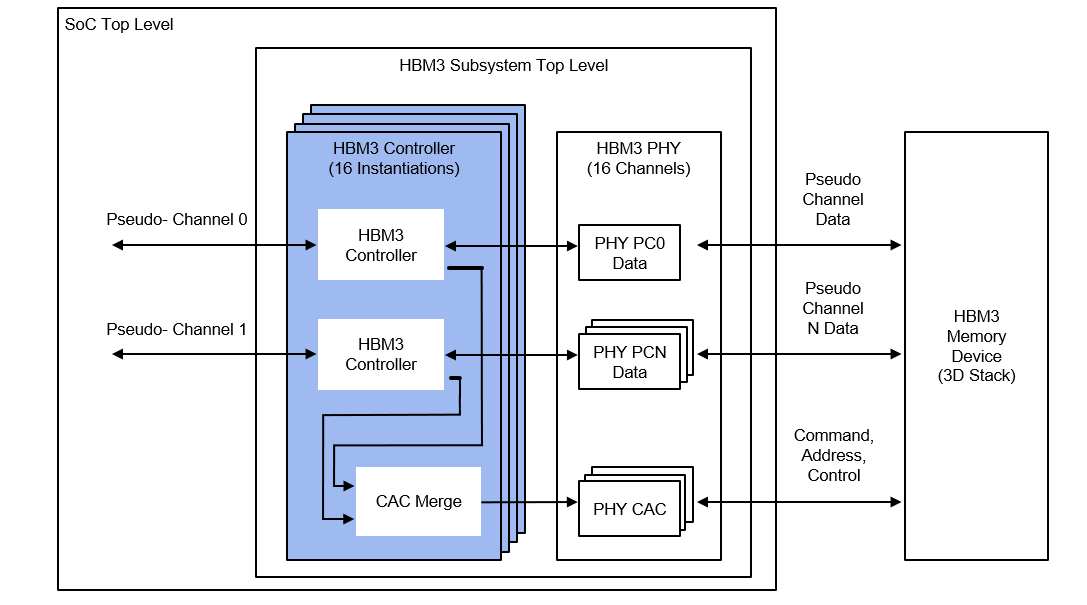

Rambus通過9.6 Gbps HBM3內存控制器IP大幅提升AI性能

Rambus通過9.6 Gbps HBM3內存控制器IP大幅提升AI性能

助力“東數西算”,Rambus PCIe 6.0控制器IP,搶先布局下一代數據中心

助力“東數西算”,Rambus PCIe 6.0控制器IP,搶先布局下一代數據中心

評論