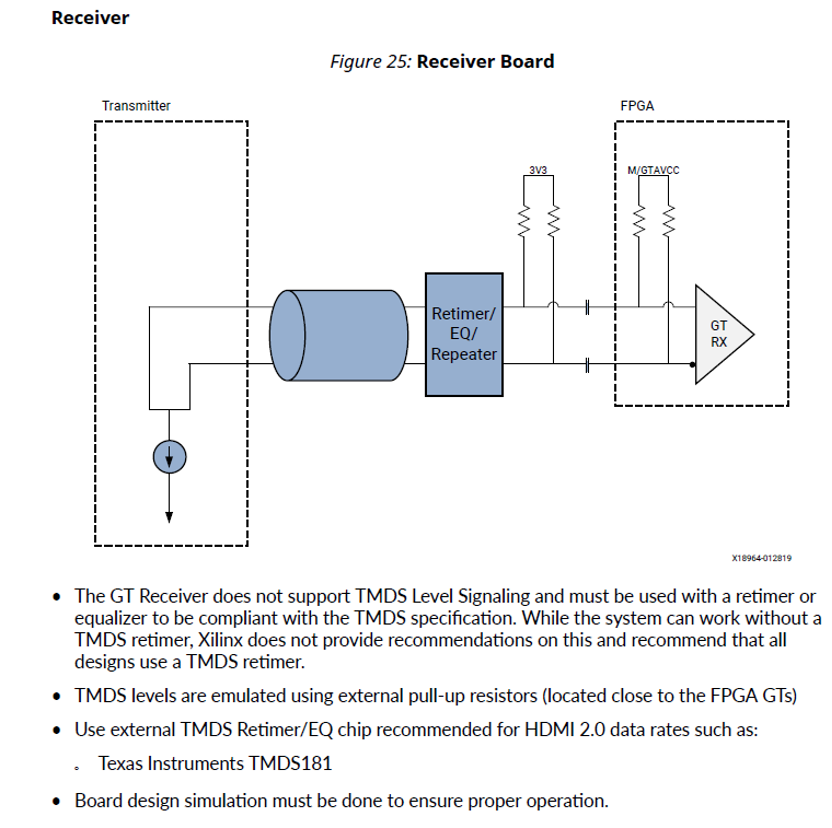

Xilinx HDMI 1.4/2.0 RX的解決方案是由HDMI 1.4/2.0 Receiver Subsystem IP作為MAC和Video PHY Controller IP作為PHY組成,在板上,由外部電阻來實現TMDS level shifter,還有TMDS181作為retimer。

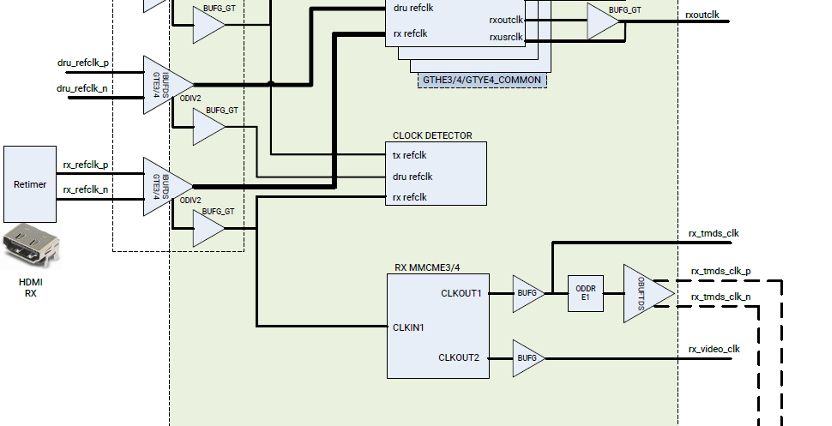

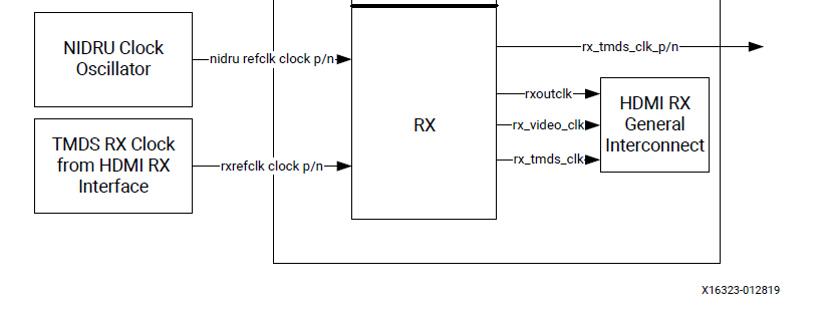

在PHY層,也就是Video PHY Controller IP,常見的問題是如果需要支持HDMI 2.0 RX所有的分辨率PHY需要哪些時鐘。以GTH為例,見下圖,對于RX而言,PHY需要兩個參考時鐘,分別是RX reference clock,DRU reference clock,才能支持所有的分辨率。

注意,RX refclk是來自HDMI RX source, 實際上來自于前面介紹的retimer,見下圖,同tx refclk一樣,RX refclk的頻率也是取決于輸入video的分辨率,最大不超過297MHz,因此,在XDC的約束文件里,可以對RX refclk的clock period約束為297MHz。與TX不同的是,RX refclk不需要rx_refclk_rdy,因為這個clock是來自于cable的。

DRU refclk來自于外部clock generator,而且DRU reclk是固定的頻率,見下圖:

HDMI RX的初始化也分為VPHY的初始化和HDMI RX的初始化。

VPHY的初始化流程圖:

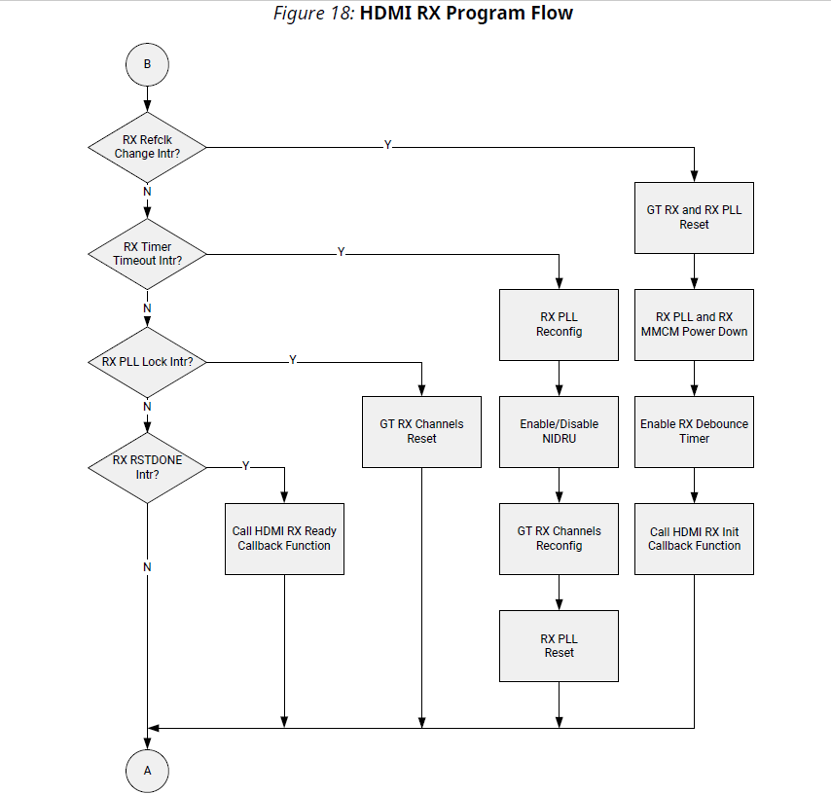

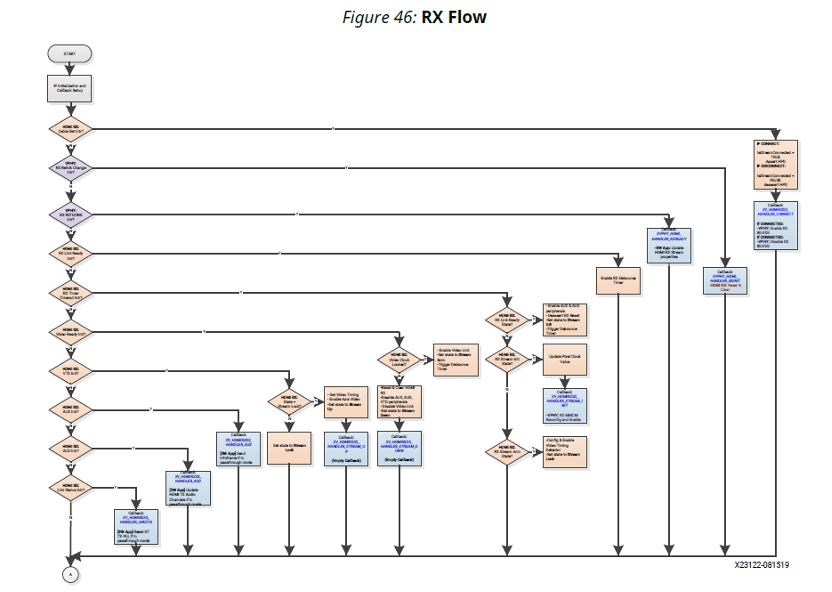

HDMI RX初始化流程圖(詳細內容, 請見文章最后的PG236鏈接):

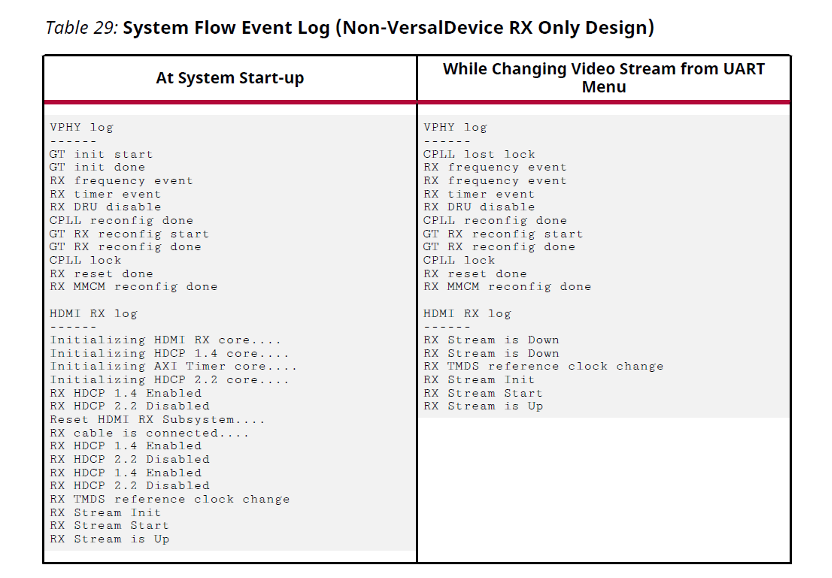

常見的問題是VPHY或者HDMI RX初始化有問題,這時候可以打印VPHY和HDMI RX的log,和好的log作對比,看問題出在哪個環節。

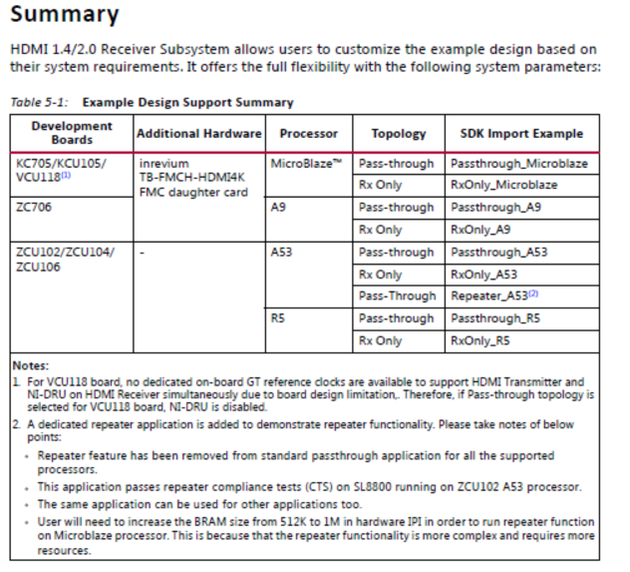

另外HDMI 1.4/2.0 RX Subsystem IP提供了很多基于Xilinx開發板的demo,用戶在做HDMI的設計或者debug問題,參考demo是一個有效的手段,詳細內容,見PG236 -> ch6 example design。

PG236:

https://china.xilinx.com/content/dam/xilinx/support/documentation/ip_documentation/v_hdmi_rx_ss/v3_2/pg236-v-hdmi-rx-ss.pdf

審核編輯 :李倩

-

電阻

+關注

關注

86文章

5476瀏覽量

171695 -

PHY

+關注

關注

2文章

301瀏覽量

51700

原文標題:開發者分享|HDMI_1.4_2.0_RX_Subsystem_IP介紹和基礎debug建議

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HDMI1.4/2.0接口靜電保護方案設計

LT8631UX HDMI2.0 / 1.4自適應均衡RX輸入和預加重TX輸出

HDMI2.0/1.4規格的4 to 2交換機,支持數字音頻輸出,最大6Gbps高速數據速率

Xilinx的HDMI 1.4Tx/Rx和HDMI 2.0Tx/Rx的IP內核介紹

如何分辨HDMI 2.0和HDMI 1.4接口

LT8641UXE HDMI2.0/1.4交換機的特性說明

LT86204UX HDMI2.0/1.4交換機功能說明

龍訊最新推出LT86404UX HDMI2.0/1.4交換機具有符合HDMI2.0/1.4規格的4:4開關

HDMI_1.4_2.0_RX_Subsystem_IP介紹和基礎debug建議

HDMI_1.4_2.0_RX_Subsystem_IP介紹和基礎debug建議

評論