要制造出符合您預期的產品,您必須與電路板制造商或制造商共享準確的疊層定義。準確的疊層定義對于從設計中獲得最佳性能至關重要。層堆疊也會影響串擾和凈阻抗;而這兩個因素反過來又會驅動 PCB 的功能性能。

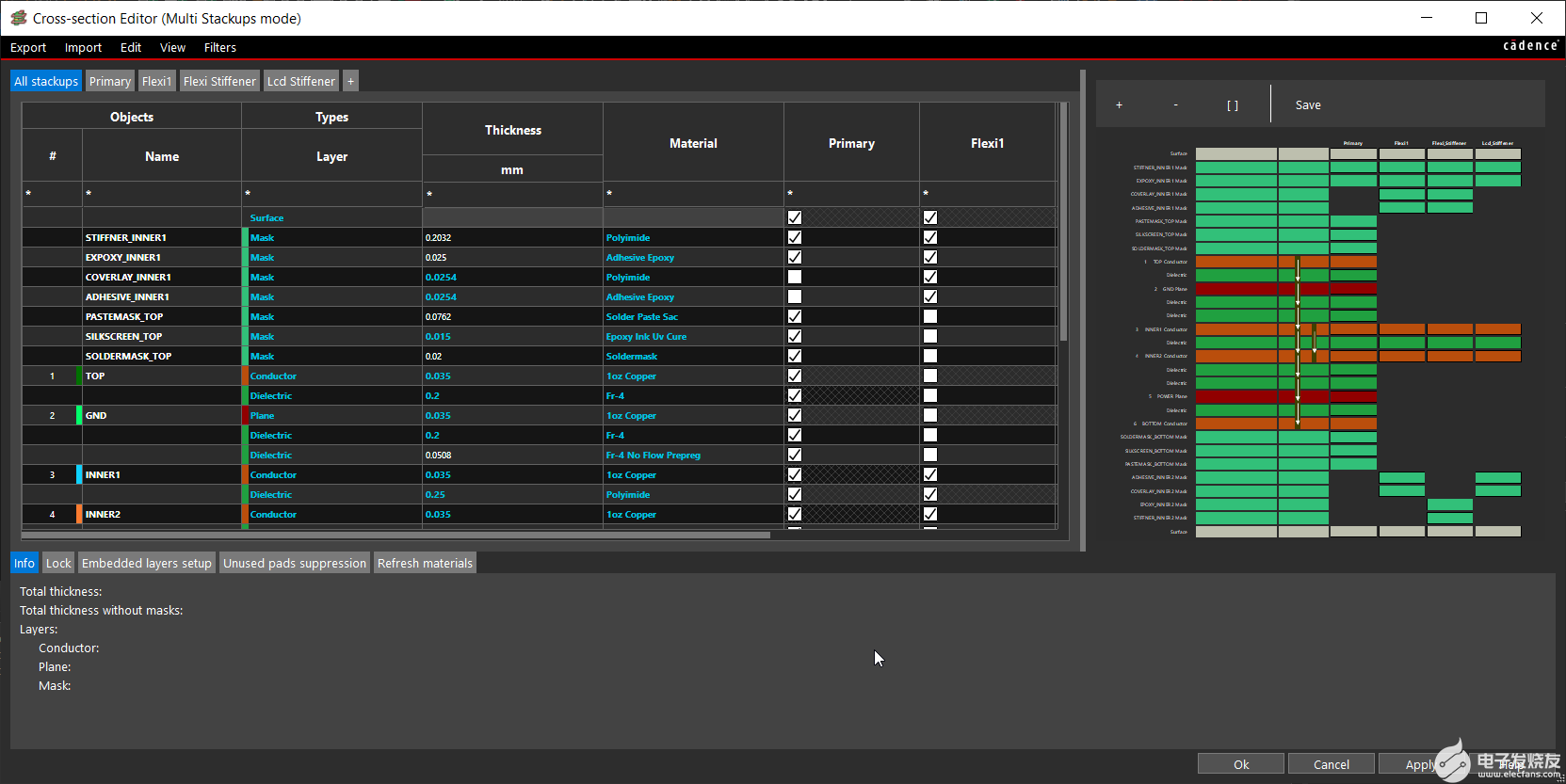

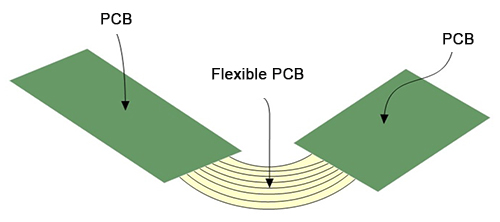

Allegro ?布局編輯器 – Allegro ? PCB Editor 和 Allegro ? Package Designer Plus – 包括基于電子表格的用戶界面、橫截面編輯器,可幫助您使用關鍵層信息定義準確的層堆疊,以避免任何電子元件設計失敗。層信息包括層數和用于疊層中的層的材料,以及每層的屬性,例如設計阻抗、層厚度和電導率。使用橫截面編輯器,為剛性和柔性板設計定義電介質和導體層以及外部掩模層比以往任何時候都容易。

這篇博文展示了如何為剛性和柔性 PCB 定義多層堆疊,并使用橫截面編輯器為設計指定層信息。

橫截面編輯器

您可以在橫截面編輯器中定義層堆疊并指定每個層的屬性。您可以使用設置-橫截面菜單命令從任何 Allegro 布局編輯器訪問橫截面編輯器。或者,使用xsection命令。

橫截面編輯器顯示活動設計的有序層以及每個層的屬性,例如其厚度、材料、導電率等。

單疊層和多層疊層

橫截面編輯器同時支持單疊層和多層疊層。單疊層模式是默認模式,其中所有電層(例如導體、平面和電介質)都顯示在Primary選項卡中。

除了對電氣層的多層疊定義支持外,此模式還支持非電氣層的多層疊定義,例如阻焊層和覆蓋層,可用于剛性、柔性或剛柔性 PCB。您可以使用View – Multi Stackups mode菜單命令啟用多層堆疊模式。

我可以在橫截面編輯器中指定哪些圖層信息?

要為 PCB 設計定義有用的層堆疊,首先了解可以使用橫截面編輯器添加哪些層信息非常重要。您可以指定的一些關鍵層信息包括層材料、厚度、介電常數、損耗角正切等。隨著本文的推進,我們將進行更多探索。

層序

從信號完整性的角度來看,層排序是決定 PCB 性能的眾多因素之一。這也是減少PCB上形成的環路輻射的有效方法。疊層中的層數由要路由的信號數量和工作頻率決定。

堆疊不良的設計可能會導致失敗。例如,如果在多層設計中電源層和接地層之間的間隔很大,則相鄰電源層和接地層之間的層間電容將不足,并且可能無法提供足夠的去耦。可以通過在信號層和平面層之間提供緊密耦合來補償層間電容的損失。在平面層之間添加更多層并將信號層放置在靠近平面層的位置,增加了層間電容并因此提高了 EMC 性能。

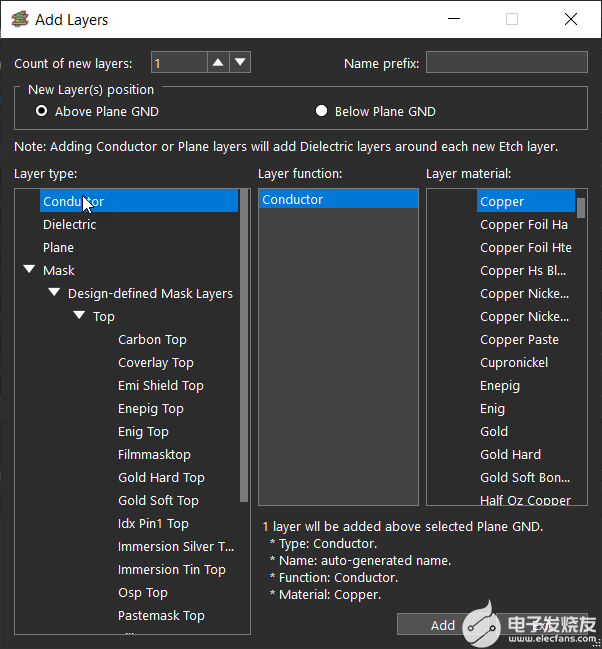

添加圖層

要將圖層添加到疊層:

層材料

添加導體和介電層后,下一步是在橫截面編輯器的材料列中選擇用于導體、平面或介電層的材料。最常用的材料是銅和FR4。

Cadence 提供了一個全局默認材料文件,materials.dat,其中包含典型的工業制造材料。您可以編輯材料文件以添加或刪除材料。此文件位于:\share\pcb\text。

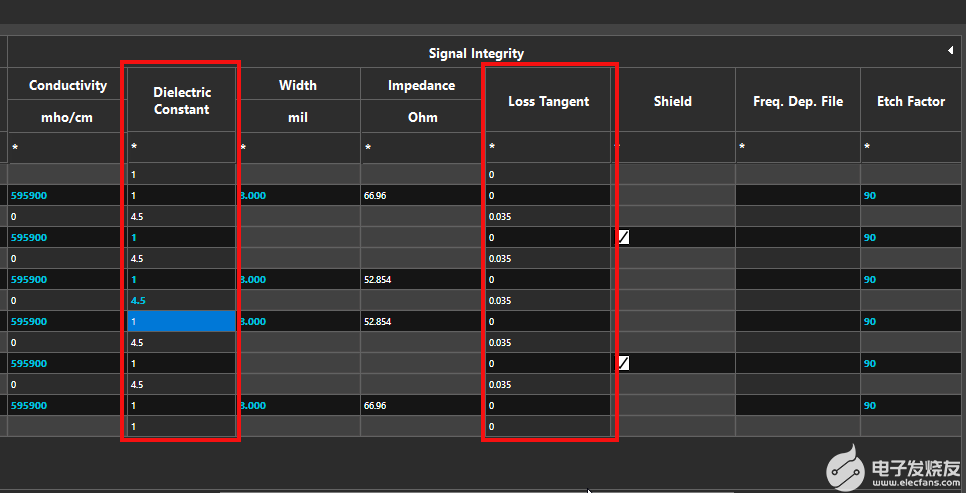

介電常數和損耗角正切

PCB 材料的介電常數和損耗角正切特性也會影響設計的電氣性能。您可以在介電常數和損耗角正切列中指定這些屬性。

如果在這些列中指定了任何不正確的值,Allegro 布局編輯器會在命令窗口中顯示錯誤消息。

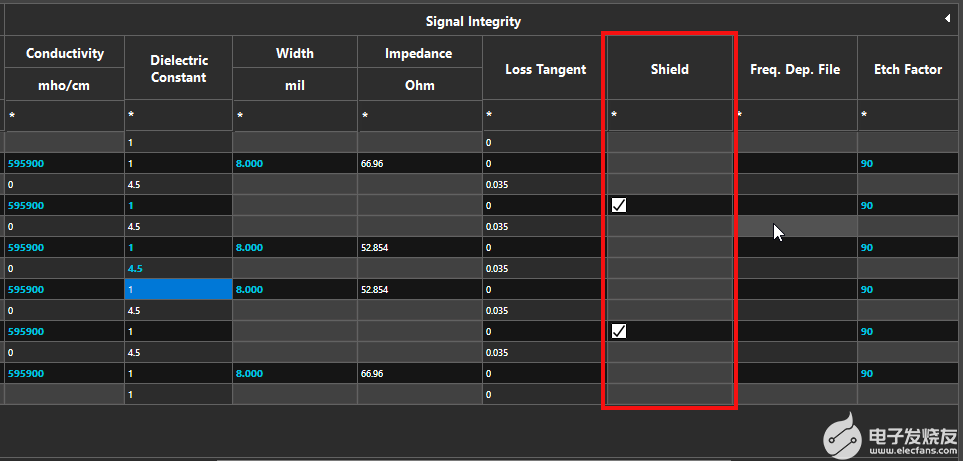

屏蔽

屏蔽可防止相鄰層上的電信號相互影響。您可以為平面層選中Shield列中的復選框,以便模擬器將該層視為傳輸線的偽無限參考平面。

阻抗

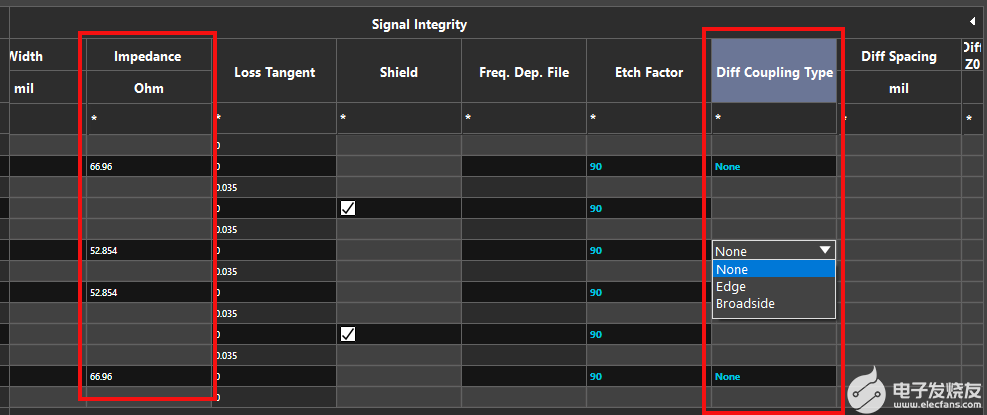

可以在阻抗列中指定跡線的阻抗。阻抗取決于材料的介電常數值、走線的厚度和寬度以及與參考平面的距離。

您還可以在橫截面編輯器中查看微帶線和帶狀線的單端和差分阻抗。您可以在Diff Coupling Type列中選擇邊緣耦合或寬邊耦合差分阻抗。

蝕刻因子

蝕刻系數列允許您在每個導體和平面層上設置蝕刻的蝕刻系數角度。如果您輸入的值超出有效范圍,橫截面編輯器會顯示警告并忽略新值。

負片

對于整個平面為實心填充的電源層和地平面層,您可以選中Negative Artwork列中的復選框以減小圖稿文件大小和膠片的打印時間。這會在反向圖像中創建藝術品,其中空隙是實心填充的,銅區域顯示為透明。

結論

隨著層數的增加,與電路板制造設施共享準確的疊層定義變得比以往任何時候都更加重要。在橫截面編輯器中指定層堆疊信息可確保您的設計在構造上是正確的,并且不易發生故障。此信息也可以傳遞到 MCAD 系統,從而消除不必要的 MCAD-ECAD 迭代。

-

pcb

+關注

關注

4280文章

22690瀏覽量

392035 -

電路板

+關注

關注

140文章

4762瀏覽量

95570 -

PCB設計

+關注

關注

394文章

4629瀏覽量

84279 -

柔性電路板

+關注

關注

12文章

109瀏覽量

29394 -

allegro

+關注

關注

42文章

640瀏覽量

144444

發布評論請先 登錄

相關推薦

Allegro PCB設計技巧 為多層剛性和柔性堆疊指定層信息

Allegro PCB設計技巧 為多層剛性和柔性堆疊指定層信息

評論