最近兩周,Chiplet相關新聞的頻出。NVIDIA宣布了一款令人興奮的新型NVLink-C2C互連,用于其CPU、DPU、GPU以及與其合作伙伴和客戶的其他集成之間的緊密耦合鏈路。UCIe(Universal Chiplet Interconnect Express)成立,其宗旨是為封裝創新構建生態系統。在本博客中,我們將關注推動Chiplet采用的關鍵用例,以及Arm如何幫助推動成功的Chiplet生態系統。

Chiplets在許多不同的應用中已經存在多年,但我們正處于一個轉折點。Chiplets可以通過擴展超過reticle限制來提高性能,同時仍然提供管理芯片成本的能力。摩爾定律的放緩已經在業界討論了一段時間。雖然先進制程(5nm及以下)為邏輯提供了好處,但片上系統(SoC)的IO和內存組件的擴展速度顯著放緩,這意味著成本更高,效益更低。

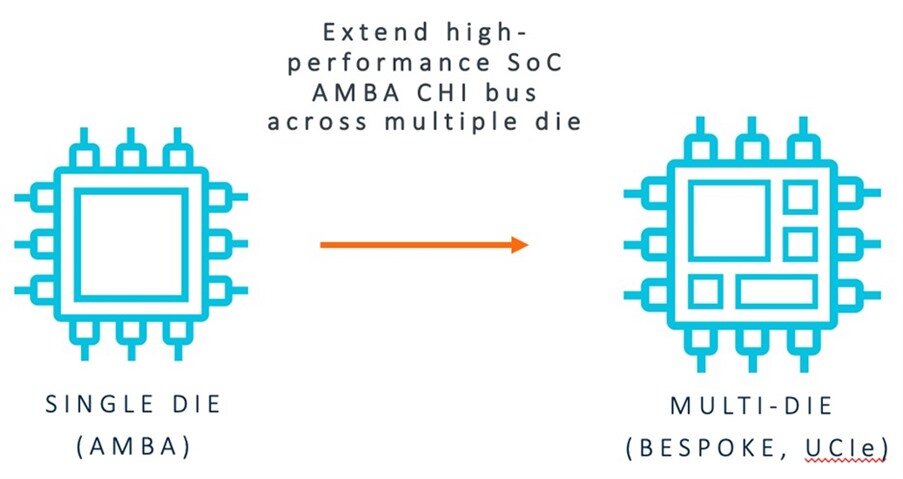

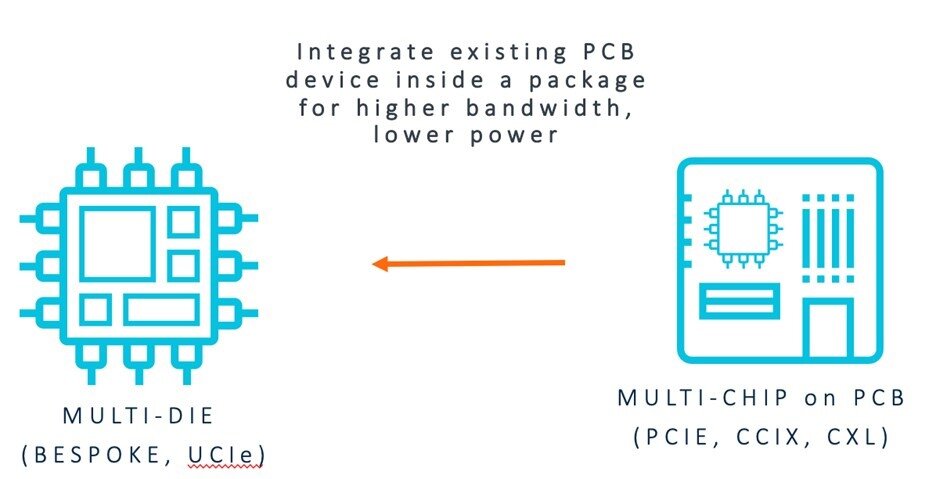

一個全面的芯片解決方案包括許多不同的元素,從協議到物理層,再到封裝技術。如今,SoC設計者正在將不同的組件組合在一起,以實現其性能、成本和系統組成目標。各種各樣的解決方案可能會導致混亂。對于芯片集成,有兩種常見的觀點。

第一種觀點是將傳統的單片SoC分解成多個更小的組件。這種方法有一個通用的協議、內存、調試和安全模型。SoC設計者努力使片上總線盡可能無縫地擴展到多芯片。

第二種觀點著眼于通過行業標準的板級互連將現有的板級組件連接起來,并將其集成到封裝中,這是因為它具有更好的帶寬和能效。SoC設計者努力盡可能多地使用現有框架,并為其需求提供最佳的片間物理層和封裝解決方案。

AMBA CHI多芯片解決方案

Arm建立了AMBA-CHI(Coherent Hub Interface),為高度可擴展、多核、異構的SOC提供片上通信。由于其可擴展性,CHI也非常適合于完整的多芯片接口規范中的協議層。CHI與CCIX和UCII等行業標準兼容,同時還提供了NVIDIA NVLIK-C2C互連等定制解決方案。使用CHI的好處包括:

。為多核擴展(CPU-CPU)實現對稱一致性

。為高級異構工作負載(即CPU-GPU)實現對稱一致性

。支持公共內存和安全模型

。消除協議橋接以獲得更優化的鏈路

NVIDIA NVLink-C2C通過其NVIDIA Grace CPU超級芯片和NVIDIA Hopper GPU提供NVIDIA CPU、GPU和DPU之間的連接。多芯片解決方案將CHI的優勢與利用NVIDIA世界級SerDes和link技術的最佳物理層和封裝解決方案相結合。這使得一類新的可組合集成產品能夠通過芯片構建,無論最終SoC是針對超級計算還是針對高級異構CPU-GPU工作負載。

UCIe:Chiplets的開放生態系統

基于Chiplets的處理器需要提高性能和降低成本,這一點是眾所周知的。但直到最近,人們還沒有就如何在特定于供應商的實現之外利用芯片體系結構的好處達成一致。Universal Chiplet Interconnect Express(UCIe)標準就是為了滿足這一需求而開發的。UCIe將半導體廠商、封裝產商、IP供應商、晶圓代工廠商和云服務提供商的行業領導者聚集在一起,推動一個新的開放式芯片生態系統。UCIe 1.0規范提供了完整的標準化芯片間互連,包括物理層、協議棧、軟件模型和合規性測試。這使得最終用戶能夠混合和匹配來自多供應商生態系統的芯片組件,以進行SoC構建。

UCIe協議層利用PCIe和CXL將傳統的片外設備與任何計算體系結構集成。此外,UCIe還設計了通過流媒體協議接口插入其他協議(如AMBA-CHI)的能力,允許SoC產品在協議方面具有靈活性。

有關UCIe技術和會員資格的更多信息,請訪問UCIe網站。https://www.uciexpress.org/

Chiplets的未來

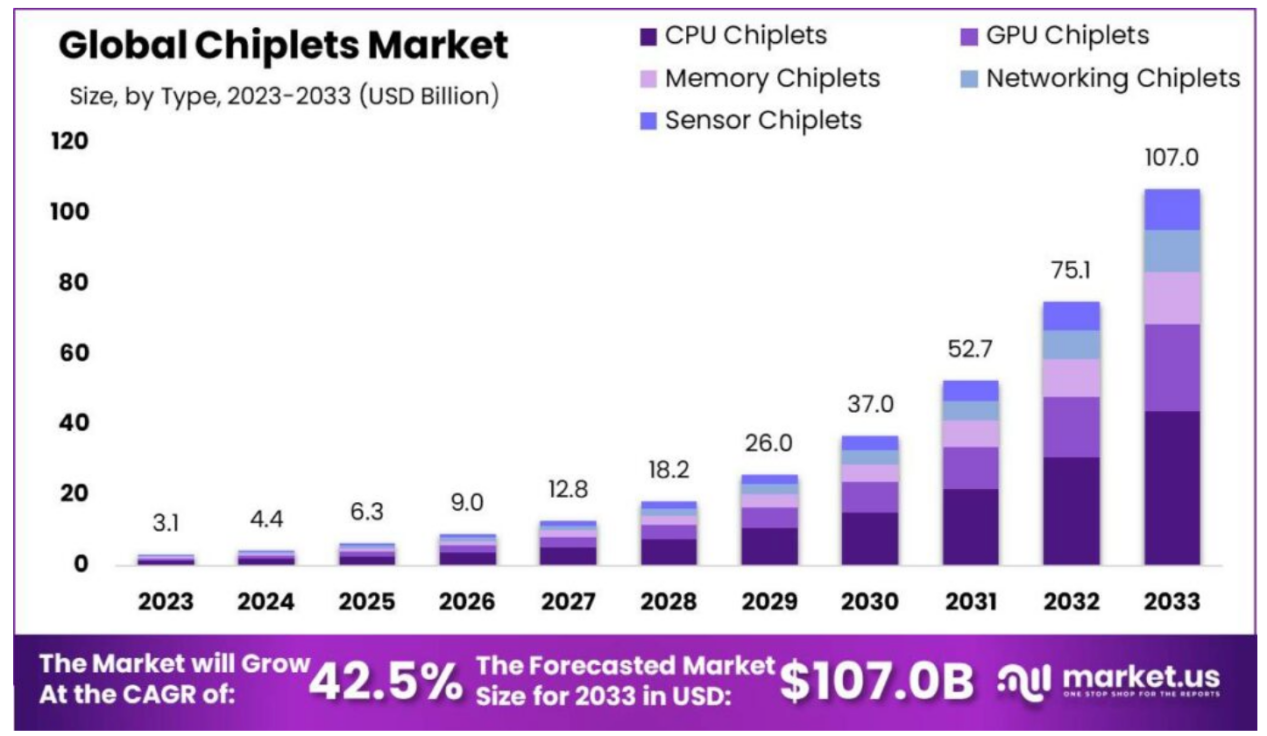

唯一可以確定的是,在未來十年中,Chiplets的采用率將大幅增長。在整個行業中,創新和標準化方面的持續投資將轉化為更高的性能、更低的成本和更廣泛的采用。在Arm,我們希望看到一系列定制和標準實現。我們將很高興看到,

-

chiplet

+關注

關注

6文章

419瀏覽量

12561

發布評論請先 登錄

相關推薦

何小鵬宣布未來十年愿景,加速全球化AI汽車布局

沃達豐與谷歌深化十年戰略合作

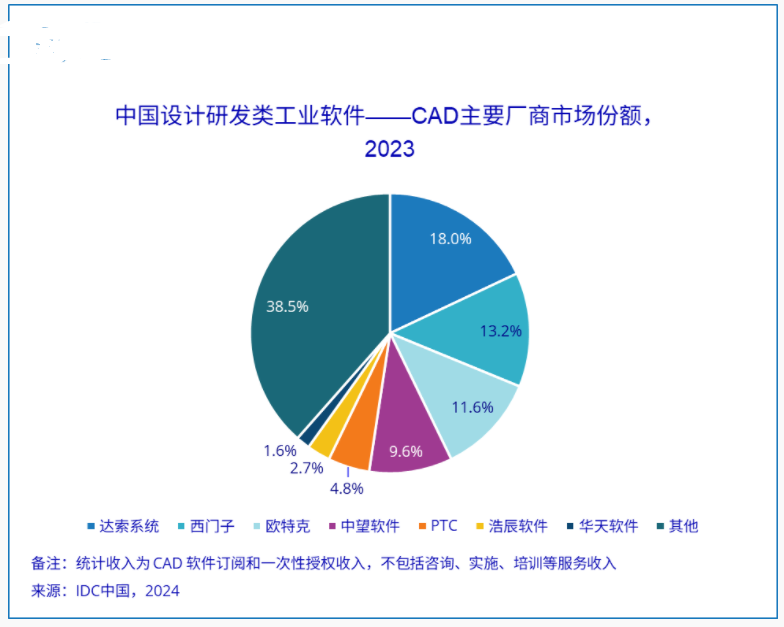

IDC報告:2023年中國CAD市場年增長率達12.8%,展現強勁增長動力

哪種嵌入式處理器架構將引領未來十年的發展?

亞馬遜豪擲千億美元,未來十年加速數據中心建設

聯發科談未來十年的戰略布局

RISC-V在服務器方面應用與發展前景

RISC-V在服務器方面的應用與發展前景如何?剛畢業的學生才開始學來的及嗎?

Redmi新十年產品定位:Turbo系列重塑中端性能格局

持續突破,中微公司超過十年平均年營收增長率超過35%

跨周期,創未來!華秋喜獲中國產業互聯網十周年-杰出企業

跨周期,創未來!華秋喜獲中國產業互聯網十周年-杰出企業

在未來十年中,Chiplets的采用率將大幅增長

在未來十年中,Chiplets的采用率將大幅增長

評論