在5G PA設計和應用中,有一個名詞經(jīng)常被大家提及:記憶效應(Memory Effect)。

PA怎么還會有“記憶”?記憶效應有什么影響,又要怎么規(guī)避?

帶著以上問題,本文對PA的“記憶效應”做一個討論

PA的“記憶效應”

什么是PA的“記憶效應”?

記憶效應是指器件的特性隨時間變化而發(fā)生變化的現(xiàn)象。器件特性隨時間變化,當前時間的特性受上一時間狀態(tài)的影響,就好像器件帶有“記憶”一樣,所以這種特性被稱作“記憶效應”。

對于PA電路來說,記憶效應反應出來的現(xiàn)象是:在同樣的輸入功率下,PA的增益、延時等特性在不同時刻表現(xiàn)不同。

PA一旦表現(xiàn)出強的記憶效應,線性度將會受到明顯影響,出現(xiàn)寬帶線性度惡化、左右ACLR不平現(xiàn)象,還會影響預失真(DPD或APD,數(shù)字預失真或模擬預失真)電路的工作 [1]。在PA設計和使用中,記憶效應需要盡量規(guī)避。

PA記憶效應的識別

方法一:觀測AM/AM、AM/PM

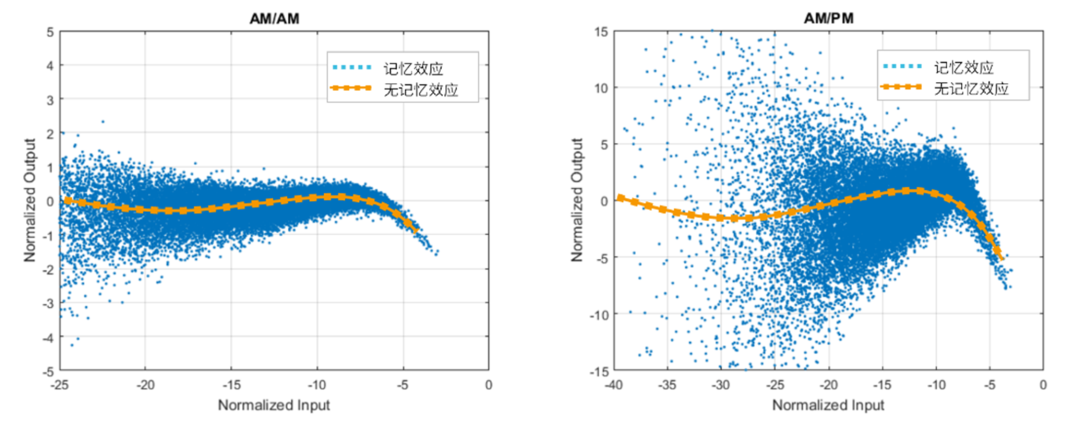

在PA輸入端加入輸入信號,觀察PA的輸出信號,將此時放大器的增益、相位與輸入信號逐點一一對應起來,就得到不同功率下的AM/AM、AM/PM特性曲線。觀測AM/AM、AM/PM是識別記憶效應的最主要方法。

未發(fā)生記憶效應時,AM/AM、AM/PM曲線為一條平滑曲線,代表同樣輸入功率時不同時刻PA的特性保持相同。發(fā)生記憶效應時,曲線表現(xiàn)出一組發(fā)散分布的點,點的分散的離散與否代表了記憶效應的強弱。如果AM/AM、AM/PM曲線表現(xiàn)分散,表示對于一個同樣的輸入功率,PA有不同的增益、相位變化。PA的狀態(tài)不止以此時刻的輸入有關(guān),還與其他時刻的狀態(tài)有關(guān),即PA表現(xiàn)出了“記憶效應”。

圖:帶有記憶效應的PA特性

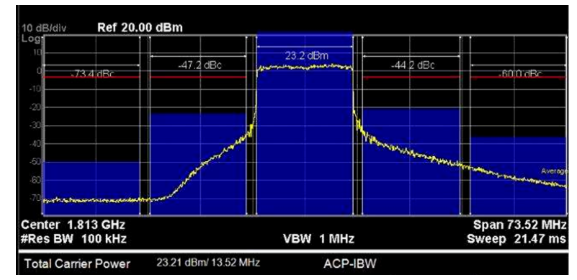

方法二:寬帶ACLR的惡化或不對稱

另外一個識別記憶效應的方法是觀察ACLR隨信號帶寬的變化。如果觀察到信號帶寬變寬時ACLR出現(xiàn)快速惡化,或者開始出現(xiàn)明顯的左右不對稱時,很有可能是發(fā)生了記憶效應[2]。

圖:典型的PA左右ACLR不對稱現(xiàn)象

ACLR不對稱的產(chǎn)生也對測試造成較大困擾,當左右ACLR差別較大時,數(shù)據(jù)的準確記錄都成問題。當發(fā)生嚴重左右不對稱現(xiàn)象時,需要停下來檢查PA是否發(fā)生了記憶效應。

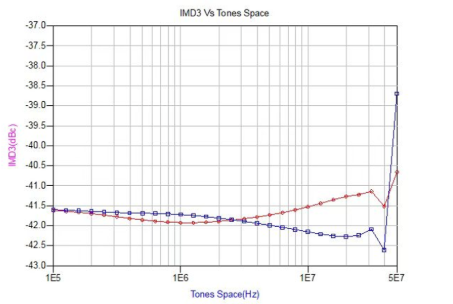

方法三:寬帶雙音信號IMD3惡化或不對稱

與觀測寬帶ACLR是否惡化方法類似,還可以采用觀察寬帶雙音信號(Two tone)的IMD3是否出現(xiàn)記憶效應。

采用雙音對PA進行激勵,并將雙音信號的間距逐漸由小變大,測試雙音信號的IMD3。如果隨著雙音信號的間隔變大,IMD3出現(xiàn)惡化或左右不對稱,則代表PA開始出現(xiàn)記憶效應。如下圖所示測試,當信號間隔大于10MHz時,PA記憶效應開始顯現(xiàn)。

圖:采用雙音測試法識別PA記憶效應

PA記憶效應的產(chǎn)生與規(guī)避

在對PA記憶效應的分析中,一般認為是輸入信號中隨時間變化的包絡引起了PA特性的變化,造成PA不同時間的響應不同。為何輸入信號會有包絡呢?包絡又是如何進一步引起PA特性變化?

4G/5G信號的包絡

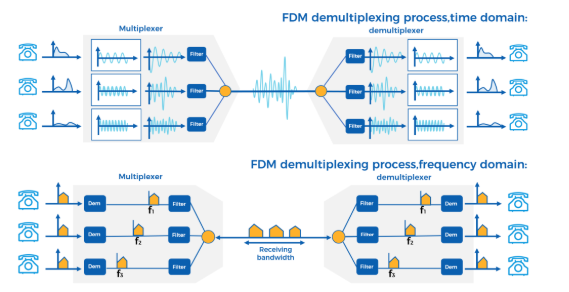

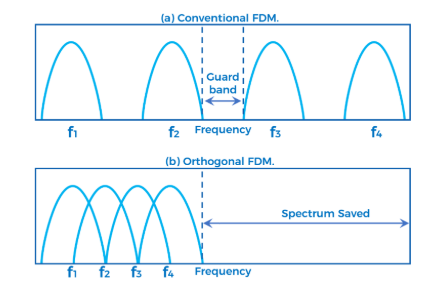

4G/5G系統(tǒng)中所使用的調(diào)制方式是OFDM(Orthogonal Frequency Division Modulation,正交頻分復用)調(diào)制,OFDM是一種特殊的FDM(Frequency Division Multiplex,頻分復用)調(diào)制方式。

FDM是無線通信中的重要復用技術(shù),是指將傳輸信號調(diào)制到不同頻率的多載波上,再進行空間傳輸。與單一頻率的單載波信號相比,F(xiàn)DM可以有效增加帶寬,提升傳輸速率,并且可以增強信號抗干擾能力,在無線通信系統(tǒng)中得到廣泛應用。下圖為FDM系統(tǒng)的典型實現(xiàn)框圖。

圖:頻分系統(tǒng)的時域及頻域圖示

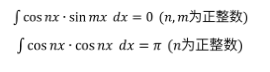

OFDM本質(zhì)也是一種FDM技術(shù),也是利用頻分的方式進行信號的空間復用傳輸。只不過在信號的正交上,并不只是采用如傳統(tǒng)FDM相同的頻分技術(shù),還利用到了一些信號在正交上的特性,OFDM利用到的信號正交特性可由如下積分公示表示,當積分區(qū)間為0~2π時:

如果將cos nx看成一路信號,sin mx或cos nx看成另外一路信號,可以看到相同的信號相乘后積分為π,不同信號相乘后積分為0。所以對于混在一起的不同信號,我們只需要用指定信號和其相乘積分,就可以將有用信號提取出來,實現(xiàn)信號的正交。這就是正交頻分復用的原理。

利用這一特性,OFDM中并不需要像傳統(tǒng)FDM一樣保留較寬的保護帶,而是可以將頻率成倍數(shù)關(guān)系的子載波疊加在一起,就可以完成頻分復用,大大提高了頻譜利用效率。FDM和OFDM的頻域關(guān)系如下圖所示:

圖:FDM與OFDM的頻譜特性 [6]

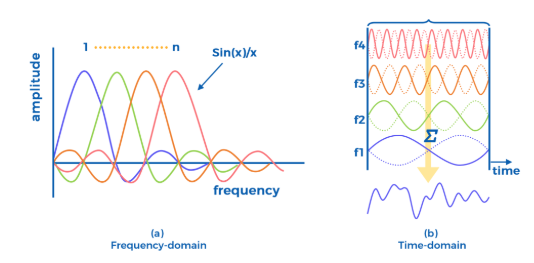

在信號傳輸時,頻域上多個子載波頻分復用進行信號傳輸,時域上這些信號幅度相疊加。如果某一時間點幾個子載波的振幅均為高位,則疊加出現(xiàn)峰值功率,OFMD信號的峰均比:PAPR(Peakto Average Power Ratio)就此出現(xiàn)。

圖:OFDM信號的時域疊加:

形成高峰均比(非恒定幅值)信號

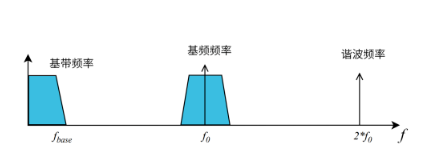

以上OFDM信號的產(chǎn)生均在基頻處發(fā)生,為了將信號在空間傳輸,需要將信號調(diào)制到射頻頻率。一般在無線通信系統(tǒng)中,將攜帶信息的OFDM信號稱為基帶信號,所對應的頻率也稱作基帶頻率。由于射頻信號的調(diào)制和放大經(jīng)常伴有諧波發(fā)生,為了把射頻的信號做區(qū)分,一般將所用來做射頻調(diào)制的頻率稱為基頻頻率,將信號的諧波稱為二次、三次諧波頻率。

圖:基帶頻率、基頻頻率與諧波

(二次諧波為代表)頻率之間的關(guān)系

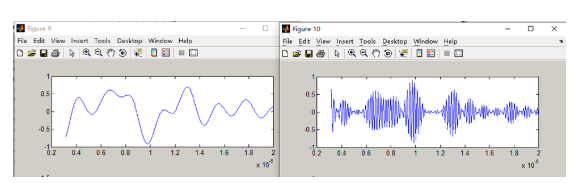

經(jīng)過射頻調(diào)制的OFDM信號波形如下圖所示。

圖:OFDM基帶包絡信號的形成(左)

及射頻基頻信號正交調(diào)制后的波形(右)

由上圖(右)可以看到,OFDM基帶信號被射頻頻率調(diào)制成包絡與原始OFDM信號相同、載波頻率與射頻基頻信號相同的射頻信號。

以上信號將進入功率放大器放大輸出,即進入功率放大器的信號并不是恒包絡信號,而是包絡跟隨OFDM信號變化、帶有峰均比的信號。這就是4G/5G中射頻信號包絡產(chǎn)生的過程。

PA記憶效應的來源

在4G/5G 通信系統(tǒng)中所使用的是非恒定包絡的OFDM信號,如果PA特性隨信號包絡在變化,則會發(fā)生記憶效應。

在PA記憶效應的分析中,一般將包絡信號對PA的影響分為三類 [3],分別是:

電記憶效應;

電熱記憶效應;

半導體器件陷波效應(Semiconductor Trapping Effects)。

電熱記憶效應和半導體器件的陷波效應

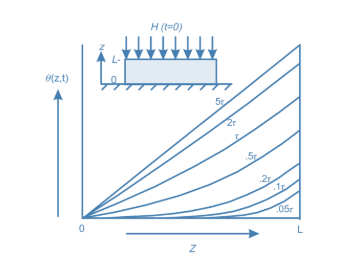

PA是高耗電器件,同時PA特性對溫度敏感。對于PA器件而言,熱擴散與時間相關(guān)。下圖為對PA芯片進行一維等效,在芯片表面加熱源后,芯片各部分位置溫度隨時間變化圖。可以看到,隨著時間的不同,芯片各位置的溫度發(fā)生變化[3]。

圖:PA晶體管芯片溫度分析的一維等效

如果PA的輸入信號帶有包絡,不同包絡信號的幅度將會引起PA溫度的變化,進而引起PA特性的不同,使PA產(chǎn)生記憶效應。通常情況下,電熱記憶效應只與低于1MHz的包絡頻率有關(guān),因此,通常把電熱記憶效應認為是長時記憶效應。

針對于電熱記憶效應,需要對PA進行良好的散熱設計,確保PA產(chǎn)生的熱量可以良好擴散。

半導體的陷波效應(Semiconductor Trapping Effects)是指在半導體器件中表現(xiàn)出來的記憶效應,此種記憶效應與半導體制造工藝相關(guān)。對于半導體陷波記憶效應,設計上可嘗試的方法并不多,需要代工廠在器件上做優(yōu)化和保障。設計中可以采用較為成熟的半導體工藝,確保器件側(cè)無記憶效應問題。

電熱記憶效應

電記憶效應是PA電路記憶效應的主要來源。

在PA設計中,PA能量的來源是直流供電。直流供電需要通過偏置電路加在器件的輸出(集電極或漏極)及輸入(基極或柵極),這些偏置電路需要完成供電功能,并且不能影響到射頻信號傳輸。

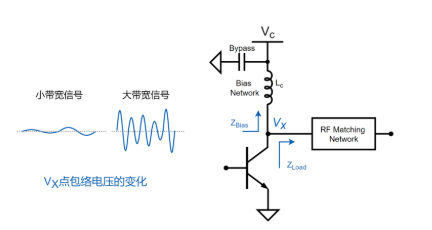

理想情況下,偏置電路需要對射頻信號表現(xiàn)出高阻(射頻信號才不會進入到偏置電路中),同時對其他頻率保持低阻(防止其他頻率出現(xiàn)交流電壓擺幅)。對于射頻信號的包絡頻率來說,由于其與射頻載波信號的二階交調(diào)(IMD2)剛好會落在信號的旁帶,所以射頻信號包絡頻率的阻抗控制尤其重要。如果處理不好,偏置電路將會發(fā)生包絡調(diào)制,引起ACLR惡化。

圖:簡單PA偏置網(wǎng)絡示意圖

以上圖所示簡單偏置電路來理解包絡信號對PA偏置的調(diào)制作用。圖示為簡單共射極放大電路,放大器集電極通過串聯(lián)電感連接至直流供電電源,Bypass電容提供射頻接地,電感LC提供高的射頻阻抗。

如果假設PA工作射頻頻率為2.6GHz,電感LC的感值為3nH,供電電壓為3.4V,電流為500mA。則電感LC可提供的射頻阻抗為ZBias@2.6GHz=163Ω,由于此點的射頻負載阻抗ZLoad@2.6GHz≈3.5Ω,在2.6GHz射頻工作頻率,ZBias遠大于ZLoad,偏置網(wǎng)絡可以提供較高的射頻阻抗,使射頻信號不進入偏置網(wǎng)絡內(nèi)。

如果此2.6GHz信號帶有10MHz信號帶寬,位于基帶頻率的10MHz的包絡信號在經(jīng)過LC產(chǎn)生的壓降為0.1V左右,晶體管接收到的將不是一個穩(wěn)定的3.4V供電電壓,而是一個受包絡調(diào)制,擺幅0.1V的變化電壓。如果晶體管特性在0.1V供電電壓波動時不產(chǎn)生變化,輸出信號將看不到記憶效應。

如果這時將輸入信號帶寬提高到100MHz,則LC產(chǎn)生的包絡頻率壓降將提升至1V左右,這將對一個3.4V供電的電源帶來明顯影響,如果晶體管特性在1V的變化下發(fā)生明顯變化,記憶效應將顯現(xiàn)。所以,隨著信號帶寬的增加,偏置網(wǎng)絡引起的記憶效應現(xiàn)象將更加明顯。這也是為什么5G相比4G記憶效應問題更加突顯的原因。

以上是以輸出偏置網(wǎng)絡為例對電記憶效應其中一個成因的簡單描述。在PA設計中,PA輸入偏置網(wǎng)絡、阻抗匹配網(wǎng)絡的記憶效應均需要在設計中加以考慮。

對包絡信號引起IMD3變化的定量分析如下。

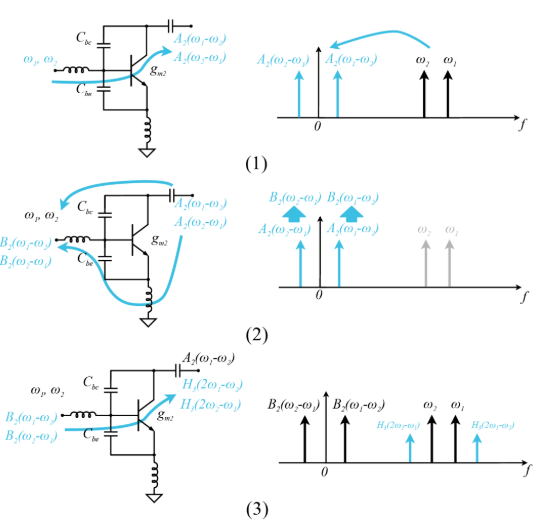

輸入放大器帶有一定帶寬的OFMD信號調(diào)制信號可以簡化為一組雙音信號,頻率分別為ω1,ω2,在只考慮HBT器件非線性跨導時gm2,IMD3信號產(chǎn)生過程如下:

輸入端雙音信號通過HBT器件 的二階非線性跨導gm2在輸出端產(chǎn)生包絡信號A2(ω1-ω2)、A2(ω2-ω1);

輸出端包絡信號通過寄生電容和源極電感等反饋通路反饋到輸入端,經(jīng)過反饋通路后到輸入端包絡信號為B2(ω1-ω2)、B2(ω2-ω1);

輸入端的包絡信號和輸入端的基頻信號ω1再次通過HBT的二階非線性跨導gm2產(chǎn)生二階交調(diào),在輸出端產(chǎn)生IMD3信號H3(ω1-ω2)、H3(ω2-ω1)、,造成線性度的惡化;

圖:寬帶信號激勵下,由于器件非線性引起IMD3的過程

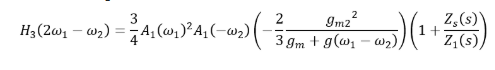

以上為寬帶信號IMD3產(chǎn)生及影響線性度惡化的過程,通過Volterra級數(shù)推導,由二次跨導非線性gm2和包絡信號產(chǎn)生的IMD3為:

通過以上公式也可以計算得到左側(cè)IMD3 H3(ω1-ω2)、H3(ω2-ω1)的表達式。需要說明的是,由于A2(ω1-ω2)及A2(ω2-ω1)位于零頻兩側(cè),二者阻抗不同,會導致第三步左右IMD3混頻結(jié)果不對稱,這也是左右ACLR不對稱的來源。

當信號帶寬變大時,即ω1與ω2頻率相差變大。如果不加以控制,A2(ω1-ω2)與A2(ω2-ω1)之間的阻抗差別也會變大,造成寬帶信號ACLR變差,這是寬帶信號記憶效應表現(xiàn)更明顯的原因。

可以看到,IMD3信號的大小與器件的線性與非線性跨導相關(guān),同時與源端、負載端等阻抗相關(guān)。以上公式可以用來設計和控制包絡信號產(chǎn)生IMD3分量的大小。

電熱記憶效應的規(guī)避

電記憶效應的來源是由于在PA設計中,諧波及包絡頻率阻抗過大引起,在設計中,要注意對這些阻抗加以處理,將包絡頻率與諧波頻率的阻抗盡量歸零。

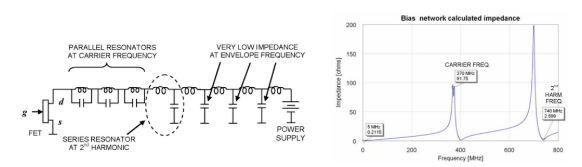

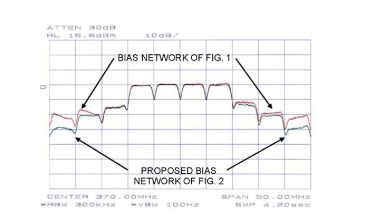

文章 [4]中提出了一種供電電路設計,此電路可以對基頻信號提供較高的阻抗(91.75Ω),同時使包絡信號及諧波信號保持較低的阻抗(0.2Ω及2.6Ω)。采用此偏置網(wǎng)絡,PA線性度和ACLR惡化現(xiàn)象明顯改善。

圖:文章 [4]所提出偏置網(wǎng)絡及其阻抗特性

圖:文章 [4]所提出偏置網(wǎng)絡對線性度有明顯改善

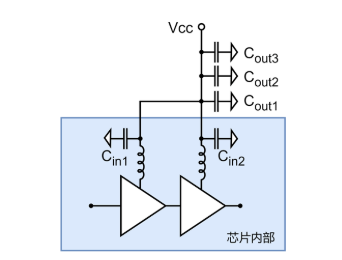

在PA芯片的手機應用中,由于偏置網(wǎng)絡在芯片內(nèi)部已經(jīng)設計好,重新設計偏置網(wǎng)絡不是一個可行的選項。但在應用中觀測到記憶效應時,還是需要對板級Bypass電容進行良好設計。

一般在PA芯片內(nèi)部,Bypass電容為100pF量級(在2.6GHz阻抗為0.6Ω的低阻),起到對射頻信號旁路功能。但100pF電容在100MHz處的阻抗為16Ω左右,無法為基帶頻率及包絡頻率提供低阻,所以,一定要在板級放置100nF量級Bypass電容,為包絡信號提供近似理想接地,降低電源引起的記憶效應。

圖:典型PA芯片的Bypass電容放置

器件的非線性引起的記憶效應需要借助對器件的非線性分析進行消除,常用分析方法是Volterra級數(shù)法等。通過對放大器偏置點、阻抗及非線性的控制,可以使器件非線性引起的記憶效應加以改善 [7]。

總 結(jié)

PA記憶效應是較為抽象的概念,反應PA特性隨時間的變化而變化,造成輸出信號的失真。

PA記憶效應是由包絡信號的幅度變化引起,OFDM調(diào)制帶來的信號峰均比經(jīng)過射頻調(diào)制后,形成包絡變化的射頻信號。如果PA特性隨包絡變化而變化,則將發(fā)生記憶效應。

電記憶效應是PA記憶效應最主要的來源,通過優(yōu)化偏置電路、節(jié)點阻抗可以有效地改善電記憶效應。在應用中,需要注意偏置電路中的Bypass電容設計,一定要在包絡頻率提供較低阻抗,確保包絡信號在偏置電路中不被調(diào)制起來。

在5G PA設計中,慧智微利用可重構(gòu)技術(shù)架構(gòu),可以對功率放大器各頻點阻抗進行調(diào)諧控制,有效解決5G PA的記憶效應問題,使5G PA大帶寬線性度明顯改善。

-

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421783 -

ofdm

+關(guān)注

關(guān)注

6文章

349瀏覽量

56982 -

5G

+關(guān)注

關(guān)注

1353文章

48367瀏覽量

563359

發(fā)布評論請先 登錄

相關(guān)推薦

什么是電池記憶效應?怎樣消除?

什么是“記憶效應”? (中英版)

電池的記憶效應是什么_鉛酸電池有記憶效應嗎

消除鎳鎘電池記憶效應的電路

電池記憶效應原理_電池記憶效應怎么解決

功率放大器居然有記憶效應?

什么是PA的“記憶效應”?

什么是PA的“記憶效應”?

評論