有許多朋友在學習,或者開發STM32時都遇到過HardFault_Handler的情況。

那么,又有多少人認真去分析過Fault這類異常中斷呢?

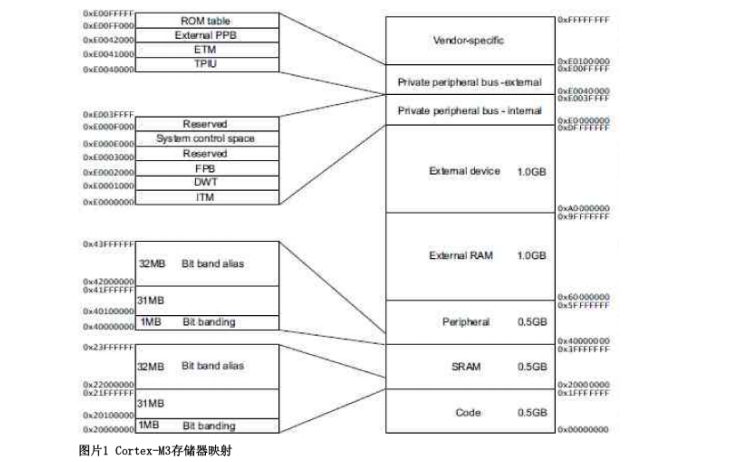

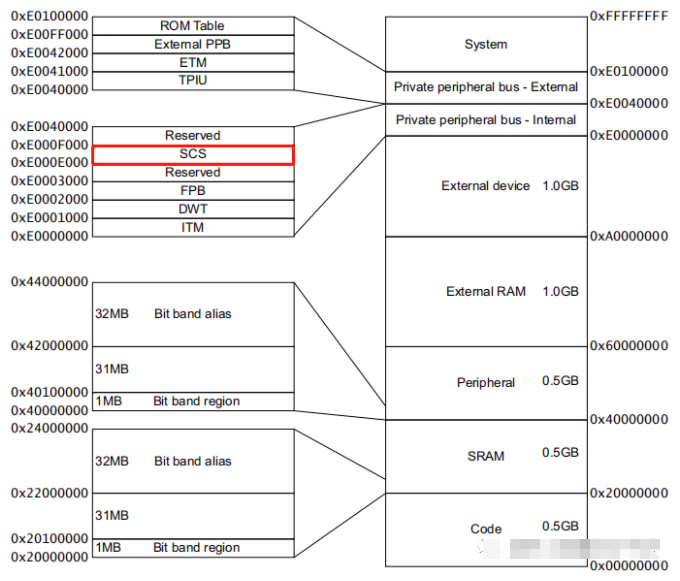

下面結合STM32F1(Cortex‐M3內核)來給大家講述一下這些異常中斷的內容。

1Cortex‐M3異常

說起Fault,我們就要說一下Cortex‐M3的異常。

Cortex‐M3 在內核上搭載了一個異常響應系統, 支持為數眾多的系統異常和外部中斷。

CM3部分異常列表:

這些異常中斷的優先級,有些卻是固定的,有些是可以通過軟件來配置,如UART發送中斷、DMA中斷等。

相信大家看到這個列表不會陌生,因為在STM32的啟動代碼,中斷代碼中都會看到這些異常。

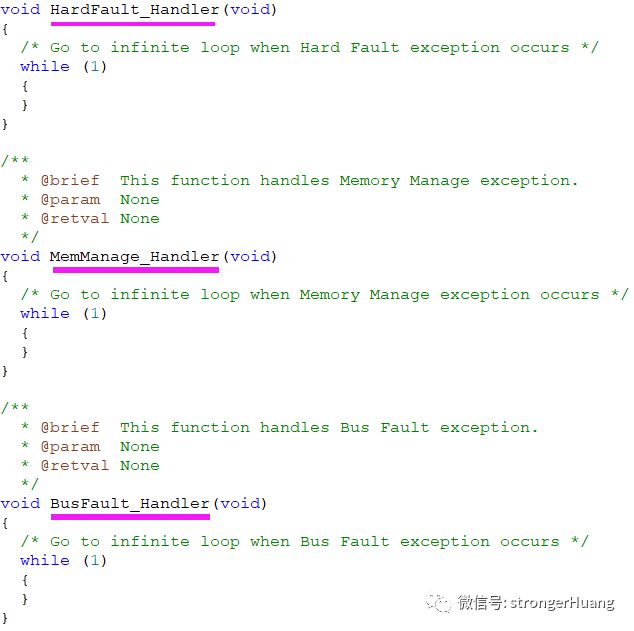

比如在stm32f10x_it.c文件中,就能看到HardFault_Handler這類Fault異常。

向量表

當發生了異常并且要響應它時, CM3 需要定位其處理例程的入口地址。這些入口地址存儲在“(異常)向量表”中。而我們的中斷函數就對應有一個入口地址。

2Fault錯誤異常

在Cortex‐M3中的Fault這種錯誤異常有:

BusFault總線錯誤

MemManageFault存儲器管理錯誤

UsageFault用法錯誤

HardFault硬錯誤

1.BusFault總線錯誤當 AHB 接口上正在傳送數據時,如果回復了一個錯誤信號,則會產生總線錯誤。

產生的場合可以是:

取指,通常被稱作“預取流產”(prefetch abort)

數據讀/寫,通常被稱作“數據流產”(data abort)

執行如下動作可以觸發總線異常:

中斷處理起始階段的堆棧 PUSH 動作。稱為“入棧錯誤”

中斷處理收尾階段的堆棧 POP 動作。稱為“出棧錯誤”

在處理器啟動中斷處理序列(sequence)后的向量讀取時。這是一種罕見的特殊情況,被歸類為硬錯誤。

總線錯誤誘因:

企圖訪問無效的存儲器 region。常見于訪問的地址沒有相對應的存儲器。

設備還沒有作好傳送數據的準備。比如,在尚未初始化 SDRAM 控制器的時候試圖訪問 SDRAM。

在企圖啟動一次數據傳送時,傳送的尺寸不能為目標設備所支持。例如,某設備只接受字型數據,卻試圖送給它字節型數據。

因為某些原因,設備不能接受數據傳送。例如,某些設備只有在特權級下才允許訪問,可當前卻是用戶級。

2.MemManageFault存儲器管理錯誤存儲器管理錯誤多與MPU(內存保護單元)有關,其誘因常常是某次訪問觸犯了MPU設置的保護策略。

常見誘因:

訪問了 MPU 設置區域覆蓋范圍之外的地址

往只讀 region 寫數據

用戶級下訪問了只允許在特權級下訪問的地址

在CM3手冊中有這樣一段話:在 MemManage fault 發生后,如果其服務例程是使能的,則執行服務例程。如果同時還發生了其它高優先級異常,則優先處理這些高優先級的異常, MemManage 異常被懸起。

如果此時處理器已經在處理同級或高優先級異常,或者 MemManage fault 服務例程被除能,則和總線 fault 一樣:上訪成硬 fault,最終執行的是硬 fault 的服務例程。

當我們程序內存訪問越界,我們會發現,程序會進入HardFault_Handler中斷服務程序。可以結合上面那一段話理解一下。

3.UsageFault用法錯誤用法錯誤發生的誘因:

執行了未定義的指令

執行了協處理器指令(Cortex‐M3 不支持協處理器,但是可以通過 fault 異常機制來使用軟件模擬協處理器的功能,從而可以方便地在其它 Cortex 處理器間移植)

嘗試進入 ARM 狀態(因為 CM3 不支持 ARM 狀態,所以用法 fault 會在切換時產生。軟件可以利用此機制來測試某處理器是否支持 ARM 狀態)

無效的中斷返回(LR 中包含了無效/錯誤的值)

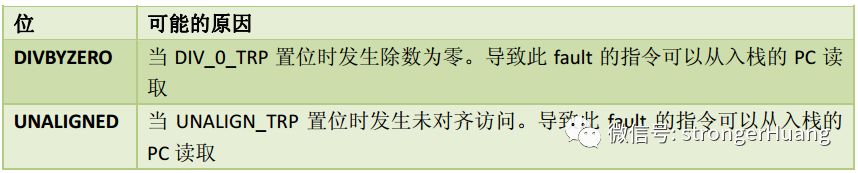

使用多重加載/存儲指令時,地址沒有對齊。另外,通過設置 NVIC 的對應控制位,可以在下列場合下也產生用法 fault:

除數為零

任何未對齊的訪問

4.HardFault硬錯誤HardFault硬錯誤是上面說的三種錯誤“上訪”的結果。如果這些fault錯誤的服務例程無法執行,它們就會成為“硬傷”——上訪(escalation)成HardFault硬錯誤。

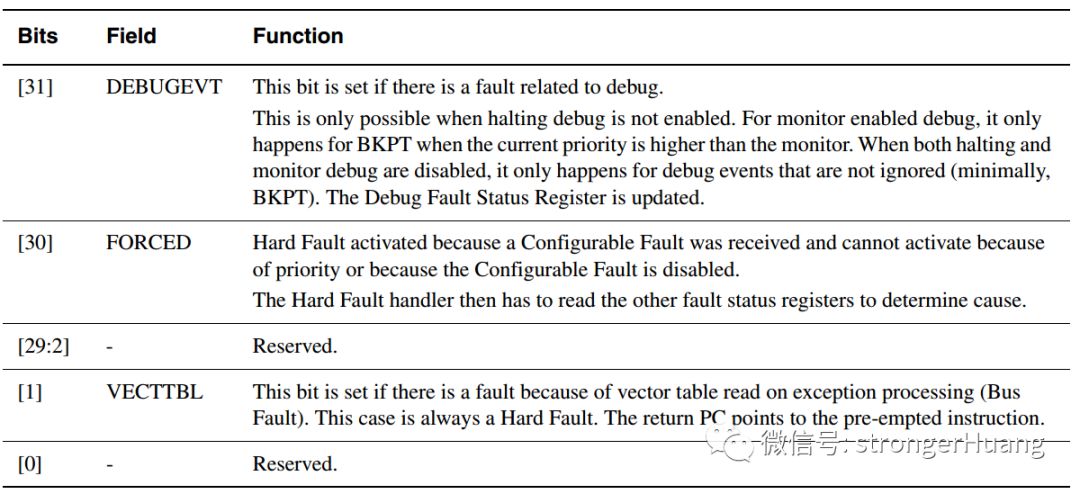

在NVIC 中有一個HardFault硬錯誤狀態寄存器(HFSR),它指出產生HardFault硬錯誤的原因。

狀態寄存器(HFSR):

3如何應對Fault錯誤異常

在軟件開發過程中,我們可以根據各種 fault錯誤 狀態寄存器的值來判定程序錯誤,并且改正它們。下面給出了各種 faults 的常見誘因,以及應對攻略。

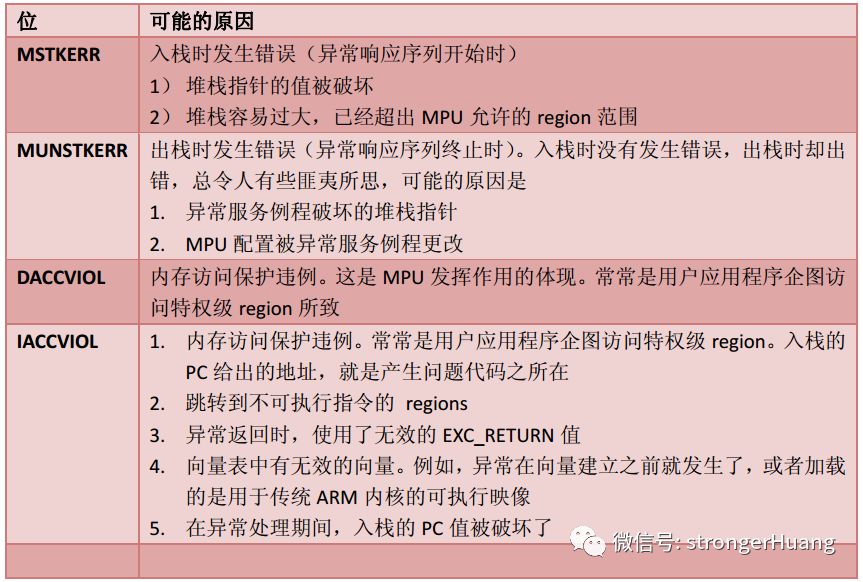

MemManage fault 狀態寄存器提供的訊息:

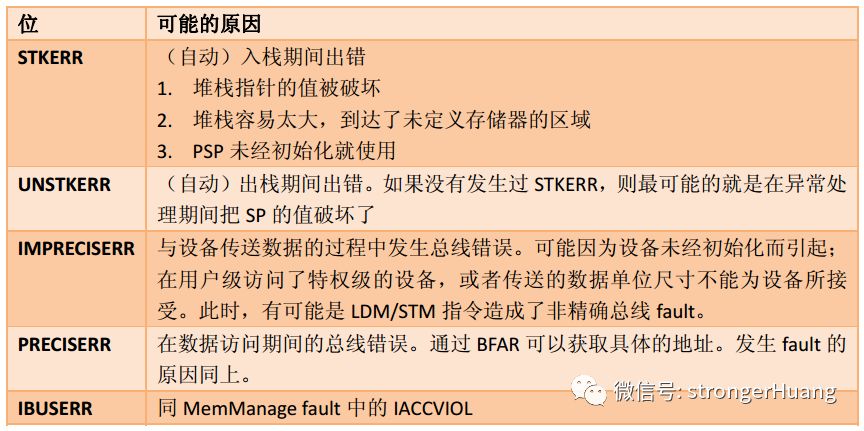

總線 fault 狀態寄存器提供的訊息:

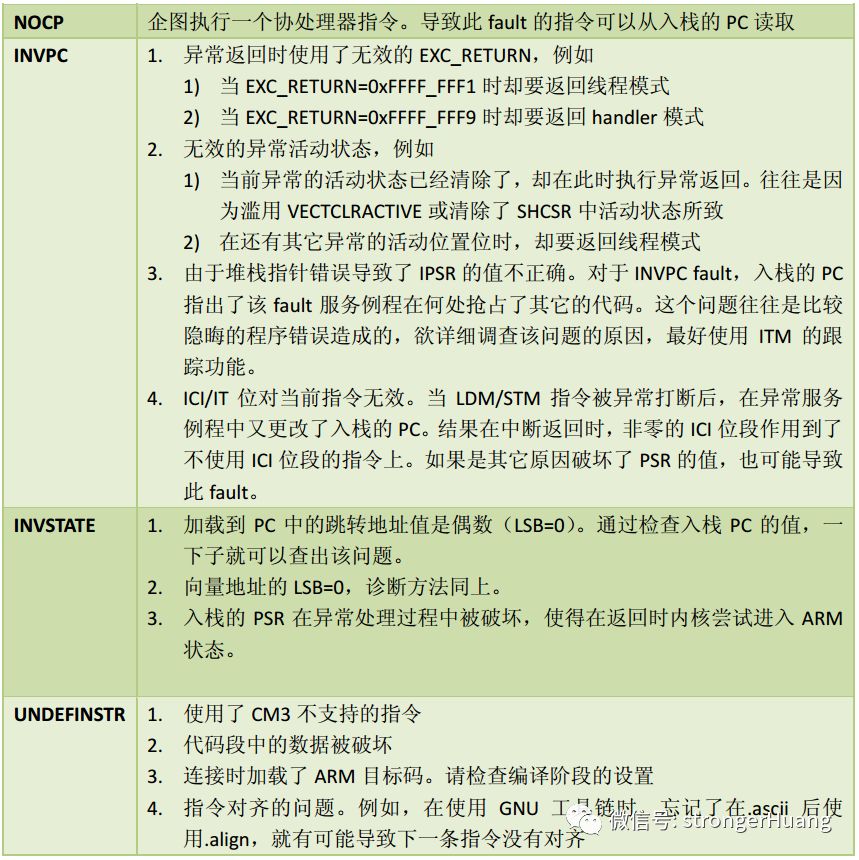

用法 fault 狀態寄存器提供的訊息:

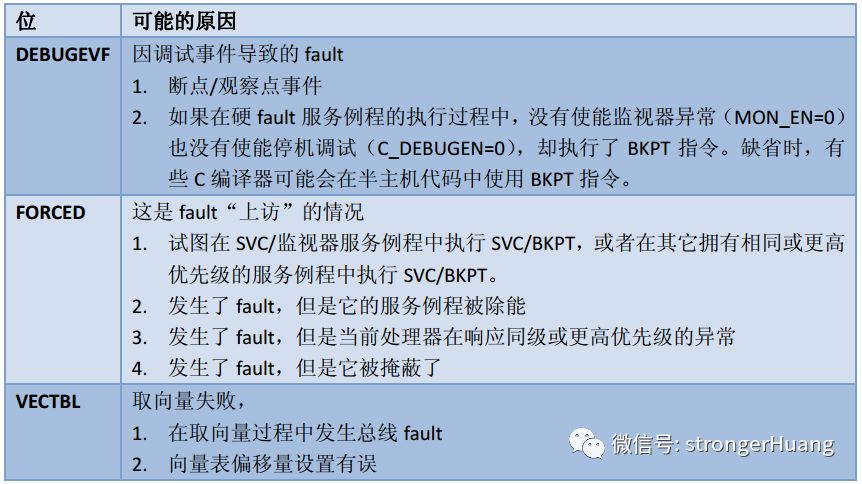

硬 fault 狀態寄存器提供的訊息:

常見應對Fault錯誤的方法:1.恢復:在一些場合下,還是有希望解決產生 fault 的問題的。例如,如果程序嘗試訪問了協處理器,可以通過一個協處理器的軟件模擬器來解決此問題——當然是以犧牲性能為代價的,要不然還要硬件加速干啥。

2.中止相關任務:如果系統運行了一個 RTOS,則相關的任務可以被終結或者重新開始。

3.復位:這也是最后一招。通過設置 NVIC“應用程序中斷及復位控制寄存器”中的VECTRESET 位,將只復位處理器內核而不復位其它片上設施。取決于芯片的復位設計,有些CM3 芯片可以使用該寄存器的 SYSRESETREQ 位來復位。這種只限于內核中的復位不會復位其它系統部件。

當然,說了這么多,我們還是要從根源出發,平時保持良好的編程習慣,以及遵循必要的編程規范。

原文標題:ARM基礎教程 | 深入 Cortex‐M3 的 Faults異常

文章出處:【微信公眾號:strongerHuang】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

內核

+關注

關注

3文章

1363瀏覽量

40228 -

Cortex-M3

+關注

關注

9文章

269瀏覽量

59429 -

異常

+關注

關注

0文章

22瀏覽量

9218

原文標題:ARM基礎教程 | 深入 Cortex‐M3 的 Faults異常

文章出處:【微信號:strongerHuang,微信公眾號:strongerHuang】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cortex-M3的異常處理機制分析

Cortex-M3內核浮點型運算的研究與實現

ARM中異常中斷問題詳情分析總結

介紹STM32F4在Cortex-M4內核和Cortex-M3內核方面的優勢

ARM異常中斷的原因及處理措施

Cortex-M3內核的ARM處理器的應用資料說明

Cortex-M3的異常和中斷資料下載

Cortex-M3處理器內核與基于Cortex-M3的MCU關系

Cortex-M4和Cortex-M3內核的systick不進中斷的軟件延時

Cortex-M3內核的異常中斷

Cortex-M3內核的異常中斷

評論