寫在前面

Chiplet最近可謂是風口正勁,但是芯片行業并不是簡簡單單比拼誰能做出來就可以,而是需要通過大規模量產催動行業更新,同時還要考慮產品良率、封裝良率、各種成本等等。在這個前提下,只有chiplet折算下來的好處能夠明顯超過傳統soc方案,才能夠被非常好的推廣。今天這篇文章,我們就專門來算算錢。文中數據皆真實可考,一部分獲取于2021年我們自己的芯片加工與封裝等,一部分借助于chiplet產業聯盟所獲取。

摘要/導讀

多芯片集成技術被業界廣泛認為是摩爾定律的延續,節省成本是其廣為人知的優勢之一,但是很少有工作能夠定量地展示多芯片集成系統對比單芯片的成本優勢。我們基于三種典型的多芯片2.5D集成技術,建立了一個定量的多芯片系統成本模型,并提出了一套分析方法,從良品率提高、芯片和封裝復用以及異構集成等多方面分析了多芯片系統的成本效益。文章被Design Automation Conference (DAC) 2022錄用。清華交叉院博士研究生馮寅瀟是該論文的第一作者,清華大學交叉院助理教授馬愷聲是該論文的通訊作者。

近年來,包括AMD、intel和華為在內的工業界推出了大量的多芯片集成產品,多芯片架構的經濟性已逐漸成為人們的共識。然而,在實踐中,由于封裝成本和Die-to-Die互連接口的開銷,多芯片系統的成本優勢并不容易實現。與傳統的單芯片系統相比,多芯片集成系統的成本計算變得更加復雜,如果不經過認真評估,盲目采用多芯片架構反而會導致更高的成本。 因此,我們建立一個名叫“Chiplet精算師”的成本模型,利用此模型對多芯片集成系統的成本效益進行了精致的評估,并回答了架構設計者所面臨的諸多難題:

該采用何種封裝集成方案?

該把整個系統拆成多少小芯片?

是否應該在多個系統間復用封裝?

如何復用芯片?

如何發揮異構集成的優勢?

具體的模型細節和考慮因素見最后。

我們來看看用以上成本模型得到的一些結論:1.不是所有的芯片在經濟上都適合用Chiplet技術。

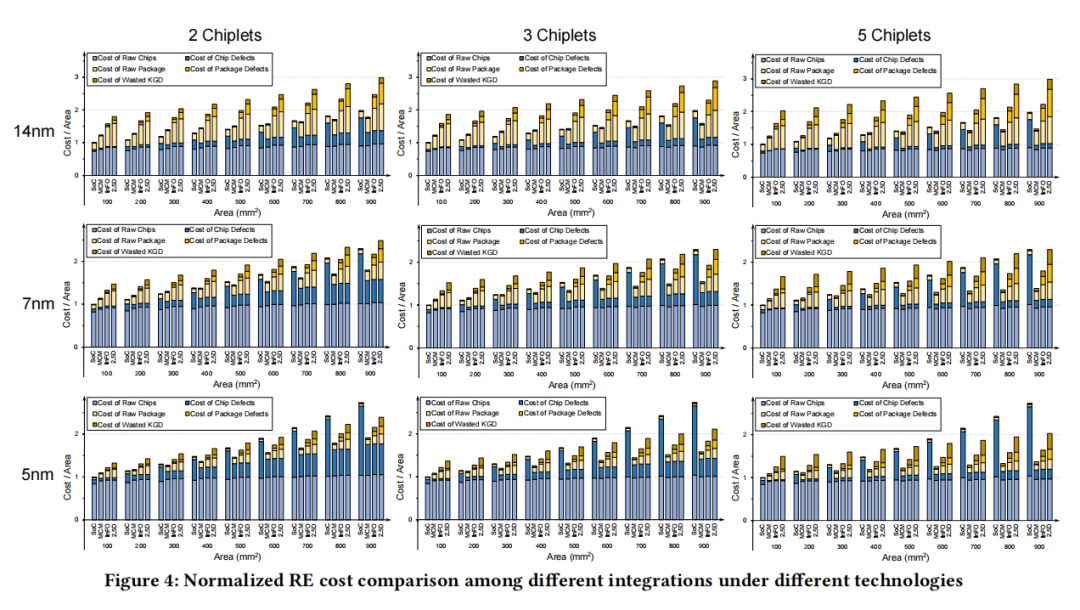

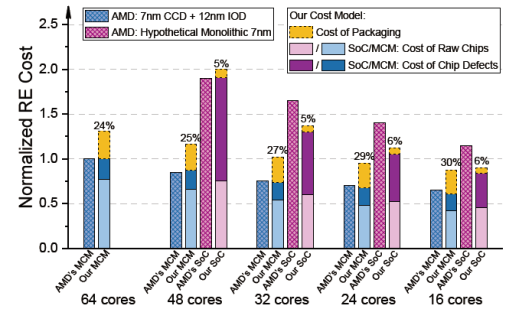

這張圖中的9個柱狀圖,都是RE Cost(recurring engineering cost,可以理解成不考慮一次性投入,生產一片芯片的錢),橫向是14nm,7nm,5nm,縱向是幾個chiplets封裝到一起。

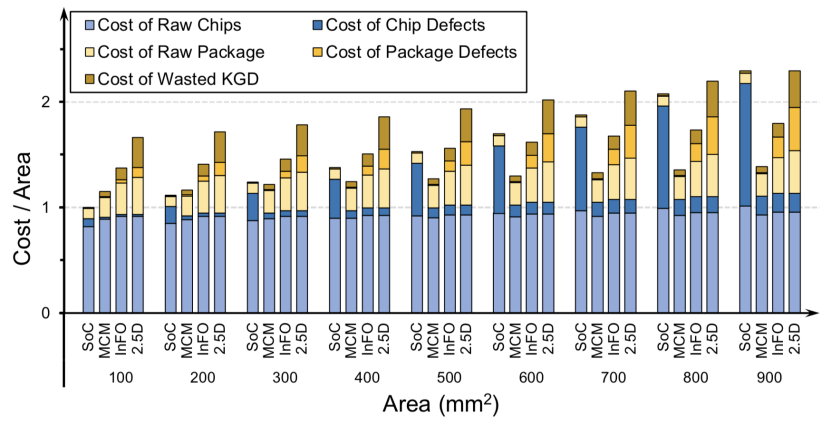

我們再看一個詳細的圖,是上圖中7nm,5個chiplets拼一起放大版。圖的橫軸是面積,縱軸是單位面積成本。四種封裝方式為:SoC,MCM封裝,InFO,2.5D封裝。

可以看到,如果在200平方毫米以下,沒有必要做chiplets。真正有收益的時候在800平方毫米以上的大芯片。這也是為什么今天超大的芯片用chiplets方案,因為經濟上確實是更合適的。

另外,伴隨先進封裝而來的大量測試、封裝成本,極其先進的封裝都非常昂貴,甚至數倍于硅的成本,首要解決的是能不能做大芯片的問題。未來隨著封裝價格的下降,chiplets路線會越來越有收益。

MCM和InFO成本相對更低,更劃算,預計基于先進封裝里面的基礎封裝的芯片會更早起量。

2.多芯片集成在越先進工藝下(如5nm)越具有顯著的優勢,因為在800mm2面積的單片系統中,硅片缺陷導致的額外成本占總制造成本的50%以上。對于成熟工藝(14nm),盡管產量的提高也節省了高達35%的成本,但由于D2D接口和封裝開銷(MCM:>25%,2.5D:>50%),多芯片的成本優勢減弱。

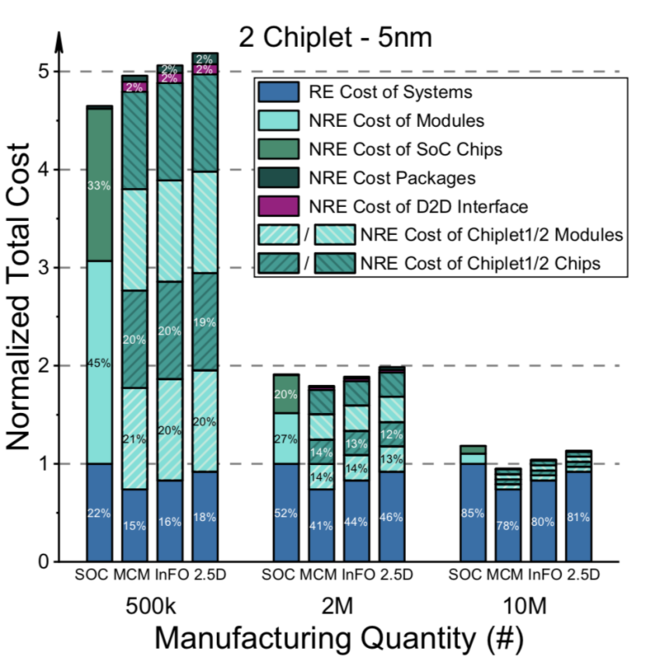

3.雖然制造成本是需要考慮的主要成本,但一次性投入的成本往往是決定性的,特別是對于沒有巨大產量保障的產品。對于單個系統,我們發現,單獨做每個小芯片,都存在很高的一次性投入成本,如流片時掩膜板的成本,因此多芯片架構導致總的一次性投入成本非常高(50萬產量時占到總成本的36%)。對于5nm系統,當產量達到2千萬時,多芯片架構開始帶來回報。

也就是說,如果單一企業想要靠著自研全部的小芯片來搭建芯片,并且只有一款芯片的話,并不劃算。但是確實能帶來比如高中低檔次芯片的搭配等優勢。

當然,這里面一次性投入成本可以伴隨著小芯片的復用,得到巨大的收益。

下面,我們來談談復用:通過許多探究實驗發現,多芯片架構的成本優勢需要通過充分利用復用和異構來實現。把常見的多芯片復用架構分為三類:單芯片多系統(SCMS)、一中心多拓展(OCME)和固定插座多組合(FSMC)。

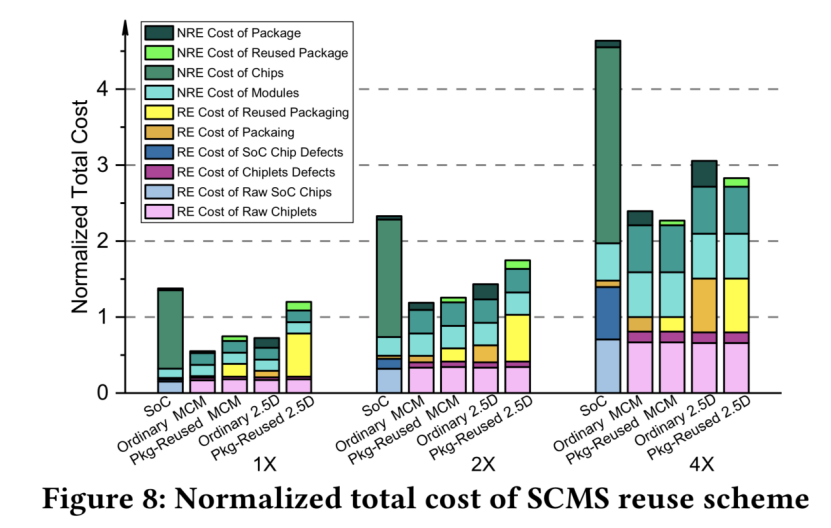

1.對于SCMS架構,由于芯片復用,與單芯片系統相比,芯片大量節省了一次性投入成本。該復用方案的最大優點是只需要一個芯片,因此無需制造多個芯片即可立即生效,這種架構適用于同一產品線不同等級的產品。

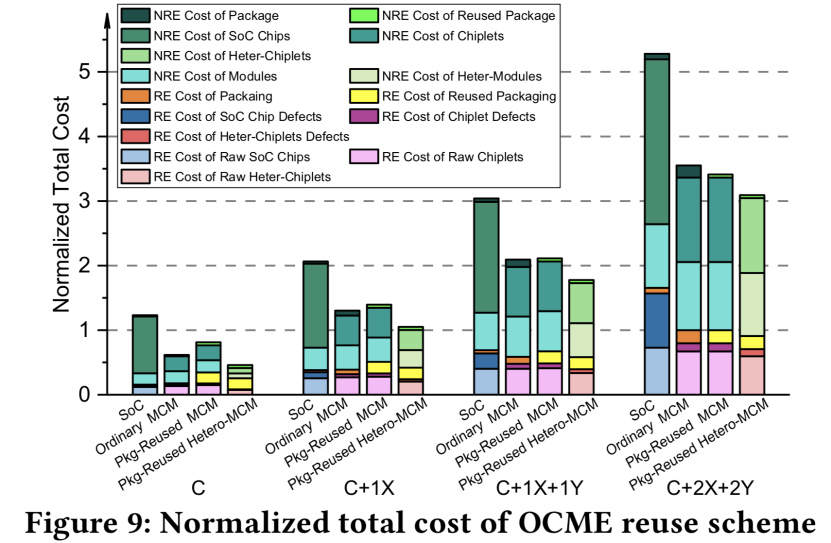

2.OCME架構相比SCMC,使得異構工藝成為可能,如果把多個系統共用的對先進工藝不敏感的模塊坐在落后工藝的中心硅片上,可以帶來巨大的收益,許多包含了DDR、PCIe等模塊的系統都可以采用此架構。數據中的Pkg-reused的概念是封裝復用,比如一個基板上可以放4個,實際上只放了2個die,另外兩個die用dummy die填充以解決散熱和應力問題。那這樣封裝看起來并不是最大化利用的,但是總體來看,反而更加劃算了。

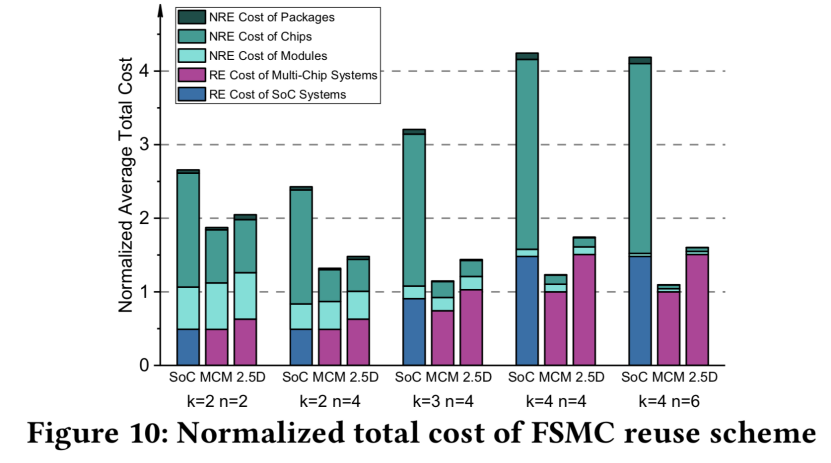

3.對于FSMC架構,則是把復用可能性最大化了,復用的芯片越多,一次性投入成本攤銷的收益就越大。當可復用性得到充分利用時,均攤后的先期投入就會小到可以忽略。在這一點上,多芯片架構的巨大成本節約潛力便顯現出來。成本優勢不僅體現在制造成本的節約上,也體現在一次性投入成本的節約上。看得出來,到了最后,誰的手里有更多的die,或者說誰的方案能兼容更多的die,誰就能更多節省成本。

(圖中k是package上面有多少個slot,n是手里有多少種不同的die)

總結

多芯片架構已成為未來的發展趨勢。然而,多芯片架構的優勢不是無條件的,而是取決于許多復雜的因素。為了幫助芯片架構師在多芯片架構上做出更好的決策,我們建立了一個定量模型來比較不同方案的成本。模型允許設計師在早期階段驗證成本。我們還展示了多芯片體系結構如何從良率提高、芯片和封裝復用以及異構性中獲益:

當硅片缺陷的成本超過封裝導致的成本時,多芯片架構開始帶來回報。

系統越接近摩爾極限(最先進工藝,最大面積),多芯片架構的成本效益就越高。

更小的芯片粒度帶來的成本效益具有邊際效應,所以,把單獨一個IP做成一個die是不劃算的。

是否復用封裝取決于制造成本和均攤的一次性投入成本哪個占主導地位。量小的時候,要盡量的復用封裝;量多的時候,可以單獨再次開發先進封裝。這個平衡點大約在80-100萬顆每年。

對于檔次分明的同質系統,SCMS方案具有顯著的成本優勢;對于共享大面積HUB模塊的系統,采用OCME方案更具成本效益;FSMC方案提供了最大的復用可能性,但是對die的形狀,以及四邊的接口數量要求很高。

基本原則是用更少的芯片構建更多的系統,芯片復用的成本效益對于破碎化、層次化的需求更為明顯。

站在今天的角度看:先進封裝,并不是越先進越好,價格過高,數倍于硅的成本,決定了其不會大范圍量產使用;反而是,基本版本的先進封裝在性能上基本上可以滿足架構訴求,可能會最先被大范圍使用。提高良率、降低成本是國內封裝廠的要務(尤其是在基板生產方面)。從未來的角度看,據我們所知,國內有接近十家基板廠商在建設,數家先進封裝廠在建設,按照兩年建廠,兩年良率爬坡的發展節奏,未來三四年后,先進封裝良率和成本將迎來大幅優化。到時候,Chiplet技術應用將迎來規模性爆發。

機會仍在,國內同仁仍需努力!

模型細節和考慮因素

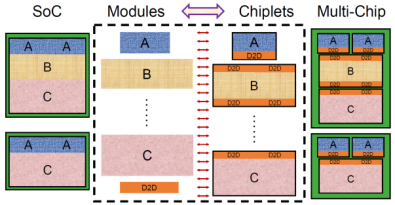

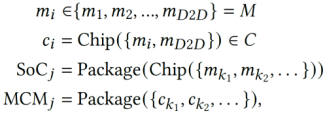

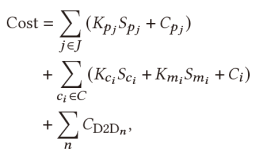

Chiplet精算師引入了模塊、芯片和封裝三個概念,任何一個系統都可以由這三個層次構成。其中,每個Chiplet對應一個模塊,D2D接口作為一個特殊的模塊在多個Chiplet間復用,可以用數學語言表達為:

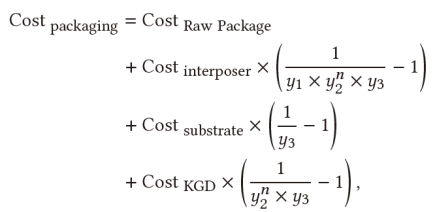

芯片的制造成本可以大致分為:(1)硅片成本,(2)硅片缺陷導致的損失,(3)封裝成本,(4)封裝缺陷導致的損失,以及(5)封裝缺陷所導致好硅片的浪費。(1)(2)兩項在前人的工作中已經被充分討論,與多芯片集成和先進封裝相關的(3)(4)(5)成本可以表達為:

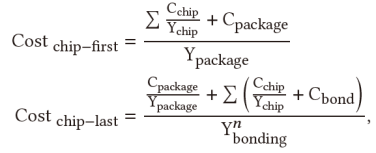

其中,y1是中間插入層制造的良率,y2是芯片與插入層鍵合的良率,y3是中間插入層與基板鍵合和良率。與此同時,chip-first與chip-last兩種不同的封裝工藝流程也被考慮在內:

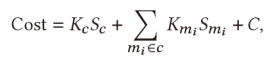

一次性投入成本(NRE,包括軟件與IP授權、系統設計驗證以及流片費用等)占據了總成本的一大部分。我們從面積入手,在成本模型中引入了一次性投入成本。對于任何一個芯片,其一次性投入成本可以估計為:

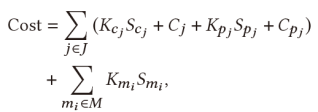

其中Sc是芯片的面積,Sm是模塊的面積,C是與面積無關的固定投入。由此可以得到如果要設計若干套系統,如果均采用單芯片架構,總的一次性投入成本可以估計為:

而如果采用多芯片架構,總的一次性投入成本可以估計為:

其中,Sp是封裝面積,Cp是封裝的固定投入,CD2D是開發D2D接口的投入。 KmSm:與模塊面積相關的NRE成本,包括模塊前端設計、模塊前端驗證等。 KcSc:與芯片面積相關的NRE成本,包括架構設計、系統驗證、后端設計、后端驗證等。 C:與芯片和模塊面積無關的NRE成本,包括軟件授權、IP授權、流片(芯片試制的掩膜費用)等。 KpSp:與封裝面積相關的NRE成本,包括封裝設計等。 Cp:與封裝面積無關的NRE成本,包括封裝制造開模等成本。 其他開銷,比如設備費、場地費、日常維護費用視情況包含于C或KcSc。 這個成本模型在AMD的多芯片架構上進行了驗證,在硅片成本上,取得了與AMD公開數據基本一致的結果。區別在于AMD沒有算入先進封裝集成多塊芯片的額外成本。

審核編輯 :李倩

-

芯片

+關注

關注

454文章

50438瀏覽量

421904 -

chiplet

+關注

關注

6文章

417瀏覽量

12560

原文標題:算一算Chiplet的成本

文章出處:【微信號:電子工程世界,微信公眾號:電子工程世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

算力基礎篇:從零開始了解算力

長沙角逐算力江湖,長沙市新一代智算產業生態聯合體成立

中科曙光入選2024算力服務產業圖譜及算力服務產品名錄

算力系列基礎篇——算力101:從零開始了解算力

算力十問:超算智算,通算及算存比

“捷智算”正式入駐國家超算互聯網平臺

千億美元打造一個系統,成本越來越高的AI超算

智能算力規模超通用算力,大模型對智能算力提出高要求

算一算Chiplet的成本

算一算Chiplet的成本

評論