電子發(fā)燒友網(wǎng)報道(文/吳子鵬)3月初的時候,英特爾、AMD、Arm、高通、臺積電、三星、日月光、谷歌云、Meta、微軟等行業(yè)巨頭組建了一個Chiplet標(biāo)準(zhǔn)聯(lián)盟,并制定了一套通用的Chiplet高速互聯(lián)標(biāo)準(zhǔn)“Universal Chiplet Interconnect Express”(簡稱:UCIe)。

Chiplet標(biāo)準(zhǔn)聯(lián)盟的成立是一件意料之中的事情,而這個聯(lián)盟的初始創(chuàng)建沒有大陸芯片公司同樣不會讓人感到意外。雖然已經(jīng)有芯原股份宣布加入了這個聯(lián)盟,但該聯(lián)盟由誰主導(dǎo)也是顯而易見的。在當(dāng)前的國際競爭格局下,大陸芯片產(chǎn)業(yè)是一個特殊的存在,被美歐日韓等半導(dǎo)體巨頭處處提防。

那么,大陸是否有必要去構(gòu)建一套自己的Chiplet標(biāo)準(zhǔn)呢?讓我們通過常用的SWOT分析法,來具體看一下這種做法的可行性和利弊。

Chiplet需要標(biāo)準(zhǔn)

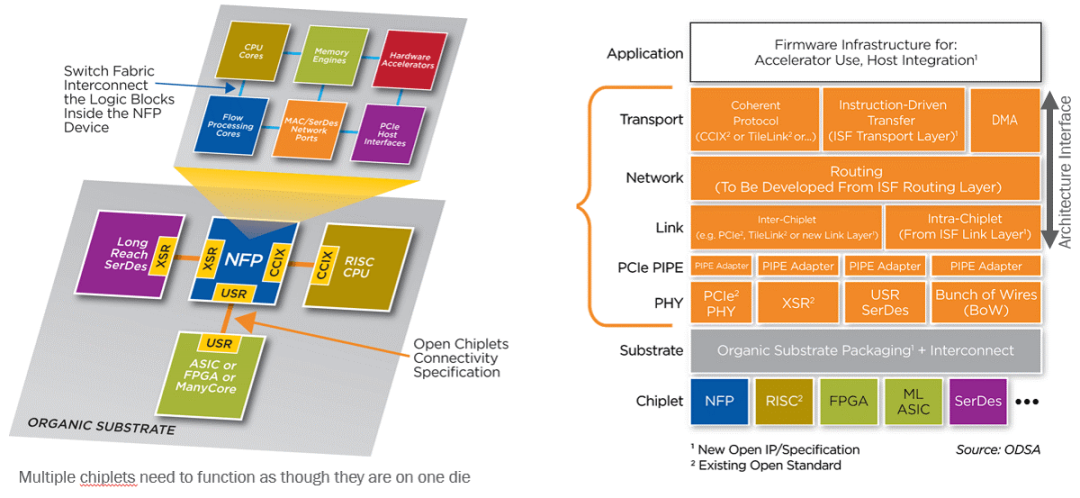

Chiplet的中文名是芯粒或者小芯片。通過下圖能夠看到,Chiplet這項技術(shù)有四個核心的構(gòu)成部分,分別是基礎(chǔ)功能芯片、具備特定功能的裸片(die)、die-to-die內(nèi)部互聯(lián)技術(shù)以及特定的封裝技術(shù)。

圖源:ODSA工作組

Chiplet的好處是顯而易見的。首先,die的復(fù)用能夠降低系統(tǒng)復(fù)雜度,降低研發(fā)成本;其次,芯片性能的提升不再是只能依靠摩爾定律;第三,功能單元模塊化提高了芯片的制造良率,進而降低制造成本;第四,Chiplet給了封裝產(chǎn)業(yè)一個明確的創(chuàng)新方向。英特爾首席架構(gòu)師沙爾瑪在UCIe聯(lián)盟官網(wǎng)發(fā)布的白皮書中這樣總結(jié)Chiplet的商業(yè)價值,“從設(shè)計角度看,能夠有效降低投資,節(jié)省不必要的跨工藝節(jié)點IP移植成本,縮短產(chǎn)品上市周期;從制造角度看,有利于制造環(huán)節(jié)良率控制、產(chǎn)能爬坡;從產(chǎn)品角度看,不同計算、存儲、I/O芯片(die)的靈活組合,使敏捷芯片定制成為可能。”

那么很顯然,Chiplet是需要一套通用標(biāo)準(zhǔn)的,關(guān)于die的尺寸,關(guān)于die-to-die如何互聯(lián),關(guān)于封裝后的接口IP如何布局,關(guān)于如何部署測試機臺等等。如果沒有標(biāo)準(zhǔn),Chiplet便會成為一次又一次的ASIC設(shè)計,省不下多少功夫,更形不成規(guī)模產(chǎn)業(yè),也就不是一門好生意。

比如,現(xiàn)階段AMD和蘋果會采用Chiplet的方式去構(gòu)建芯片,雖然明面上看著成本會有所下降,因為很多功能單元是此前就設(shè)計好的,但背后的IC設(shè)計、封裝和測試成本都非常高。并且,在沒有標(biāo)準(zhǔn)的情況下,選定了哪一家的die就真的是選定了,后面看到了更好的也換不起,因為一個功能單元的替換,可能就意味著整顆芯片的重新設(shè)計。

在摩爾定律明顯放緩的當(dāng)下,Chiplet一定是產(chǎn)業(yè)的發(fā)展趨勢,但是要讓Chiplet成為一個規(guī)模產(chǎn)業(yè),標(biāo)準(zhǔn)是必不可少的。

但是,以美國為首的國際半導(dǎo)體廠商當(dāng)然不想有大陸芯片公司在所謂的“開放”的UCIe標(biāo)準(zhǔn)中起到主導(dǎo)作用,那么大陸是否要自己搞一套呢?接下來進入SWOT分析環(huán)節(jié)。

大陸建Chiplet標(biāo)準(zhǔn)的優(yōu)勢(S)

美國有蘋果、英特爾和AMD等公司搞Chiplet,大陸也并非只能在邊上看著不做事,實際上華為此前就公布過“芯片堆疊技術(shù)”相關(guān)的專利,其實就是Chiplet類似的技術(shù),清華大學(xué)微電子所所長、中國半導(dǎo)體行業(yè)協(xié)會副理事長魏少軍教授也曾多次在公開演講中提到過芯片封裝從2.5D向3D的演進,芯原股份創(chuàng)始人、董事長兼總裁戴偉民博士更是力推Chiplet,大陸其實更早之前就成立過Chiplet聯(lián)盟,說明大陸的科技公司以及從業(yè)者是重視Chiplet的。

如果大陸自己建一套Chiplet標(biāo)準(zhǔn),是否有自己的優(yōu)勢所在?

我想大陸的優(yōu)勢主要會有兩點,其一是大陸現(xiàn)階段已經(jīng)擁有從IC設(shè)計到封裝測試這樣完備的產(chǎn)業(yè)鏈基礎(chǔ),且大陸在封裝環(huán)節(jié)的實力處于全球領(lǐng)先水平。當(dāng)前,大陸在封裝環(huán)節(jié)擁有長電科技、通富微電、華天科技三大龍頭企業(yè),根據(jù)2021年Q1的公開營收數(shù)據(jù),三家廠商均是全球前十的水平,其中長電科技排名第三位。

其二是大陸擁有更好的應(yīng)用市場,通過上方ODSA工作組分享的Chiplet概念圖可以看到,Chiplet是在芯片設(shè)計制造環(huán)節(jié)提出了一個可行路線,而其還需要軟件、設(shè)計工具等的配合,最后應(yīng)用到終端市場。那么,終端市場具有一定規(guī)模且明確的需求便能夠促進Chiplet的發(fā)展,對基于此打造出來的系統(tǒng)級芯片有帶動作用。

大陸建Chiplet標(biāo)準(zhǔn)的劣勢(W)

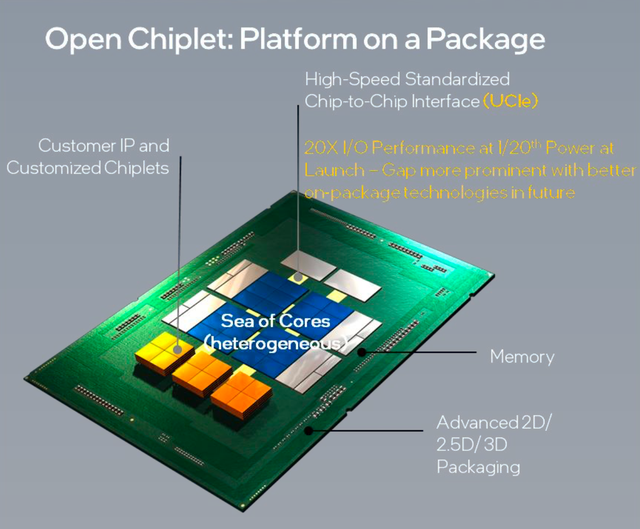

在探討大陸自己建Chiplet標(biāo)準(zhǔn)的劣勢之前,我們看一下另一張圖片。下圖來自UCIe聯(lián)盟的示意圖,就像我們上面提到的,這里面會有基礎(chǔ)的核心芯片,也會有一些特定功能的die,以及各種連接協(xié)議,包括芯片內(nèi)部的和外部的。

圖源:UCIe聯(lián)盟

那么大陸芯片產(chǎn)業(yè)的劣勢就顯露出來了。由于大陸現(xiàn)階段芯片制造工藝和核心芯片的性能都不強,因此可以說基礎(chǔ)不牢靠,Chiplet主要面向高性能的系統(tǒng)級芯片,那么在高性能這一點上大陸芯片產(chǎn)業(yè)現(xiàn)狀還不達標(biāo)。其實大陸現(xiàn)在能夠達到國際領(lǐng)先水平的芯片并不多,大部分芯片還混跡在中低端,那么die的性能也會拖后腿。

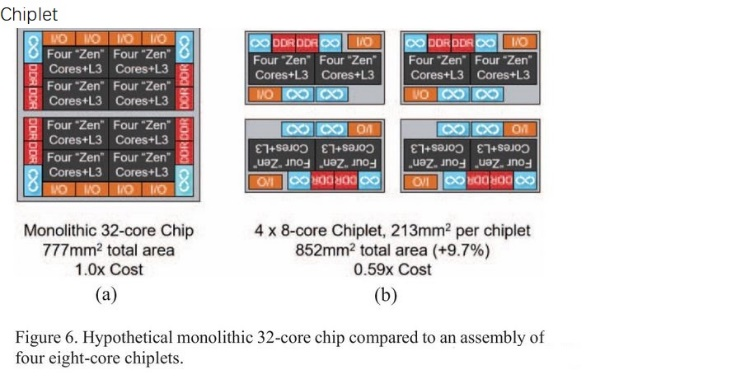

另外還有我們常常提到的IP和EDA環(huán)節(jié),下圖是AMD在介紹Chiplet技術(shù)時用到的示意圖,很顯然Chiplet這種組裝的方式在單個功能塊上的制造難度會顯著降低,但在系統(tǒng)層面還是需要將這些功能塊組合起來,并且可能出現(xiàn)3D堆疊的效果,這需要更加智能化的EDA工具和IP支持,但這一塊長期以來都是國內(nèi)的薄弱環(huán)節(jié)。

圖源:AMD

因此,國際EDA工具提供商是否配合大陸的Chiplet標(biāo)準(zhǔn)也是一個問題。

大陸建Chiplet標(biāo)準(zhǔn)的機會(O)

SWOT中的“O”代表機會,通常是分析外部環(huán)境,在此我們可以提一下目前的大環(huán)境。

Chiplet的好處顯而易見,一定是一個產(chǎn)業(yè)趨勢,且必將在芯片產(chǎn)業(yè)發(fā)揮重要的作用,這是毋庸置疑的,因此擁抱Chiplet也就成為一個必然的結(jié)果。而目前的國際形勢也表明,傳統(tǒng)的國際半導(dǎo)體巨頭并不想帶著我們一起玩,這些積極的和消極的因素都提供了大陸自己搞Chiplet標(biāo)準(zhǔn)的契機。

在機會這里我們必須還要重提摩爾定律失速,這也是國際半導(dǎo)體巨頭抱團搞Chiplet標(biāo)準(zhǔn)的重要原因,在大陸芯片制造被高端***“扼住咽喉”的時候,規(guī)模量產(chǎn)10nm以下工藝的芯片看似遙遙無期,那么Chiplet這種能夠放大工藝效益的技術(shù)就應(yīng)該去搞。

另外,在大的產(chǎn)業(yè)環(huán)境里,除了講Chiplet,先進封裝本身就是一個大方向,而Chiplet會起到積極的促進作用,從這個層面看,大陸想穩(wěn)固芯片封裝方面的優(yōu)勢,也得參與到Chiplet中來。

大陸建Chiplet標(biāo)準(zhǔn)的威脅(T)

在SWOT分析方法中, “T”代表威脅。那么,這個“威脅”實際上就是如果我們搞了自己的Chiplet標(biāo)準(zhǔn),會面臨哪些外部的沖擊。筆者認(rèn)為,威脅可以歸結(jié)為可能存在的制裁,包括可能存在美政府要求使用美國技術(shù)的公司不為大陸Chiplet標(biāo)準(zhǔn)聯(lián)盟成員提供產(chǎn)品和技術(shù)支持,以及對聯(lián)盟成員的其他制裁措施。

Chiplet是一個產(chǎn)業(yè)鏈協(xié)作的創(chuàng)新技術(shù),而在這個鏈路上,大陸芯片產(chǎn)業(yè)處處存在后發(fā)的弱勢,每一項都可能帶來巨大的威脅。

關(guān)于Chiplet的爭論

實際上,國內(nèi)早就有Chiplet聯(lián)盟,由芯動科技和清華大學(xué)人工智能交叉研究院發(fā)起,目標(biāo)正是推動Chiplet技術(shù)的國產(chǎn)化進程。據(jù)悉,目前國內(nèi)已經(jīng)制定了自己的chiplet標(biāo)準(zhǔn)草案,名為《小芯片接口總線技術(shù)要求》,由中科院計算所、工信部電子四院和國內(nèi)多個芯片廠商合作展開標(biāo)準(zhǔn)制定工作,是一個較為純粹的die-to-die連接協(xié)議,即將完成后續(xù)意見征詢、技術(shù)驗證和發(fā)布的工作。

我們從知情人士的透露獲知,國內(nèi)的標(biāo)準(zhǔn)出發(fā)點是自主原生,那么必然和UCIe標(biāo)準(zhǔn)存在差異化,算是邁開了第一步。但與此同時,質(zhì)疑聲也不小,Chiplet技術(shù)的出發(fā)點是為了讓高性能運算芯片的成本降低,要是生硬地被走成國產(chǎn)芯片的自主化道路,是否丟掉了這項技術(shù)最大的價值,是否有些本末倒置?

古人云:亂世用重典,沉疴下猛藥。但古人還說過,竭澤而漁。底層基礎(chǔ)決定上層建筑,拉著國內(nèi)目前領(lǐng)先廠商搞一個自己的Chiplet標(biāo)準(zhǔn),投入產(chǎn)出比想來不會高,且尤為重要的EDA工具由誰來配合也是一個問題。我覺得現(xiàn)階段國內(nèi)當(dāng)然要研究Chiplet技術(shù),成立聯(lián)盟和協(xié)會都沒有問題,但并不急著搞一套自己的標(biāo)準(zhǔn)去做對抗,這樣做多少有點閉門造車的意思。

原文標(biāo)題:用SWOT分析法看中國大陸是否應(yīng)該制定自己的Chiplet標(biāo)準(zhǔn)

文章出處:【微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

450文章

49636瀏覽量

417211 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

26331瀏覽量

210074 -

chiplet

+關(guān)注

關(guān)注

6文章

404瀏覽量

12513

原文標(biāo)題:用SWOT分析法看中國大陸是否應(yīng)該制定自己的Chiplet標(biāo)準(zhǔn)

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

中國大陸成全球半導(dǎo)體制造設(shè)備銷售核心市場

中國大陸8家半導(dǎo)體大廠被調(diào)查!

中國大陸芯片設(shè)備支出領(lǐng)跑全球

喜報 | 江西薩瑞微榮獲中國大陸半導(dǎo)體功率器件企業(yè)第32名

中國大陸是否有必要構(gòu)建自己的Chiplet標(biāo)準(zhǔn)

中國大陸是否有必要構(gòu)建自己的Chiplet標(biāo)準(zhǔn)

評論