系統總覽

RapidIO標準分為三層:邏輯,傳輸和物理。

邏輯層定義整體協議和數據包格式。這是端點啟動和完成事務(transaction)所必需的信息。

傳輸層提供數據包從端點移動到端點所需的路由信息。

物理層描述了設備級接口細節,例如數據包傳輸機制,流控制,電氣特性和低級錯誤管理。

這種劃分提供了將新事務類型添加到邏輯規范的靈活性,而無需修改傳輸或物理層規范。

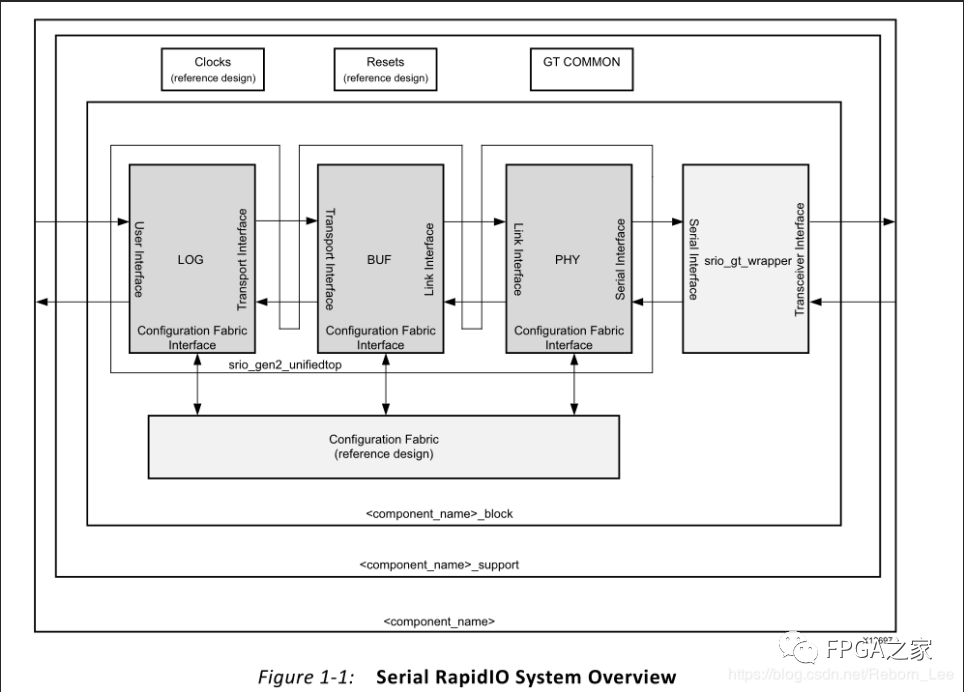

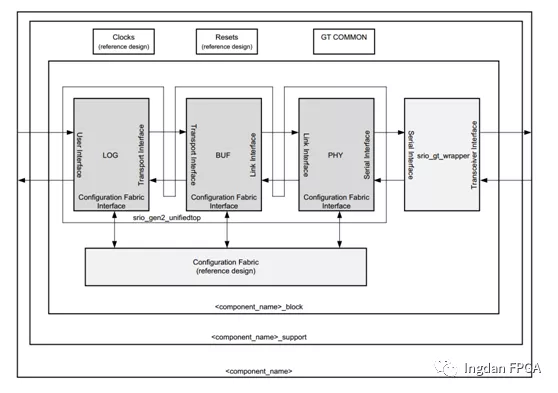

下圖是FPGA端 SRIO IP核系統總覽圖:

從圖中可以看出:

The SRIO Gen2 Endpoint is comprised of the following:

? A Serial RapidIO Gen2 top-level wrapper (srio_gen2__unifiedtop) containing:

Serial RapidIO Gen2 Physical Layer (PHY)

Serial RapidIO Gen2 Logical (I/O) and Transport Layer (LOG)

Serial RapidIO Gen2 Buffer Design (BUF)

? Reference design for clocking, resets, and configuration accesses

圖中的層次結構如下:

The srio_gen2__unifiedtop wrapper contains the LOG, BUF, and PHY.

The _block integrates the srio_gen2__unifiedtop wrapper, the srio_gt_wrapper, and configuration fabric reference design.

The _support wrapper contains the clock and reset modules.

is the top-level wrapper. This wrapper is used to integrate an entire SRIO Gen2 Endpoint into your design.

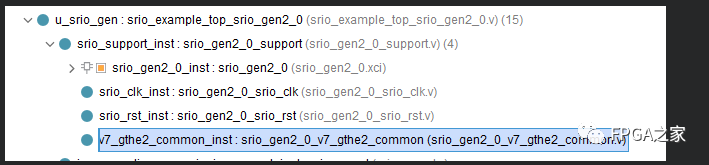

上面的這張圖的關系,也可以通過IP提供的例子程序的層次結構窺見一二:

Top-Level Wrapper

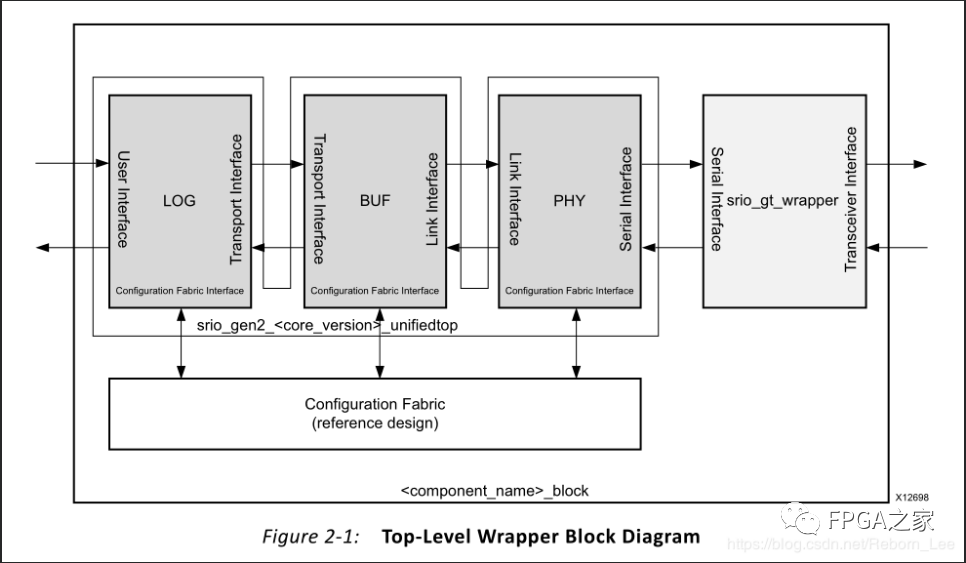

如下圖為頂層封裝原理圖:

_block模塊捆綁了SRIO Gen2端點的每個組件,包括參考設計,以提供圍繞其設計的打包解決方案。圖2-1提供了 _block模塊每個部分的基本框圖,以及 _block設計的每個部分之間的數據交互的一般視圖。

Port Descriptions

Logical Layer Interfaces

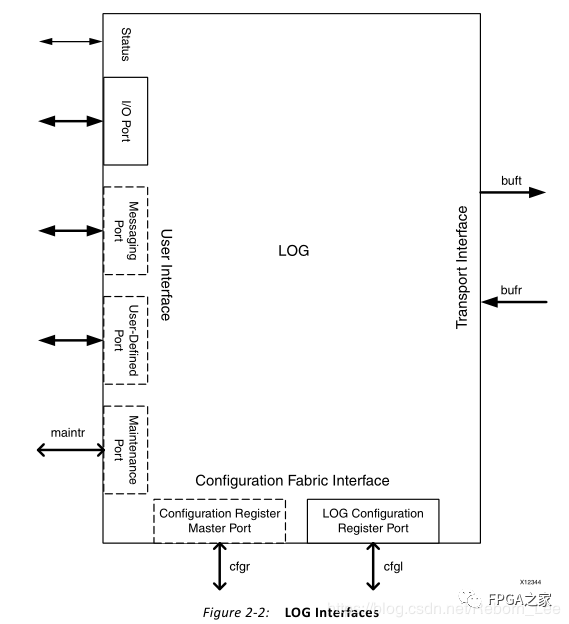

The LOG has three interfaces:

? User Interface

? Transport Interface

? Configuration Fabric Interface

如下圖為邏輯層接口的詳細視圖:

Figure 2-2 shows the ports associated with each of the LOG interfaces.

上圖中,實箭頭表示AXI4-Stream ports,空箭頭為AXI4-Lite ports;

這兩種端口的區別?自行了解。

用戶端口包含可以發出或使用數據包的端口。生成IP核時,可以配置與每個端口關聯的端口數和事務(Transaction)類型。還可以從這些端口啟動配置讀和寫訪問到駐留在此 SRIO Gen2 終結點設備中的配置寄存器或遠程設備。這些接口通過Serial RapidIO包裝器輸出,用于數據包生成和使用。

傳輸接口包含兩個端口,接收和發送,旨在與RapidIO兼容的物理層或緩沖應用程序連接。此接口在包裝器模塊外部是不可見的。

配置結構接口包含兩個端口:

? Configuration Master port,通過Configuration Fabric發出對本地配置空間的讀寫。

? LOG Configuration Register port,它是一個從接口,用于讀取和寫入任何配置寄存器,這些寄存器定義為邏輯或傳輸層的一部分。

配置結構解碼來自配置總線主機的讀或寫地址,并將它們傳遞到LOG,PHY和BUF的配置寄存器端口。此交互完全保留在 _block模塊中。

User Interfaces

上面說的邏輯層的端口分為用戶端口、傳輸端口以及配置端口,這里來細看下用戶端口:

The user interface contains a set of I/O ports and the following optional ports:

? Messaging Port

? Maintenance Port

? User-Defined Port

每種事務(transaction)類型都分配給特定端口。通常,在I / O端口上發送或接收任何支持的I / O事務,例如NWRITE,NWRITE_R,SWRITE,NREAD和RESPONSE(不包括MAINTENANCE響應)。MESSAGE事務(如果支持)可以分配給Messaging端口或I / O端口。無論消息端口是否存在,DOORBELL事務都使用I / O端口。如果啟用了維護(maintenance)端口,則維護端口上應支持所有維護數據包。如果事務是用戶定義的,不受支持的類型,或者沒有分配的端口,則它使用用戶定義的端口(當禁用用戶定義的端口時,將丟棄與另一個端口不對應的接收數據包)。

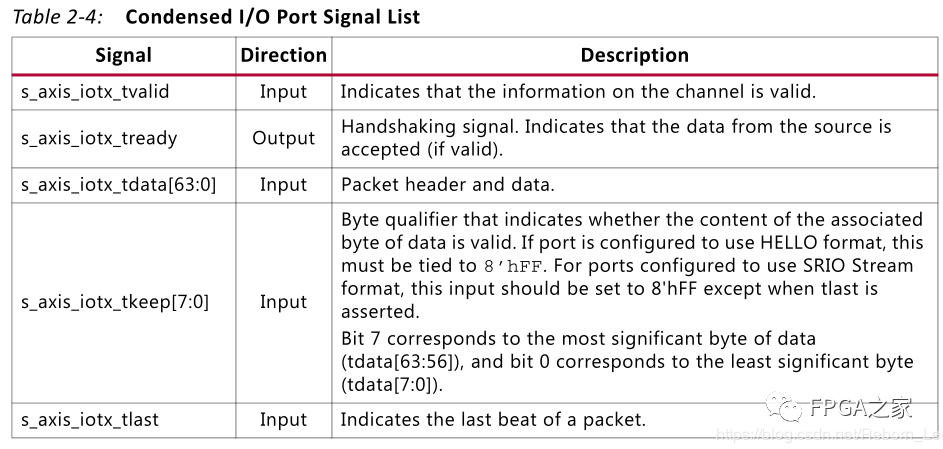

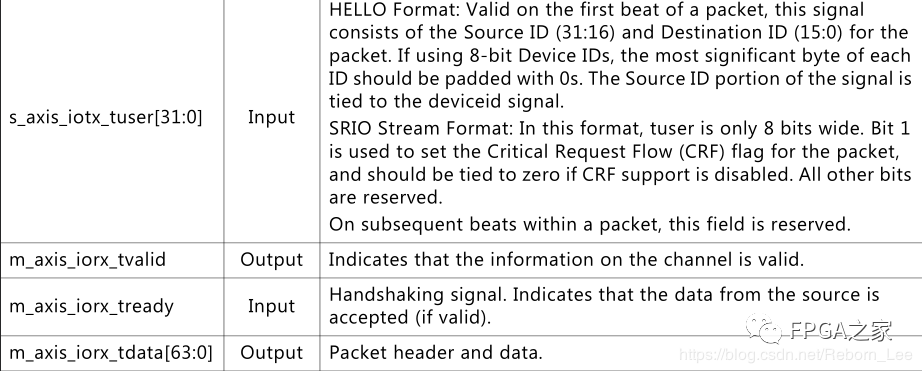

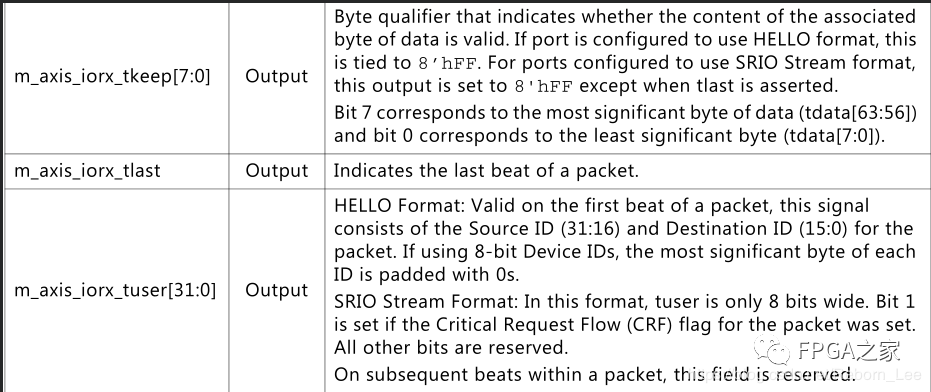

I/O Port

I / O端口可以配置為兩種樣式之一:Condensed I/O or Initiator/Target. 。可用信號取決于IP核生成期間選擇的樣式。

The I/O port is built from AXI4-Stream channels,有兩種數據包格式:

? HELLO

? SRIO Stream

I / O端口中的所有通道必須使用相同的數據包格式,該格式在生成核心時選擇。

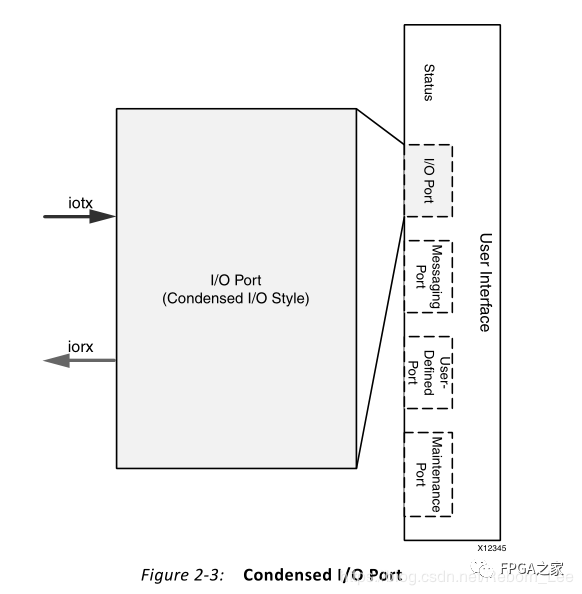

Condensed I/O

The Condensed I/O 樣式減少了用于傳輸和接收I / O數據包的通道數。有一個AXI4-Stream通道用于傳輸與I / O端口(iotx)相關的所有數據包類型。類似地,有一個信道用于所有接收的I / O端口數據包(iorx)。圖2-3顯示了Condensed I / O端口。

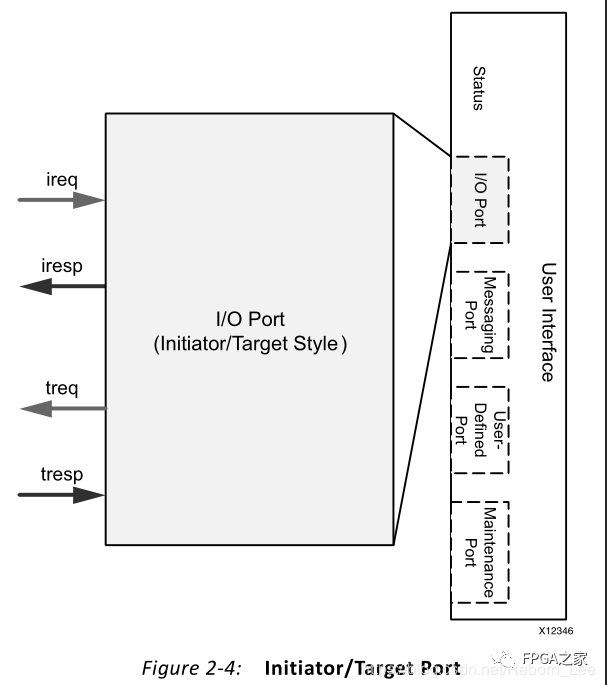

Initiator/Target

Initiator / Target端口樣式允許將針對遠程設備(放置在Initiator端口上)的事務與針對本地端點(放置在Target端口上)的事務分離。

由本地端點(local endpoint )生成的請求被置于要在鏈路上傳輸的啟動器請求(ireq)信道上。從遠程設備接收的響應在發起者響應(iresp)信道上呈現給用戶設計。

這句話還是原文比較好理解:

Requests generated by the local endpoint are placed on the Initiator Request (ireq) channel to be transmitted on the link. Responses received from a remote device are presented to the user design on the Initiator Response (iresp) channel.

Requests originating from a remote device which are received by the core are presented to the user design on the Target Request (treq) channel. Responses to these requests, which are generated by the user design, are placed on the Target Response (tresp) channel.

意思是本地設備的請求信號在ireq channel上,對應的遠程設備的響應在iresp channel上。

而遠程設備的請求在treq上,對應的本地響應在tresp上。

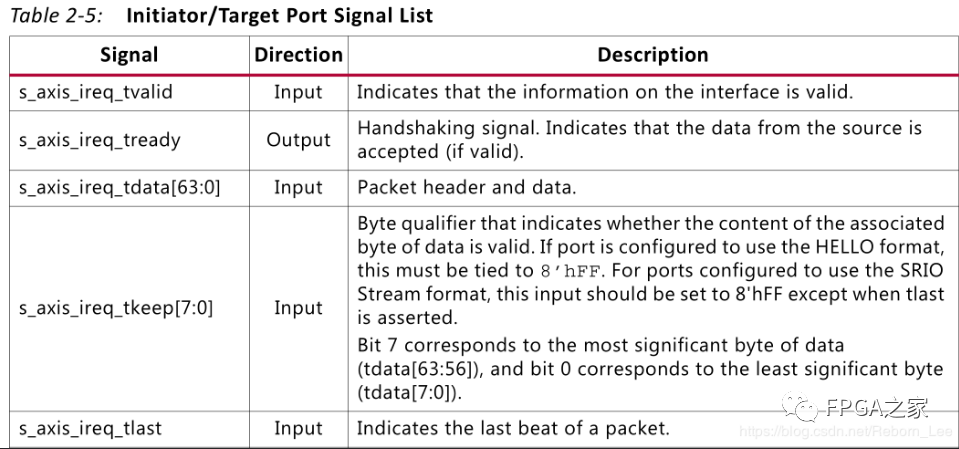

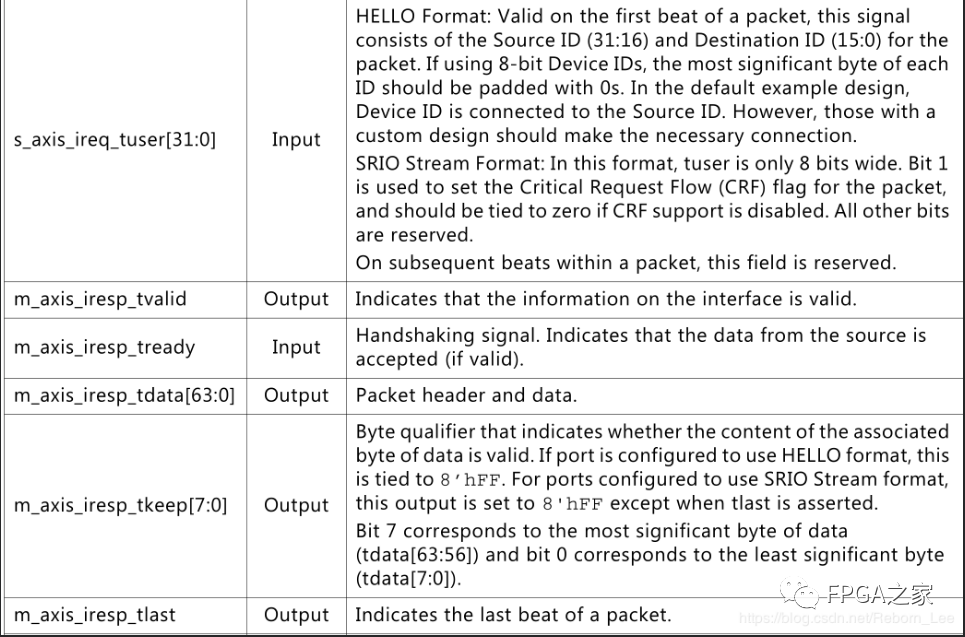

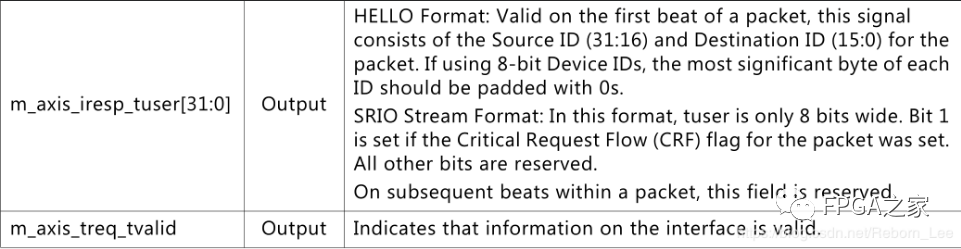

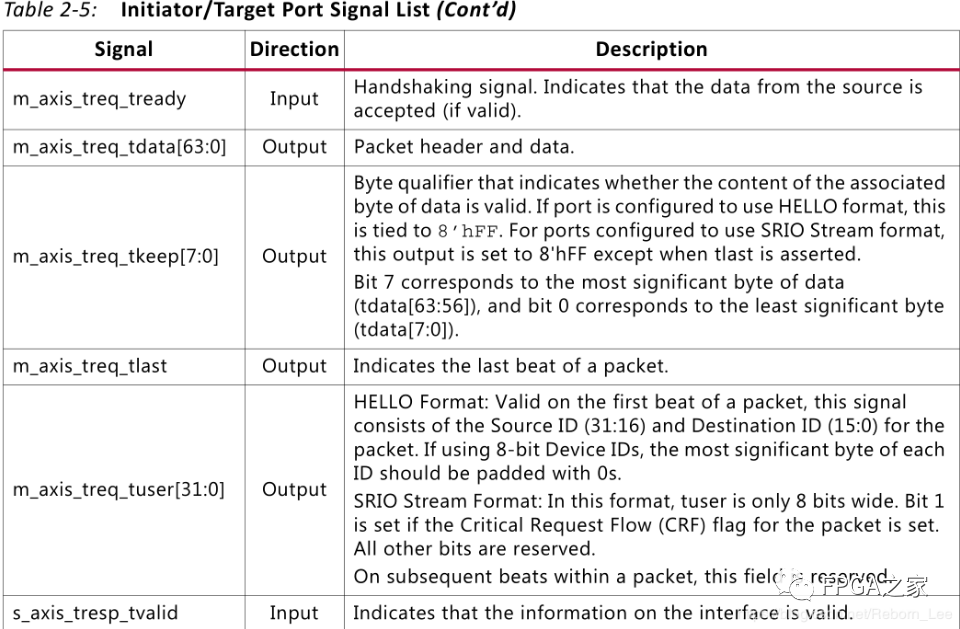

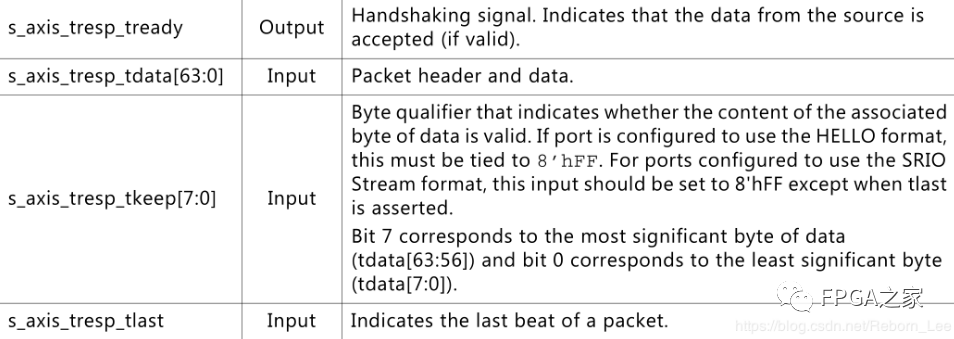

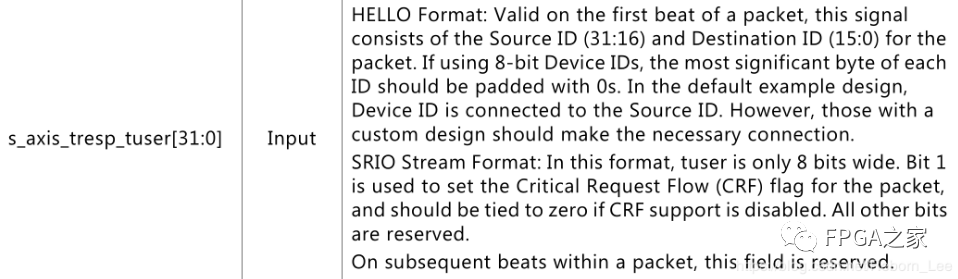

Table 2-5 shows the signals associated with the Initiator/Target port. At the level, the following signals are associated with these interfaces:

? s_axis_ireq* are associated with INITIATOR_IREQ.

? m_axis_iresp* are associated with INITIATOR_IRESP.

? m_axis_treq* are associated with TARGET_TREQ.

? s_axis_tresp* are associated with TARGET_TRESP.

好,這篇博文到這里,至于通俗的解釋(說人話),我會隨著我的理解不斷加深而更新。

下篇博文繼續講Messaging端口等。

原文標題:【FPGA】SRIO IP核系統總覽以及端口介紹(一)(User Interfaces 之 I/O Port)

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598972 -

端口

+關注

關注

4文章

916瀏覽量

31862 -

IP核

+關注

關注

4文章

318瀏覽量

49271

原文標題:【FPGA】SRIO IP核系統總覽以及端口介紹(一)(User Interfaces 之 I/O Port)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于FPGA IP核

FPGA IP核的相關問題

請問用c6678 srio收發地址位數,DSP端keystone_srio的程序要做什么改進?

FPGA實現基于Vivado的BRAM IP核的使用

Xilinx SRIO IP介紹和使用經驗分享

【FPGA】SRIO IP核系統總覽以及端口之Messaging Port介紹

FPGA端SRIO IP核系統總覽及端口介紹

FPGA端SRIO IP核系統總覽及端口介紹

評論