緒論

在計算機與電子產品的世界中,我們習慣于通過兩種截然不同的方法實現計算:硬件以及軟件。計算機硬件,比如專用集成電路(ASIC),為關鍵任務提供了運算快速與資源高度優化的方案。但是 ASIC 一旦設計與加工完成,這其中需要花費數以百萬美元的成本與大量努力,就只能永久性地配置為單一應用的解決方案。計算機軟件可以靈活地改變應用,可以進行大量不同的計算任務。但是軟件相比 ASIC 硬件實現,在性能、硅片面積效率以及功耗等方面的表現有數量級的差距。

現場可編程邏輯門陣列(FPGA)是一種真正意義上的革命性器件,融合了軟件與硬件各自的優勢。FPGA 所實現的電路與專用硬件相似,提供遠超軟件的功耗、面積以及性能。而且,能夠輕易并低成本地重新編程,以適應范圍廣泛的、不同的計算任務。與專用計算硬件一樣,FPGA 能夠利用空間上分布于整個芯片的資源并行數以百萬計的運算,相較于軟件所基于的通用處理器,速度運算最高可以快上百倍。然而,與 ASIC 不同的是,這些運算任務是編程到 FPGA 器件中的,而不是像 ASIC 一樣是在生產中固化的。這意味著基于 FPGA 的系統可以多次編程或者重編程(reprogrammed)。

有時,重編程可用于修復系統的錯誤行為,或者用于添加新的功能。而有時,FPGA 也可通過重編程轉換為一個為新運算任務量身設計的計算引擎。利用在運行過程中的可重編程特性,單個 FPGA 芯片甚至能夠實現多塊專用芯片的不同功能。

但確實,FPGA 實現軟硬件兩者的優勢并不是沒有代價的。FPGA 幾乎具有軟件所有的靈活性優勢以及可以使用軟件開發模型,并且具有接近硬件的高效率優勢——但無論是相比軟件還是硬件,FPGA 實現還是有差距。相較于運行軟件的通用微處理器,FPGA 的性能與功耗效率最高可比前者要高上幾個數量級,但是高效的 FPGA 系統開發過程要復雜的多。通常來說,FPGA 只適合于處理以較長數據流為輸入的運算,比如信號處理、網絡以及其他數據流應用。相較于 ASIC,FPGA 在面積、延遲以及性能方面有 5-25 倍的差距。然而, 單個 ASIC 設計需要數個月到幾年的時間,花費幾百萬美元,FPGA 開發則僅需幾天,成本在幾十至幾百美元之間。(譯注:通常這個說法適用于 FPGA 實現單一功能,而不是整個系統,后者的開銷無疑會更高)對于那些不需要極高性能或者效率的系統來說,FPGA 實現是一個更吸引人的方案,因為 FPGA 方案開發更為簡單,并可通過可重編程特性輕松地修復缺陷與添加功能。對于許多任務,尤其是對初學的電子開發者來說,FPGA 是一種理想的選擇。

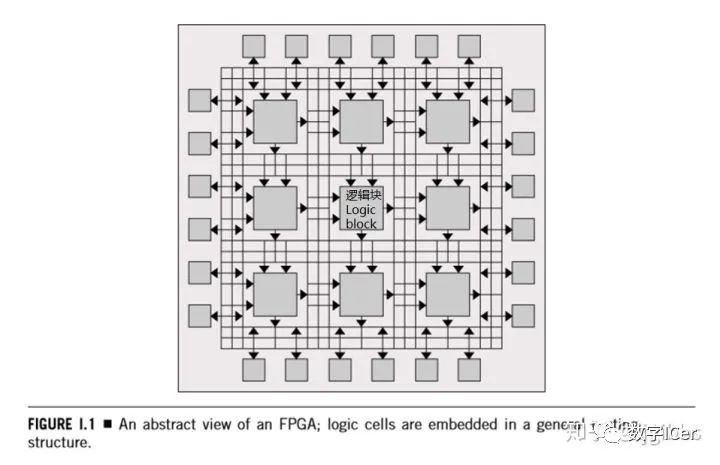

圖 I.1 FPGA 內部結構抽象;邏輯塊(內部大方塊)嵌入在通用布線結構中

圖 I.1展示了 FPGA 的內部構造。其內部由邏輯塊組成,邏輯塊嵌入在一個通用的布線結構中。邏輯塊可實現基礎邏輯門(Gate),大量邏輯塊排列成陣列(Array),這就是 FPGA 中的 ‘G’ 和 ‘A’ 的由來。邏輯塊由處理單元與觸發器構成,分別用于實現組合邏輯與時序邏輯。處理單元是一小塊存儲空間,可實現任意的五輸入或者六輸入的布爾函數。(譯注:處理單元即為查找表(LUT),輸入數量取決于具體器件)通用布線結構支持邏輯塊端口間任意的連線,所以各個邏輯塊可以按開發者設想的順序連接。

得益于 FPGA 的通用性與靈活性,可以實現非常復雜的電路。目前的 FPGA 器件可以實現百萬門(譯注:電路中的組合邏輯電路規模等效于百萬個基礎邏輯門,如與非門)電路,工作頻率達到上百MHz(譯注:一般在300MHz以下)。為了提高電路的速度以及規模,FPGA 在邏輯塊陣列的基礎上增加了一些特別的單元,比如大規模的存儲塊(BRAM)、乘法器、快速進位鏈(fast-carry)甚至加入整個微處理器單元。(譯注:還有以太網控制器、DDR控制器以及高速總線的串行收發器,這些單元都是固化電路,不可編程的)通過這些預先定義并固化在硅片上的額外單元,單片 FPGA 便有能力構成整個完整的系統。

FPGA 中的邏輯以及布線單元的可重構由編程節點控制(programming points),基于反熔絲(antifuse)、SRAM 或者 FLASH 技術,一般來說 SRAM FPGA 對于可重構計算是一個適宜的選擇,SRAM 也是目前商用 FPGA 的主流技術。在 SRAM FPGA 中,每個布線或者邏輯單元的功能都由存儲于 SRAM 介質中的內容決定。整個器件中的 SRAM 內容可通過一個配置文件或者比特流(bitstream)進行配置,編程為用戶定義的功能。因此,整個配置過程可以快速地進行,并且不需要一些固化步驟。(譯注:SRAM 的寫入擦除均十分快速且易于進行)開發者能夠很方便地在自己的工作臺上對器件進行編程。哪怕 FPGA 器件已經安裝于終端產品中,編程也十分容易進行。這就是為什么 FPGA 會被稱為現場可編程(Field programmable)的原因,并區別于那些僅在生產時可編程的掩膜可編程(mask programmable)器件,這些器件的可編程只能在產線上通過相應設備進行,無法在客戶現場完成。

譯注:Field programmable 指產品出了問題,帶著電腦去用戶現場調試,干過這事兒都懂:苦差啊。

因為 FPGA 的定制只需要將相應的內容寫入到片上的存儲中,因此和編譯、然后將程序加載到計算機中運行這一軟件開發流程相似。FPGA 相對應的流程是創建與 FPGA 電路對應的比特流、然后將比特流寫入到器件中(可見圖 I.2)。盡管有多種建立 FPGA 電路的方法,可以借助工具將軟件代碼(譯注:HLS)、原理圖或者其他格式的數據轉換為電路。FPGA 開發者一般還是通過硬件描述語言(HDL,Hardware description language)來構建一個應用,比如 Verilog 和 VHDL。由 HDL 描述的電路經過一系列步驟轉換為可映射至 FPGA 器件的邏輯,這些步驟包括:

邏輯綜合(logic synthesis),將高級語法以及行為級描述,轉換為邏輯門網表。

工藝映射(technology mapping ),將若干邏輯門為劃分至一個邏輯組,并將邏輯組高效地映射于 FPGA 的邏輯資源。

布局布線(placement & routing,P&R),將邏輯組指定至器件上某個具體的邏輯單元,并按照用戶定義連接各個邏輯單元之間的端口。

生成比特流(bitstream generation),將布局布線后的信息生成為一個二進制文件,用于恰當地配置器件邏輯單元與布線資源。

在設計編譯完成后,我們可以通過比特流將 FPGA 器件編程為對應于某個計算應用的平臺。一般通過主機上的處理器完成比特流的下載工作。或者可以將預先編程完成的存儲介質連接至 FPGA 的配置管腳。無論如何,FPGA 在每次上電之后都需要讀取比特流進行配置。或者在運行時,用戶可以按需控制器件重新下載比特流進行重配置。一旦 FPGA 配置完成,那么就會像一個具有特定功能的數字電路一樣工作。

因為 FPGA 同時具有軟件靈活性與硬件高性能兩項特性,FPGA 開發者的思路需要區別于純粹的軟件或者硬件開發者。軟件開發者一般開發串行執行的程序,最大化利用微處理器的性能,來執行一系列的指令

譯注:假設程序員只有一個單獨的處理核,并且目標運算的指令數量固定。軟件程序員的目標就是降低相同數量指令的執行時間,換句話說,減少微處理器的等待時間。

但是在高質量的 FPGA 設計開發中需要考慮空間的并行性,即使用芯片上的多路資源并行計算,盡可能地減少運算整體時間。

譯注:假設資源是無限的,對于目標運算,FPGA開發者的目標是盡可能實現指令的并行,將指令盡可能地分配到多個并行處理單元上。

對于 ASIC 等硬件開發人員來說,因為會從硬件電路實現出發,所以在硬件設計中具有一定優勢(譯注:在設計階段實現更好的 PPA,Performance/Power/Area)。但是 FPGA 的靈活特性能夠給開發者帶來 ASIC 或者其他固化器件設計中不存在的新機遇。FPGA 設計可以更快地進行新功能的迭代和部署,甚至在現場重新編程。因此,FPGA 設計不需要 ASIC 開發那么大規模的設計團隊,所需的驗證工作也會更少 。此外,FPGA 的動態可重編程特性使一些設計成為可能。比如,在運算過程中設計可以根據當前的外部需求的動態改變重編程,動態地優化自身的結構。或者通過定時對自身功能進行重構,在小型的器件上時分復用功能,實現規模更大的設計。但是有一點,FPGA 相比 ASIC 運行速度要低得多,并且容量也小得多,設計者需要細致地對設計進行優化,以契合目標器件。

圖 I.2 典型的 FPGA 開發流程示意圖

FPGA 是一項擁有獨立機遇以及挑戰的器件,是一個非常靈活的硬件平臺。本書《可重構計算:可重構計算的原理與實踐》旨在介紹基于 FPGA 平臺的各個方面,這些方面可能是積極的,也有可能是面臨問題的,本書主要包括 6 個部分:

第一部分介紹硬件器件,包括 FPGA 以及那些為可重構專門優化的器件(章 1-4)

第二部分關注可重構計算平臺的編程實現,包括編程語言以及編程模型(章 5-12)

第三部分關注 FPGA 開發流程的軟件,包括圖 I.2 中每個步驟的詳情(章 13-20)

第四部分關注面向應用的 FPGA 設計,討論范圍包括:如何最高效地利用器件的邏輯資源(章21-26)這部分可以認為是 FPGA 開發者的最后一課了,因為學完的讀者應該已經完全掌握了 FPGA 開發與軟件編程、ASIC 設計之間的區別。

第五部分是一系列案例學習,闡述了可編程器件在各領域的應用(章27-35)

第六部分包括了一些進階主題,比如可重構計算的理論模型以及衡量標準。此外還包括了可重構的缺陷、容錯(fault tolerance)等主題以及可重構計算與納米技術之間潛在的協同作用。(章36-38)

在完成了所有 38 個章節的閱讀后,讀者會發現 FPGA 當前存在一些重大挑戰。但更重要的是,可重構器件為計算科學帶來的獨特機遇與收益將遠超為了克服這些挑戰所付出的努力。

原文標題:可重構計算:基于FPGA可重構計算的理論與實踐

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601843 -

計算

+關注

關注

2文章

445瀏覽量

38736 -

可編程邏輯

+關注

關注

7文章

514瀏覽量

44072

原文標題:可重構計算:基于FPGA可重構計算的理論與實踐

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA的重構方式

基于FPGA的可重構系統結構分析

【懸賞100塊】如何實現FPGA可重構計算(Android平臺)

可重構計算(Reconfigurable Computing)

可重構技術分析及動態可重構系統設計

基于FPGA硬件平臺的可重構系統調度算法詳解

可重構和自適應計算:理論與應用

可重構計算:基于FPGA可重構計算的理論與實踐 1.器件架構 譯文(一)

基于FPGA的可重構計算平臺設計

基于FPGA的可重構計算平臺設計

評論