本文在詳細介紹了電磁干擾理論知識的基礎上,分析了無刷直流電機控制系統 電磁兼容性軟、硬件設計,電磁兼容性設計有利于提高系統的抗干擾能力,提高系統的可靠性和穩定性。

1 電磁干擾

熟悉和了解常見的電磁干擾源是發現和解決電磁干擾問題的關鍵之一。電磁干擾可分為自然和人為兩類。所謂自然的是指自然界所固有的與人類的活動無關的電磁干擾現象。所謂人為的是指由于人類的工業和社會活動所產生的電磁干擾。

1.1 電磁干擾源

諸如雷電的放電現象,電動機的TTL邏輯元件、動態RAM、電源、震蕩器件及變壓器等在工作時都會產生高頻電磁波或者噪音,嚴重影響電動機的正常工作。

1.2 電磁干擾能量的耦合途徑

耦合是指電路、設備、系統與其它電路、設備、系統間能量的聯系。各種電磁騷擾源通過耦合傳輸電磁能量到敏感設備。耦合途徑有兩種方式:傳導耦合與輻射耦合。

1.2.1 傳導耦合

傳導耦合是通過電源線、信號線、互聯線、接地導體等連接通道進行耦合。按耦合方式又可劃分為公共阻抗耦合、電容性耦合、電感性耦合三種基本方式。實際中,這三種方式是同時存在共同作用的。

1)公共阻抗耦合

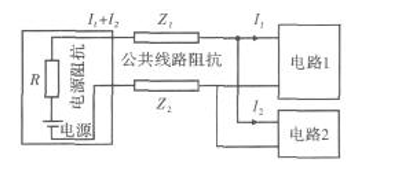

當電路電流經過一個公共阻抗時,一個電路的電流在該公共阻抗上形成的電壓就會影響到另一個電路。公共電源阻抗耦合模型及其等效電路如下:

圖1 公共電源阻抗耦合模型

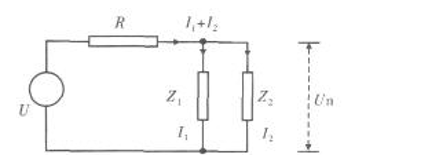

圖2 公共電源阻抗等效電路

圖2中將圖1中的電源阻抗及公共線路阻抗合并表示為R,U為理想電壓源,Z1、Z2分別為電路1和電路2的阻抗。根據等效電路有:

由上式可以看出由于R的存在,電路1電源電流的任何變化都會影響電路2的電源電壓。若R=0,則U1=U2=U,即電路1和電路2無公共阻抗耦合。降低電路1與電路2間的公共阻抗耦合即減小電源阻抗和公共線路阻抗。一方面可將電路的電源引線靠近電源輸出端,從減小電源線長度的方式來減小公共線路阻抗;另一方面可采用穩壓電源將電源內阻降低。

2)電容性耦合

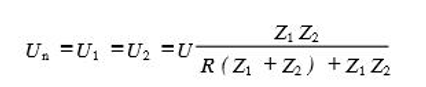

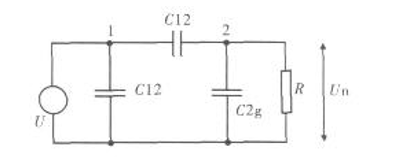

電容性耦合是由兩條電路間的電場相互作用所引起的,其耦合模型及等效電路如下:

圖3 電容性耦合模型

圖4 電容性耦合等效電路

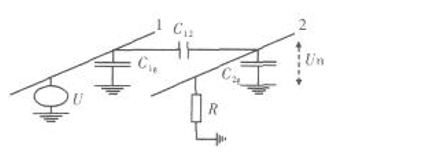

C12是導體1與導體2之間的分布電容,C1g是導體1與地之間的電容,C2g是導體2與地之間的電容,R是導體2與地之間的電阻,U1是作為騷擾源的導體1的電壓,電路2為受干擾電路,Un是線路2與地之間產生的騷擾電壓。

根據等效電路則有:

式(1) 表明電容性耦合的騷擾作用相當于在導體2與地間接了一個幅值In=jwC12U的電流源。在騷擾源電壓和頻率恒定的情況下要減小耦合干擾,一方面可使敏感電路在較低的電阻值上工作,即通過減小R的方式來減小Un;另一方面導體通過合適地取向、屏蔽或隔離的方式減小C12來達到減小Un。

式(2) 表明在高阻抗的情況下電容性耦合騷擾作用只與C12、C2g有關,且此時產生的騷擾作用要大的多。

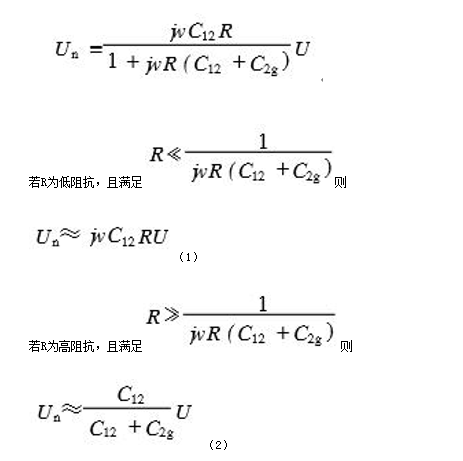

3)電感性耦合

電感性耦合是由兩電路間的磁場相互作用引起的,其耦合模型及等效電路如下:

其中S為回路面積,B是角頻率為的正弦變化磁通密度的有效值。由上式可知,可通過減小B、S、cosθ的方式減小電感性耦合騷擾的目的。

1.2.2 輻射耦合

輻射耦合是以電磁場的形式將電磁能從騷擾源經空間傳輸到敏感設備。空間中除了騷擾源有意輻射之外,還存在許多無意輻射的電磁波,而處在這一電磁場中的導體都能感應出電壓。因此,輻射干擾可通過天線、導線、閉合回路等方式對

電動機控制系統進行干擾。

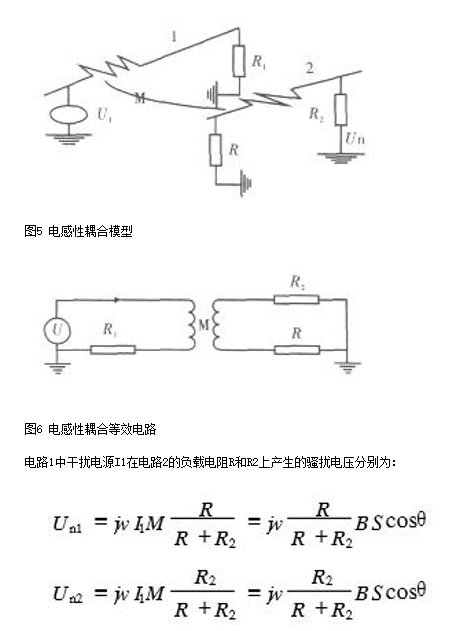

2 系統硬件的電磁兼容的設計

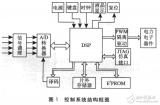

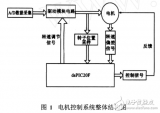

DSP電路的工作頻率很高,芯片管腳很密,在與模擬器件一起進行數模混合設計時,對PCB版的設計要求很高。以下為設計時必須遵守的準則和要求。

隨著電子器件的小型化及封裝密集化,有必要采用多層印刷電路板,其中包括單獨的數字地層、電源層及其其它信號層。在布線時,單獨設置的電源層有利于電路板元器件的布放;采用地層則不僅省去了大量器件管腳接地的工作量,而且可以有效地改善數字地線的質量。但應注意,在布孔、布線時應考慮通孔焊盤和過孔會將地層打斷,過多的通孔會影響地層的抗干擾效果。本系統采用了四層板結構,分別為地層、電源層和兩面元件層。在繪制PCB也特別考慮了通孔焊盤和過孔的使用, 將盡可能多的網絡在元件層布通。

由于基于DSP的電動機控制系統使用的微處理器內核采用獨立電源供電模式,因此對于具有144個管腳的TSM320LF2407A,需要較多的電源解耦電容,為了節省空間,減小通孔數目,系統采用貼片電容,達到了較好的解耦效果。

接地應遵循的基本原則是:數字地、模擬地、屏蔽地應該合理接地,不能混用。盡可能的使接地電路各自形成回路,減少電路與地線之間的電流耦合。合理布置地線使電流局限在盡可能小的范圍內,并根據地電流的大小和頻率設計相應寬度的印刷電路和接地方式。DSP的A/D采樣模擬電源引腳VCCA和VSSA必須區別于任何數字電壓電源引腳,避免數字干擾信號通過地線耦合。同時,A/D轉化器的模擬地線采用單點接觸,數字地與模擬地在電源處連接并在此處接大地。 VCCA和VSSA模擬引線在印刷電路板布線時應盡可能的短,以使二者正確匹配。

3 軟件電磁兼容設計

TSM320LF2407A有豐富的指令集、極高的運行速度及軟件看門狗(watchdog)和實時中斷(RTI)模塊,這些特點都為軟件抗干擾提供了良好的條件。本系統主要采用以下幾種軟件抗干擾設計。

3.1軟件陷阱法

由于干擾,往往會導致運行程序進入程序存儲器的空白區(即無指令區),這種現象叫做程序“跑飛”。因此在各個子程序之間、各功能模塊之間和所有空白處,都寫上連續3個空操作(nop),后接一無條件轉移指令,一旦程序跑飛到這些區域,就會自動返回執行正常程序。即:

Nop

Nop

Nop

LJMPADDRESS:ADDRESS指定地址;

3.2 程序的冗余設計

在程序存儲器的空白區域,寫入一些重要的數據表和程序作為備份,以便系統被破壞時仍有備份參數和程序維持系統正常工作。由于LF2407A的數據存儲以數據頁為基準,如果對不同數據頁的數據進行操作而不指定相應的數據頁,會導致程序跑飛。因此需要對程序未使用滿的數據頁進行填充,防止數據頁混亂導致程序的系統誤操作。

3.3 軟件看門狗設計

看門狗定時器(WDT)又稱監視定時器,可使微機系統從故障中恢復過來。在微機系統啟動時,也啟動WDT。它將對機器的狀態周期進行計數,每一個狀態周期計數器加1,當計數器溢出時,能自動的將復位引腳的電平拉低至少兩個狀態周期的時間,這個復位信號使得DSP復位。在正常工作時,定期的用軟件去復位 WDT,而不會使WDT溢出造成系統復位。可是,如果程序一旦“跑飛”進入死循環或誤區,這時軟件就不會復位WDT,從而使WDT的計數達到溢出而使系統復位。系統復位后又從000H單元開始執行程序,這樣就可把“跑飛”的程序拉回到正常的程序中。

4 結論

基于 DSP的電機控制系統能否安全工作,是電磁兼容設計的關鍵。電機控制系統的設計應根據系統的工作環境、技術指標、工藝復雜程度、成本等因素,綜合考慮電磁兼容性設計。電機控制系統采用上述電磁兼容設計,工作穩定可靠,故障率低,達到了預期效果!

-

電磁干擾

+關注

關注

36文章

2295瀏覽量

105314 -

電磁兼容性

+關注

關注

6文章

413瀏覽量

33684 -

電機控制系統

+關注

關注

0文章

51瀏覽量

14146

發布評論請先 登錄

相關推薦

設計方案:基于單片機AT89S52的直流電機PWM調速控制系統

常規的滑板車控制系統硬件設計方案

電力電子裝置控制系統的DSP設計方案

基于DSP的電力電子裝置控制系統設計方案

基于DSP的轉子磁場定向控制系統設計方案

基于DSP的電機控制系統設計方案

基于DSP的電機控制系統設計方案

評論