前言

2022年3月,芯片制造商英特爾、臺積電、三星,聯合日月光、AMD、ARM、高通、谷歌、微軟、Meta(Facebook)等十家行業巨頭共同推出了全新的通用芯片互聯標準——UCle。

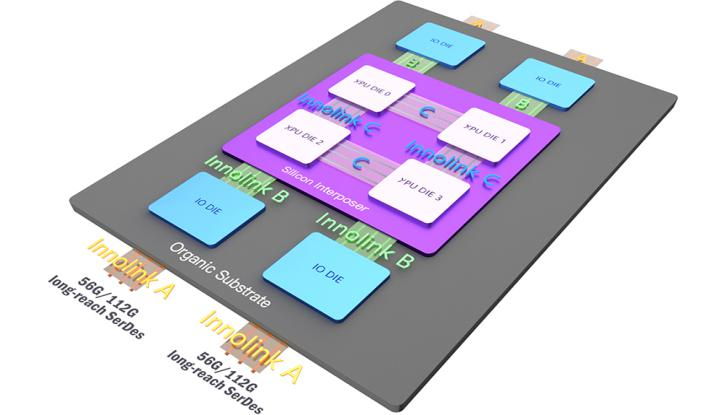

幾乎同一時間,中國IP和芯片定制及GPU賦能型領軍企業芯動科技宣布率先推出國產自主研發物理層兼容UCIe國際標準的IP解決方案-Innolink Chiplet,這是國內首套跨工藝、跨封裝的Chiplet連接解決方案,且已在先進工藝上量產驗證成功!

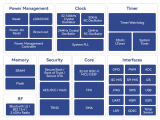

▲ Innolink Chiplet架構圖

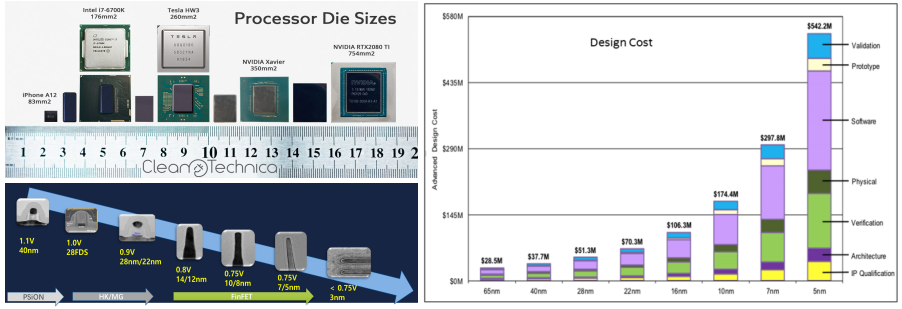

隨著高性能計算、云服務、邊緣端、企業應用、5G通信、人工智能、自動駕駛、移動設備等應用的高速發展,算力、內存、存儲和互連的需求呈現爆炸式增長,但同時,先進工藝芯片迭代也面臨著開發難度大、生產成本高、良品率低的窘境,即先進制程工藝下芯片面臨著性能與成本的矛盾,Chiplet技術在這一背景下得到快速發展。

▲ 制程工藝發展和晶體管密度增加導致開發成本急劇上升

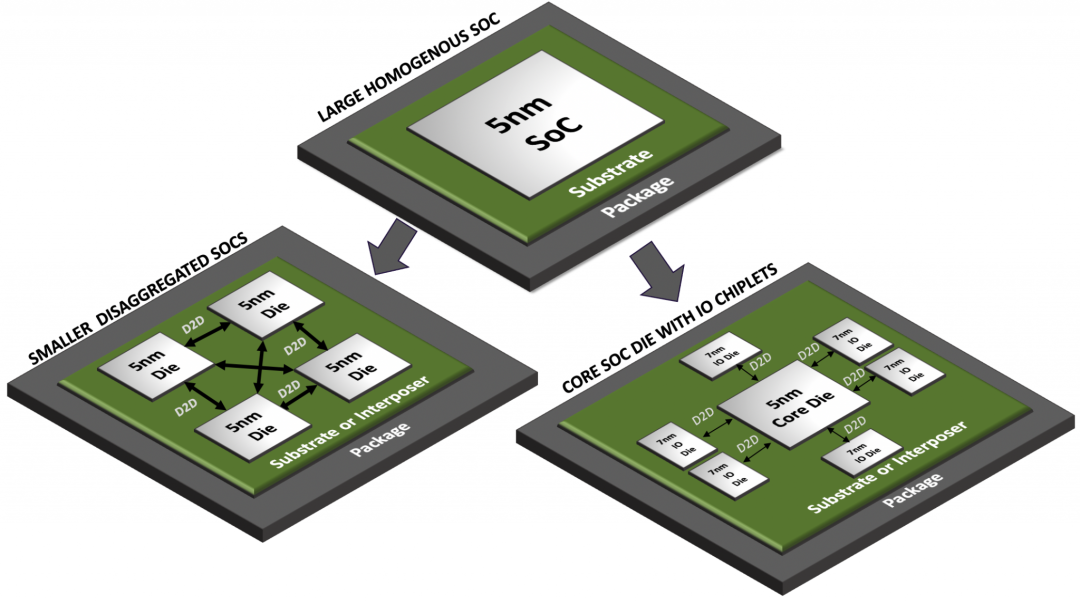

Chiplet技術的核心是多芯粒(Die to Die)互聯,利用更短距離、更低功耗、更高密度的芯片裸die間連接方式,突破單晶片(monolithic)的性能和良率瓶頸,降低較大規模芯片的開發時間、成本和風險,實現異構復雜高性能SoC的集成,滿足不同廠商的芯粒之間的互聯需求,達到產品的最佳性能和長生命周期。

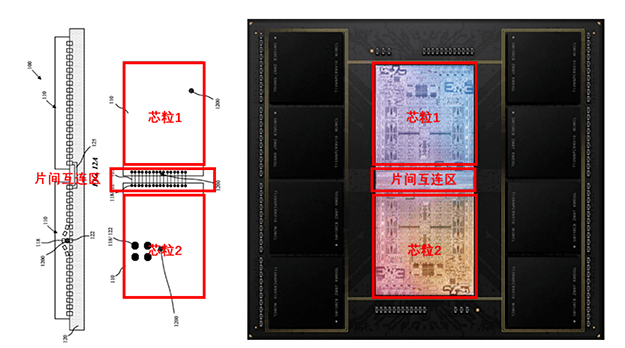

▲ Chiplet核心技術是多芯粒互聯

近年,AMD、蘋果和英偉達等國際巨頭都發布了標志性的Chiplet旗艦產品,并在各個應用領域取得極大成功,進一步驗證了Chiplet技術的可行性和發展前景,使得Chiplet互聯這一核心技術日益受到市場追捧!

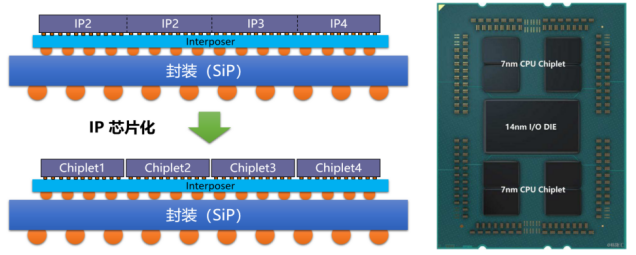

▲ 多芯粒互聯的Chiplet技術是實現高性能異構系統的發展趨勢

▲ 蘋果自研M1 Ultra芯片應用Chiplet技術實現性能翻倍

Chiplet的早期發展協議混亂

各個公司制定自己的私有標準

此前,眾多的芯片廠商都在推自己的互聯標準,比如Marvell在推出模塊化芯片架構時采用了Kandou總線接口;NVIDIA擁有用于GPU的高速互聯NV Link方案;英特爾推出了EMIB (Embedded Die interconnect bridge)接口;臺積電和Arm合作搞了LIPINCON協議;AMD也有Infinity Fabrie總線互聯技術等等。 芯動科技奮起直追緊隨其后,2020年在國內率先推出自主研發的Innolink Chiplet標準并實現授權量產。

Chiplet技術核心就是Die to Die互聯,實現大帶寬下的多芯片算力合并,形成多樣化、多工藝的芯片組合。顯然,如果各家芯片廠商都在推自己的標準,這將導致不同廠商的Chiplet之間的互聯障礙,限制Chiplet的發展。因此,實現各個芯粒之間高速互聯,需要芯片設計公司、EDA廠商、Foundry、封測廠商等上下游產業鏈協調配合、建立統一的接口標準,從而實現Chiplet技術的量產應用并真正降低成本,加速整個Chiplet生態的發展。于是,UCIe標準應運而生。

UCIe的建立

將有力推動Chiplet連接標準發展

前不久,UCIe標準發布引起了業界高度關注與熱議,因為這是由一條比較完整的產業鏈提出的開放的、可互操作性的標準,能有效解決當前先進工藝芯片產業上下游發展的難題,降低成本、提升性能。

Universal Chiplet Interconnect Express (UCIe) 是一個開放的、行業通用的Chiplet(芯粒)的高速互聯標準,由英特爾、AMD、ARM、高通、三星、臺積電、日月光、Google 、Meta、微軟等十大行業巨頭聯合推出。它可以實現小芯片之間的封裝級互連,具有高帶寬、低延遲、低成本、低功耗等優點,能夠滿足包括云端、邊緣端、企業級、5G、汽車、高性能計算和移動設備等在內的整個計算領域,對算力、內存、存儲和互連日益增長的高需求。通俗來講,UCIe是統一標準后的Chiplet,具有封裝集成不同Die的能力,這些Die可以來自不同的晶圓廠,也可以是采用不同的設計和封裝方式。

Innolink Chiplet方案解讀

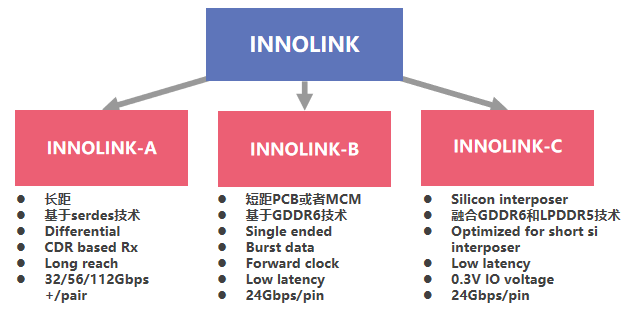

就在Ucle標準發布后兩周,芯動科技就宣布推出首個國產自主研發物理層兼容UCIe標準的IP解決方案-Innolink Chiplet。芯動Chiplet架構師高專表示:芯動在Chiplet技術領域積累了大量的客戶應用需求經驗,并且和臺積電、intel、三星、美光等業界領軍企業有密切的技術溝通和合作探索,兩年前就開始了Innolink 的研發工作,率先明確Innolink B/C基于DDR的技術路線,并于2020年的Design Reuse全球會議上首次向業界公開Innolink A/B/C技術。

得益于正確的技術方向和超前的布局規劃,Innolink 的物理層與UCIe的標準保持一致,成為國內首發、世界領先的自主UCIe Chiplet解決方案。

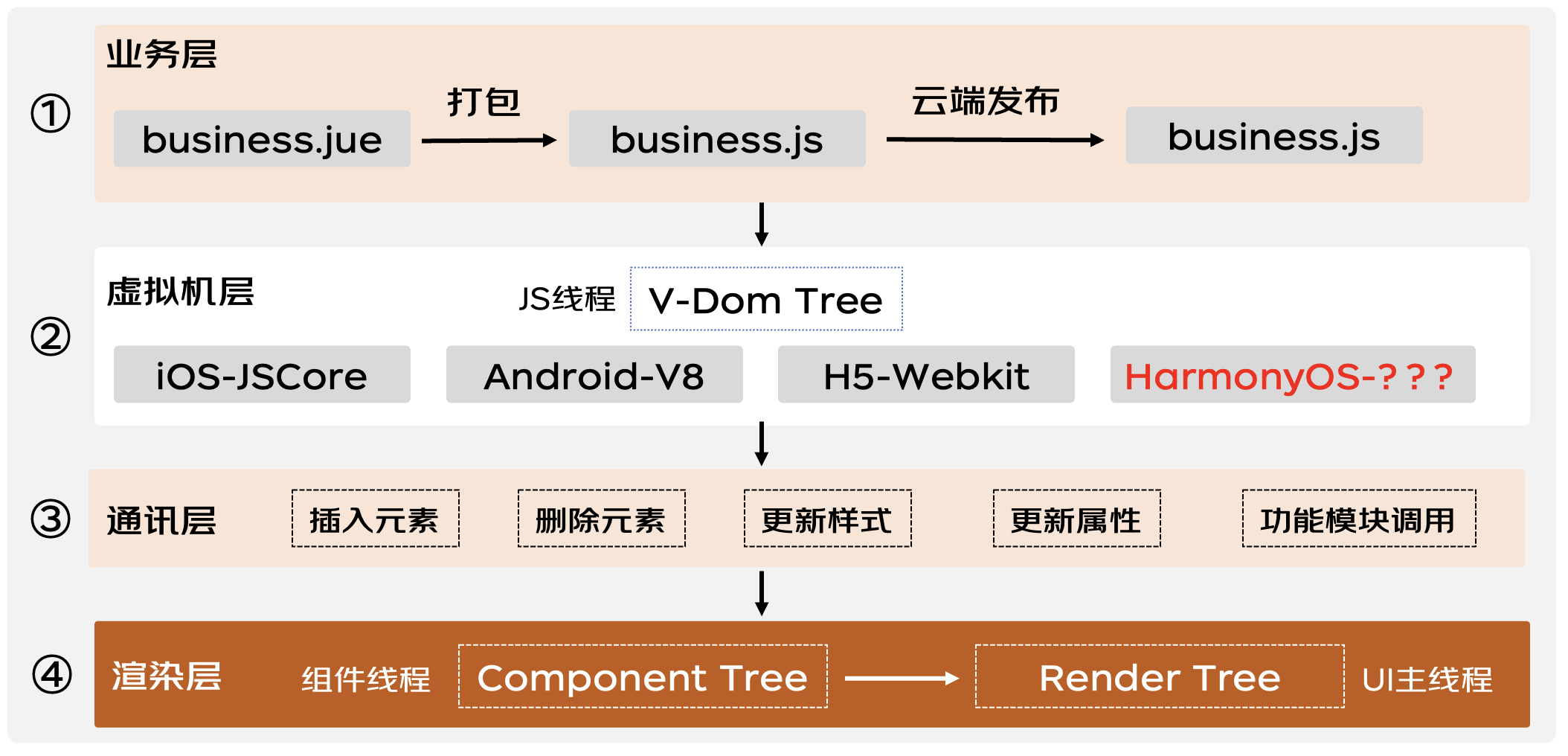

▲ Innolink A/B/C實現方法

Innolink Chiplet的設計思路和技術特點:

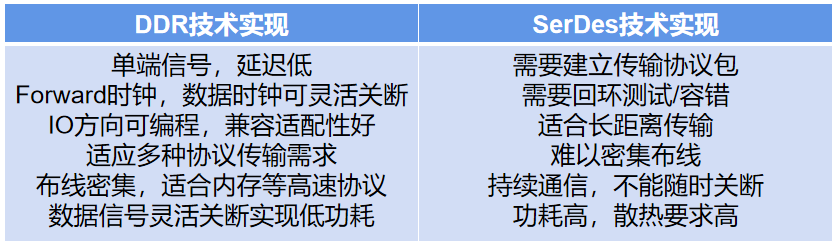

1.業界很多公司認為Chiplet跨工藝、跨封裝的特性,會使其面臨復雜的信號衰減路徑,所以普遍使用SerDes差分技術以應對這一問題。芯動基于對Chiplet應用場景和技術趨勢的深刻理解,以及在DDR技術領域的絕對領先,認為相較于SerDes路線,DDR技術更適合Chiplet互聯和典型應用,而且不同封裝場景需要用到不同的DDR技術方案。

2.Chiplet(Die to Die) 在短距PCB、基板、Interposer上連接時,路徑短、干擾少、信號完整性好,此時采用DDR技術路線在延時功耗和帶寬密度上更具優勢。在短距離PCB、 基板、Interposer平臺上,DDR對比SerDes的優勢如下:

Chiplet的核心目標就是高密度和低功耗,DDR技術滿足多芯粒互聯的高密度、低功耗、低延遲等綜合需求,可使多芯粒像單芯粒一樣工作,單芯粒總線延展至多芯粒。因此,芯動綜合考慮SerDes和DDR的技術特點,在Innolink-B/C 采用了DDR的方式實現,提供基于GDDR6/LPDDR5技術的高速、高密度、高帶寬連接方案。

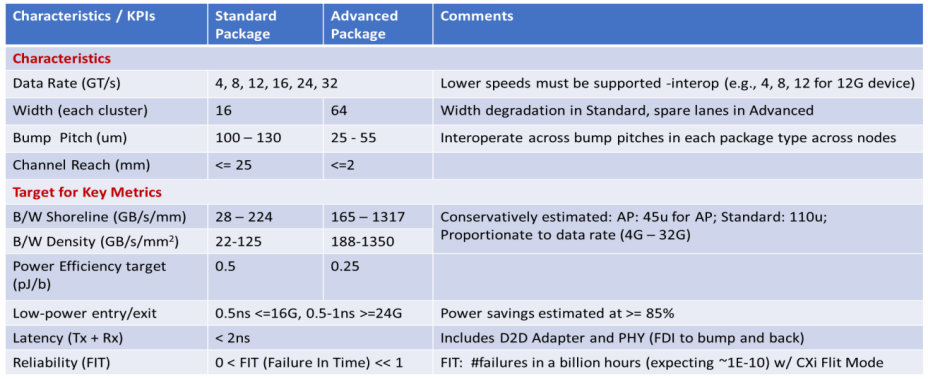

3.標準封裝使用MCM傳統基板作為Chiplet互聯的介質,具備成本便宜等特點,是對成本較為敏感的Chiplet應用場景首選;先進封裝如Interposer,具備密度高、良品率低、成本高等特點,則是對價格不敏感的高性能應用場景首選。在UCIe定義正式發布前,Innolink-B/C就提前實現了這兩種封裝場景的應用,驗證了其對市場前景和Chiplet技術趨勢的準確判斷。

▲UCIe定義 不同封裝標準的主要性能指標

4.針對長距離PCB、線纜的Chiplet連接,Innolink-A提供基于SerDes差分信號的連接方案,以補償長路徑的信號衰減。

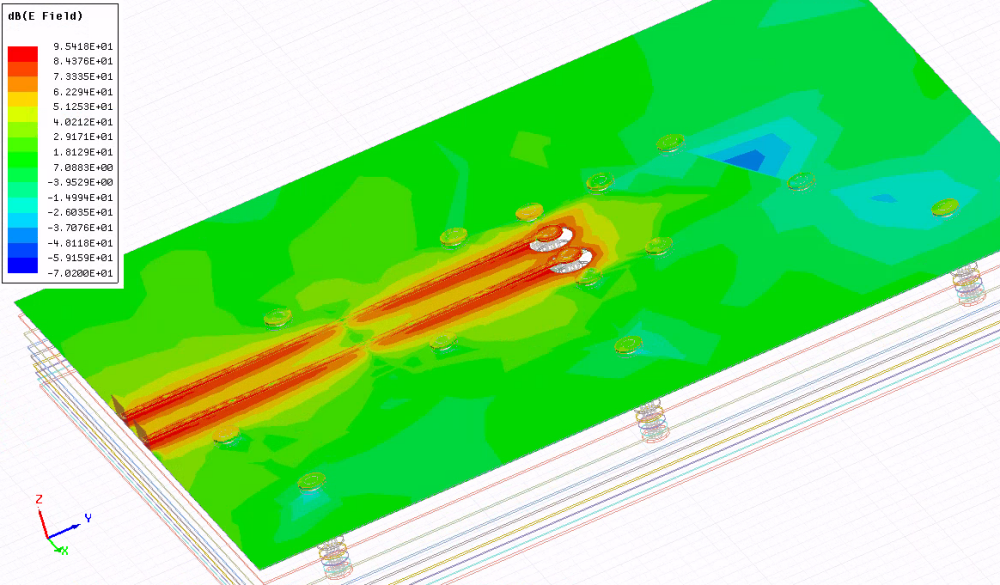

5.總的來看,Innolink-A/B/C實現了跨工藝、跨封裝的Chiplet量產方案,成為業界領先!圍繞著Innolink Chiplet IP技術,芯動同時還提供封裝設計、可靠性驗證、信號完整性分析、DFT、熱仿真、測試方案等整套解決方案!

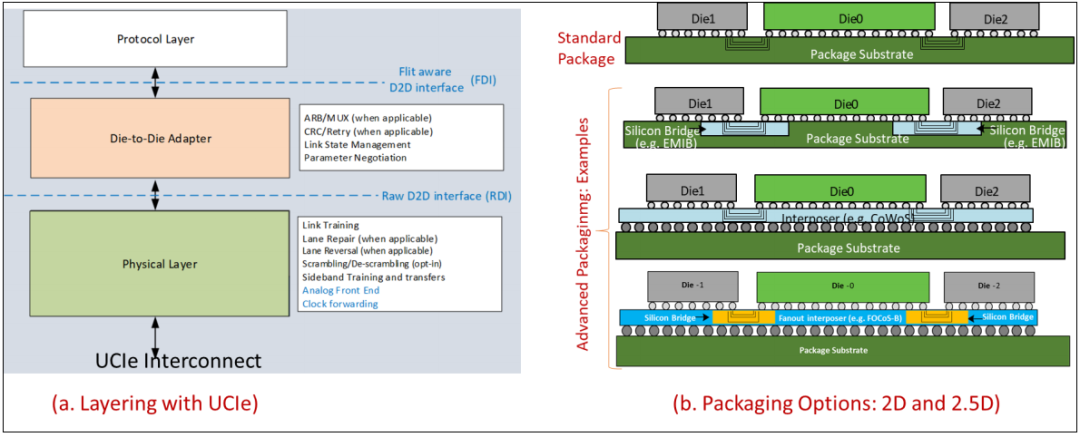

▲ Innolink Chiplet的設計包含了UCIe的Chiplet連接先進、標準封裝定義

圖中顯示UCIe分了3個層次,Protocol Layer協議層、die to die Adapter互聯層、Physical Layer物理層。其中協議層就是常用的PCIE、CXL等上層協議,底層的Die to Die和PHY物理層,即是和Innolink同樣的實現方式。

總結:芯動準確地把握了Chiplet技術方向,并前瞻性地完成設計驗證,與后來推出的UCIe技術方向一致,為Innolink 兼容UCIe標準奠定基礎,成為業界領先方案。

這聽起來像押中高考大題的故事,其實Innolink背后的技術極為復雜,正因為芯動掌握了高速SerDes、GDDR6/6X、LPDDR5/DDR5、HBM3、基板和Interposer設計方案、高速信號完整性分析、先進工藝封裝、測試方法等等世界領先的核心技術,并且經過大量客戶需求落地和量產驗證迭代。博觀而約取,厚積而薄發,“押中題”無疑是是芯動技術團隊長期投入和耕耘的成果!

芯動準備了滿滿一桌的大餐

等著UCIe這個客人上桌!

Innolink Chiplet是芯動先進IP之集大成者,代表著國內乃至世界領先水平,聞之不如見之,我們來盤點一下其內部實現的基礎技術。

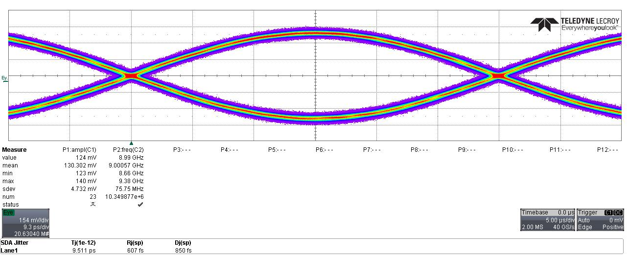

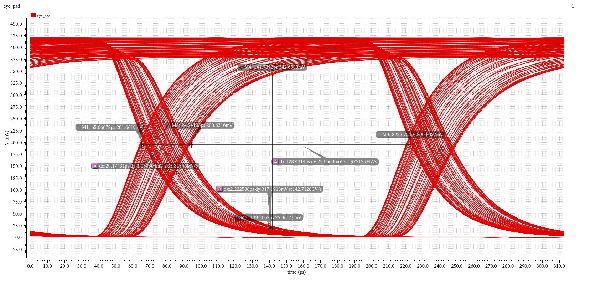

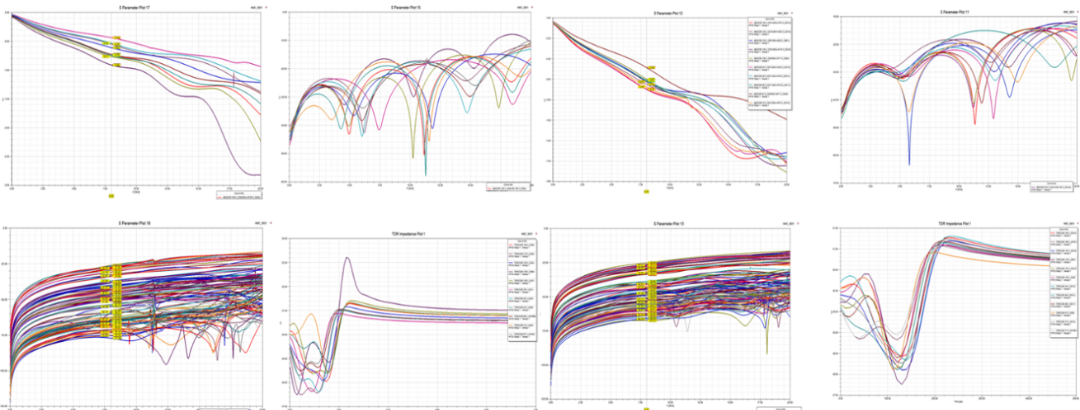

▲ 18Gbps GDDR6 單端信號量產驗證

▲ 21Gbps PAM4 DQ eye, single ended

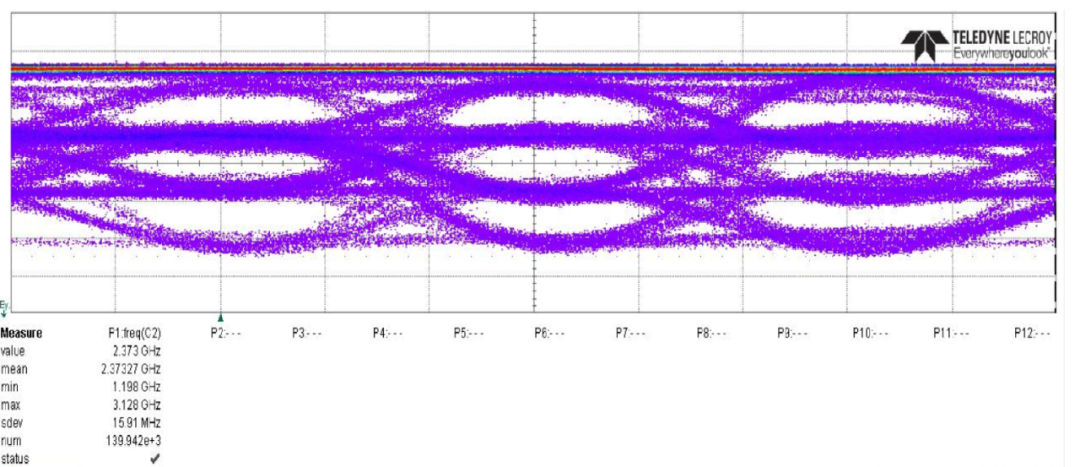

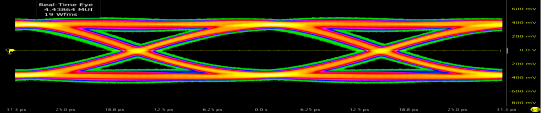

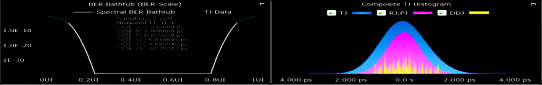

▲ HBM3 6.4Gbps 高速眼圖

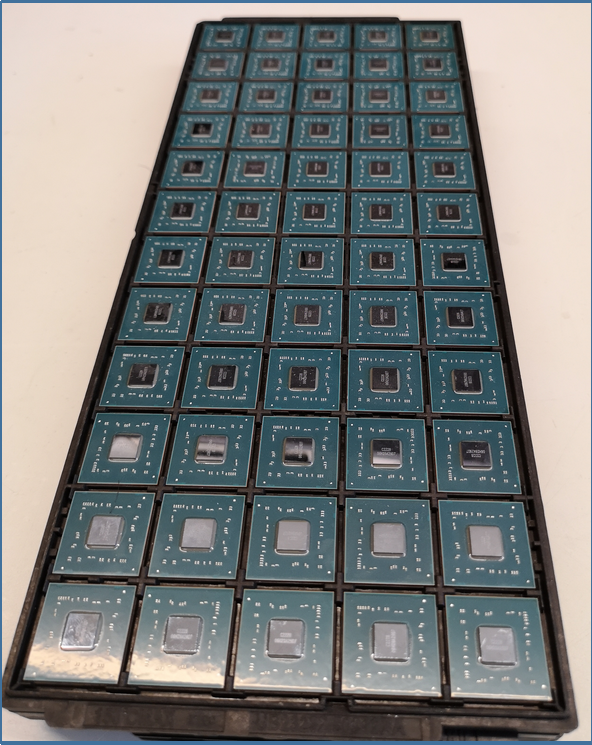

▲ 全球首個GDDR6/6X combo IP量產

▲ 32/56G SerDes眼圖

▲ 風華1號4K高性能GPU應用Innolink Chiplet實現性能翻倍

▲ 先進封裝信號完整性分析

▲ 封裝熱效應仿真

看到這些賞心悅目的IP驗證測試眼圖,相信大家對Innolink Chiplet有了更加客觀的認知。追本溯源,這些成果反映的另一問題也值得探討,為什么芯動能在這么多先進技術上取得如此耀眼的成績?

為什么要做先進IP

有哪些挑戰和困難?

芯動科技的CEO敖海先生是技術出身,長期保持和一線研發工程一起討論架構、改代碼、調電路、定方案的習慣,從領導人至一線員工,全公司都秉承踏實進取、勇于創新、務實精進的作風。見微知著,芯動研發團隊能持續攻克一個個技術難關、攀登一座座行業高峰也就不奇怪了。正因于此,芯動才能保持對市場的敏銳判斷和技術發展的持續領先!

▲ CEO親自參與研發工作,帶領團隊勇爭領先!

敖海認為,現階段先進工藝芯片技術迅速發展、高性能應用需求急劇增加,只有不畏挑戰迎難而上、搶先占領技術高地,在Chiplet等先進IP技術上對標海外巨頭,并在某些領域實現彎道超越,才能在市場上站穩腳跟,有效賦能國產半導體發展!

首發先進IP技術具備很多優勢,可以快速贏得業界認可、第一時間導入客戶需求并設計驗證、廣泛獲得Foundry和封測等上下游的大力支持。在市場應用成熟時,還可以讓廣大芯片客戶用上量產驗證的、可靠安全的IP,從而根據新的升級方向迅速實現技術迭代,進一步推動業務增長。一步領先、步步領先,從IP切入是極具實際意義的。

當然,首發推出先進工藝IP面臨很多困難:

1.沒有參照對象,試錯成本高。

第一個吃螃蟹的人,先進道路的開拓者,總要付出加倍的努力。在很多大的技術節點上并沒摸石頭過河的說法,需要不斷的摸索嘗試。通俗點講就是一個個坑踩個遍,踩結實了,路就平了。

2.對團隊要求高。

一個先進IP,從數字到模擬、后端到工藝、流片到封測,每個環節都要資深的技術人員,芯動經過16年的積累,打造一支技術過硬的隊伍,后來居上,面對國外廠商的先發優勢毫不退讓,用實力贏得全球客戶認可。

3.先進工藝流片驗證成本高。

先進工藝的IP流片驗證成本很高昂,設計工時、FinFet工藝MPW或者流片費用、封測等累加,每次驗證的費用輕輕松松破百萬美元。

某種意義上,芯動在先進IP領域獲得的優勢和業界認可,以及6大合作晶圓廠在工藝、流片成本、產能上給予的巨大幫助,都是做先進工藝IP的好處。

先進IP的重要意義

有和沒有先進IP區別是很大的,有先進IP能夠使市場更加理性,同時滿足國產高端芯片自主可控、技術迭代的迫切需求!

芯動的先進IP技術,一方面引領行業技術的創新,塑造半導體企業的全球化長遠發展視野,另一方面填補國內高性能芯片的應用空白,助力國內高端芯片發展。

芯動16年來重兵投入全球先進工藝、專注國產自主IP研發,在高性能計算平臺、多媒體終端&汽車電子平臺、IoT物聯網平臺等應用領域打造了核心優勢,超過200次的流片紀錄、逾60億顆授權量產芯片、10億顆以上高端定制SoC量產,默默耕耘、腳踏實地,為賦能高端芯片做出重要貢獻!

原文標題:量產驗證成功!國產首個物理層兼容UCIe國際標準的Chiplet解決方案正式發布

文章出處:【微信公眾號:芯動科技Innosilicon】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

芯片

+關注

關注

454文章

50460瀏覽量

421975 -

芯動科技

+關注

關注

2文章

92瀏覽量

9876 -

chiplet

+關注

關注

6文章

419瀏覽量

12561

原文標題:量產驗證成功!國產首個物理層兼容UCIe國際標準的Chiplet解決方案正式發布

文章出處:【微信號:Innosilicon,微信公眾號:芯動科技Innosilicon】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cadence推出基于Arm的系統Chiplet

揭秘動態化跨端框架在鴻蒙系統下的高性能解決方案

騰訊云與芯動科技推出聯合解決方案,推動芯片行業創新發展

創新型Chiplet異構集成模式,為不同場景提供低成本、高靈活解決方案

OPA1641是否可做PA級跨阻放大器?

OPA847進行跨阻放大震蕩的原因?

超低噪聲跨阻放大器如何選型?

Microchip推出集成作動電源解決方案旨在簡化航空業向多電飛機轉型

廣汽埃安推出國內首個無圖純視覺智能駕駛解決方案—Garcia智駕系統

架空線路圖像視頻監測裝置(三跨視頻)|不可忽視的“三跨”

泰凌微宣布推出國內首顆工作電流低至1mA量級的無線SoC芯片TLSR925x

芯動科技推出國內首套跨工藝、跨封裝的Chiplet連接解決方案

芯動科技推出國內首套跨工藝、跨封裝的Chiplet連接解決方案

評論