PWM與PDM是現在運用非常多的電路,現在的MCU一般都內帶硬件PWM,用特殊的定時器電路實現。所以一般不會像我們當年那樣用軟件來做PWM。因此,上述算法的一個用處,是用來做硬件PDM。用PSoC的UDB Datapath來做,就是本算法硬件實現的例子。

十來年前,有幾十個宏單元的CPLD就可以做硬件PDM。但是,如果不是對速度和精度有特別要求,MCU外再掛一塊CPLD做的硬件PDM“拖油瓶”,好像還是不大合算。現在的FPGA,連MCU都擺進去了,再添上點硬件PDM,就是小意思了。所以,算法就有了用武之地。再說,用該算法做出硬件PDM,恐怕比定時器式的PWD所占用的資源還要小。自從出現Cypress的PSoC3后(以及后來的PSoC5、LP及PSoC4),我們就可以很輕易地把這種算法用MCU內的硬件做出來。第一篇的實例就是在新推出的PSoC4上做的。

我們把這種加法硬件PDM和定時器式的硬件PWM稍做比較,就會發現某些優點。(以下PWM和PDM均指定時器式的硬件PWM和加法硬件PDM)

(1) 相同的輸出平均值

PDM和PWM有相同的輸出平均值,這是兩者比較的前提。即,在N個clk長的時間內,它們都輸出了H個1。

只不過對PWM,這H個1是連在一起的;而對PDM,這H個1是近乎均勻地分布的。這也是兩者根本區別之所在。

(2) 輸出建立時間

假設都是16位,N=65536,且都輸出0.7071…。時鐘Fclk=1MHz。

那么定時器式PWM的一個PWM脈沖周期是65.536毫秒,在65.536毫秒內輸出連續的46340個1和連續的19196個0,過1秒鈡,即15個PWM脈沖周期輸出未必已經到達穩定。

而加法硬件PDM,看一下第二篇的例子,經過256個clk,即0.256毫秒,就可穩定到誤差1%以內。

對DA輸出有上升沿、下降沿要求時,就可以分出優劣。

(3) 濾波

而且對PDM的濾波要容易得多。對PWM,要按T=65.536毫秒,即f=15Hz計算濾波電路。而對PDM,看精度按100KHz、10KHz、1KHz計算濾波電路就能滿足要求了。在某些情況下,不用專門的濾波電路,輸出的發布電容、引線電感就可起濾波作用。

對PWM輸出的噪聲頻譜做一分析,會發現,在f = Fclk / N的低頻率點,有一個不可避免的峰值。而PDM大大壓低了低頻峰值和整體的噪聲電平,使得濾波更加容易。

(4) 任意截斷的平均值

在PDM輸出中,從任一時刻開始,截取一段任意長度(Nx)的輸出,其中1的個數為Hx,我們有:Hx/Nx總是目標輸出值的最好分數逼近。

而PWM輸出序列中,除了Nx=N,截取下來的Hx/Nx往往遠離目標輸出值。

(5) 任意時刻改變設定值

PWM只能在N個計數終了時,改變設定值;盡管該設定值已事先送到寄存器。而PDM可以在任意時刻改變設定值,并直接在輸出有所反映。

對那些對輸出延時有要求的DA,就可以有所選擇了。

這些,都使得基于加法的硬件PDM比基于定時器的硬件PWM在使用上更具優勢。

-

PWM

+關注

關注

114文章

5148瀏覽量

213436 -

PDM

+關注

關注

2文章

92瀏覽量

17841

發布評論請先 登錄

相關推薦

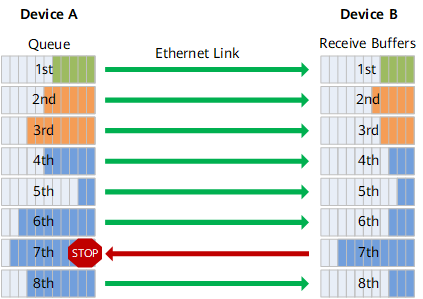

RoCE與IB對比分析(二):功能應用篇

光伏電站運維管理系統與傳統運維模式對比分析

常用音頻線接口對比分析

PDM系統哪個好?三品PDM系統怎么樣?

對比分析點焊機與傳統焊接方法

網關和路由器的對比分析

2020-2022-2024年TI杯全國大學生電子設計競賽官方推薦芯片對比分析比較

交流伺服電機與直流伺服電機的對比分析

不同地物分類方法在長江中下游典型湖區應用對比分析

超級電容儲能與飛輪儲能的對比分析

機器人焊接與人工焊接對比分析

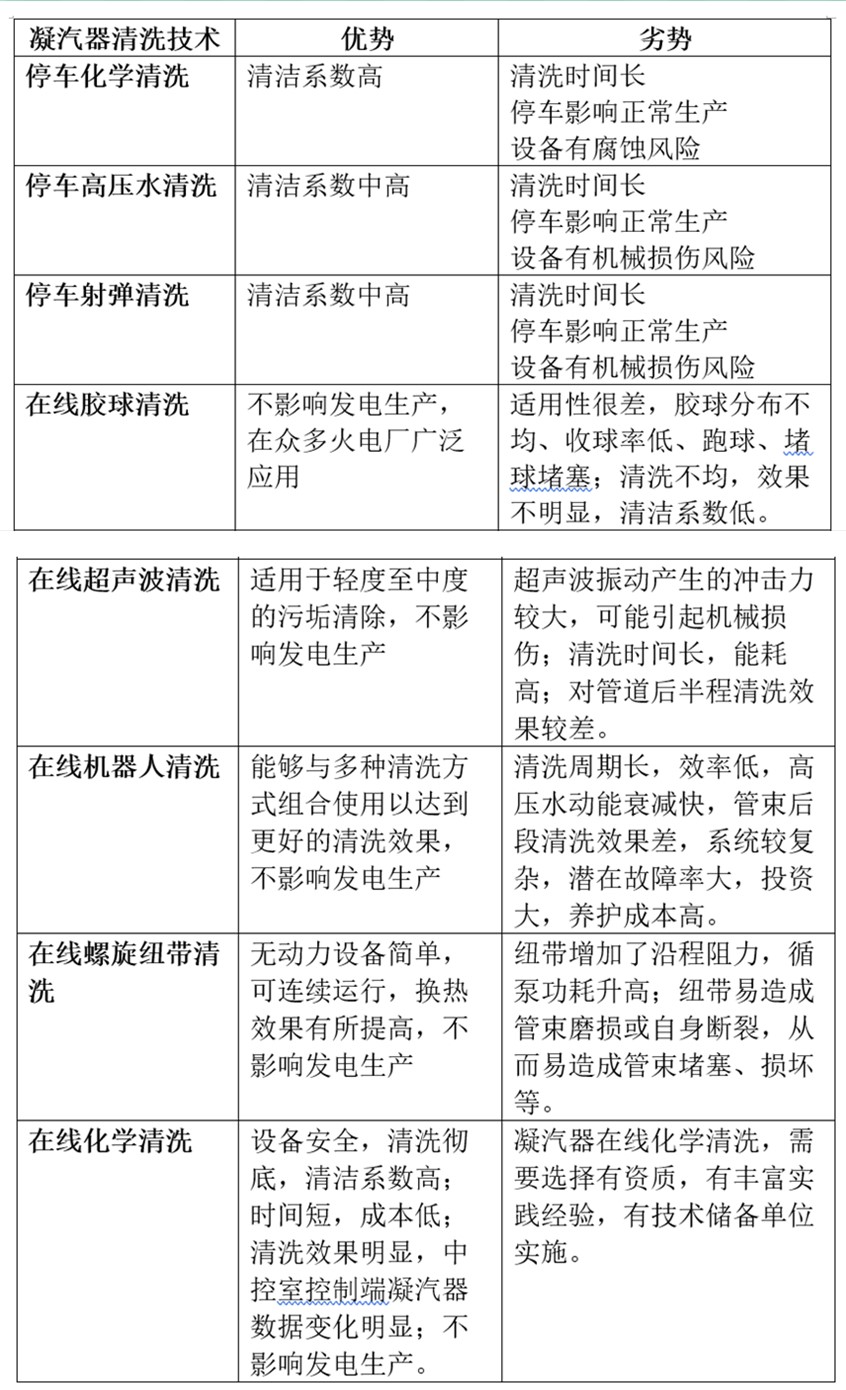

火電廠凝汽器不停車在線清洗與凝汽器停車清洗八種技術對比分析

DC電源模塊與AC電源模塊的對比分析

PWM與PDM對比分析哪個好

PWM與PDM對比分析哪個好

評論