黑客攻擊是當下最嚴重的安全問題之一,隨著近期攻擊活動的頻繁,國際上不少能源公司都深受其害,被竊取勒索機密信息。然而,同樣的攻擊也在威脅著人們看不到的領域,比如最近專門針對工控系統(tǒng)的惡意軟件PIPEDREAM,就是通過PLC編程軟件CODESYS的漏洞進行攻擊的。

不過這類攻擊主要是還是從軟件層面上攻破PLC等硬件,那有沒有直接在硬件層面上為黑客創(chuàng)造可乘之機的方法呢?自然也有,也就是我們常說的硬件木馬。這類硬件木馬更像是一種后門攻擊,靠的就是對集成電路進行惡意篡改。

硬件木馬如何下黑手

集成電路已經成為了諸多實際應用中不可或缺的組件,從智能家居、工業(yè)設備到機器學習加速器。然而隨著IC的設計與生產愈發(fā)復雜,一個芯片可能包含數百億晶體管,先進工藝所需的生產條件也不是Fabless廠商能夠輕易負擔的。很多時候這些工作是外包給第三方完成的,這樣的流程結構造成了一些硬件安全隱患,只要流程中任意一名參與者圖謀不軌,就有可能利用硬件木馬觸發(fā)敏感信息泄露、性能下降和IP竊取。

這類硬件木馬通常分為兩個部分,一個是觸發(fā)器,另一個就是內部的載荷了。觸發(fā)器決定硬件木馬什么時候激活,載荷則負責關鍵的攻擊工作,比如竊取隱私信息或產生錯誤的輸出等。

就以常見的邊信道攻擊(SCA)為例,這種攻擊可以利用IC的固有物理屬性,比如時序、功耗等,獲取本放在IC內部的信息,但這種攻擊往往需要獲取大量的數據和處理,如今不少安全性強的芯片通過阻絕這一過程,讓自己免受SCA的破壞。然而在硬件木馬的輔助下,可以省去處理的過程,極大減少攻擊的時間。

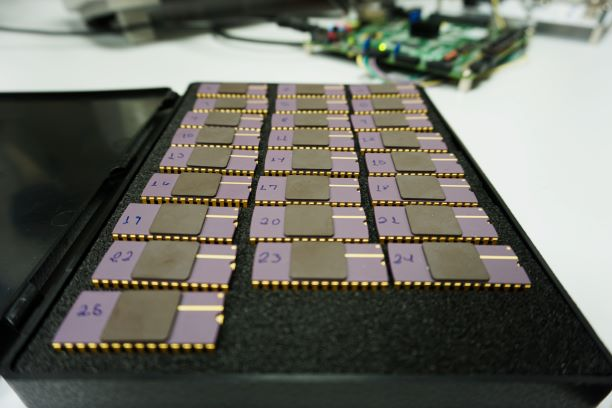

驗證硬件木馬的樣片 / 塔林理工大學

那么攻擊者是在哪個階段插入這些硬件木馬的呢?塔林理工大學的研究人員為了驗證硬件木馬的可行性,打造了一個基于65nmCMOS工藝的ASIC芯片,通過ECO在其中的4個加密核(兩個AES、兩個PRESENT)中引入了硬件木馬,“下黑手”的時間只花了不到兩個小時。

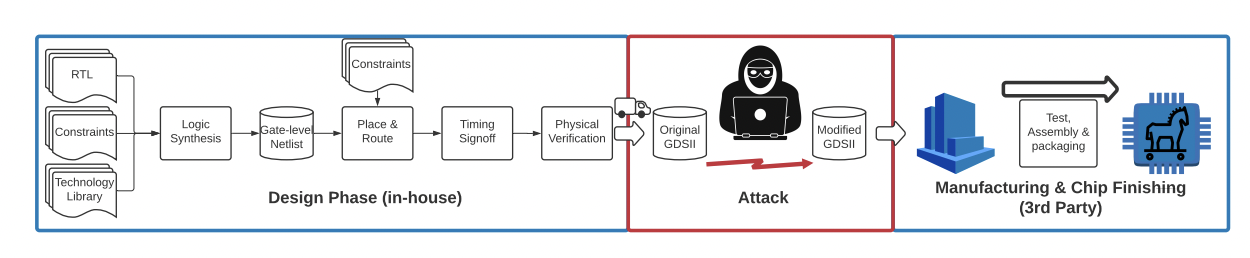

芯片設計、攻擊和制造的流程 / 塔林理工大學

從上圖可以看出,在GDSII版圖送給代工廠的途中,攻擊者對其進行了篡改,改變或增加額外的邏輯,最后代工廠制造出了內含木馬的芯片,并利用基于功率的邊信道攻擊獲取了加密信息。若是芯片本身功耗就在mW級左右,終端用戶基本很難察覺到來自芯片的異常。

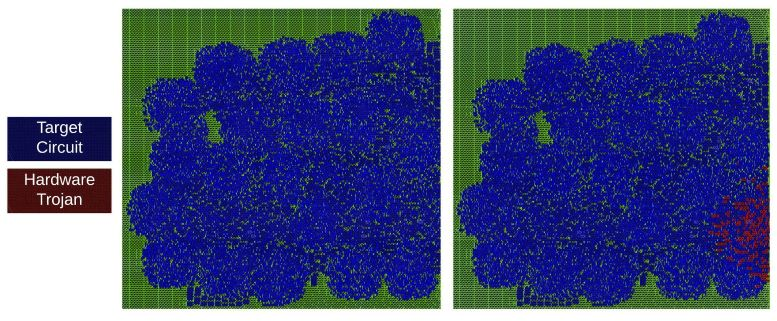

原始和被篡改后的布局 / 塔林理工大學

ECO必須要四個先決輸入,工藝庫、單元庫、門級網表和時序約束,對于能在代工廠內對版圖動手的攻擊者來說,前兩項已經到手了,門級網表可以通過EDA工具從布局中提取,而時序約束只能靠一定程度的估計了。

如何杜絕硬件木馬

至于杜絕硬件木馬的話,目前主要方式有兩種,一種是邊信道分析,一種是邏輯測試。像以上的邊信道攻擊方式,因為會改變時序等參數,所以邊信道分析可以檢測出這類無功能性的硬件木馬,但對于小的硬件木馬存在一定的誤報率。而邏輯測試的難點在于用少量的測試模式,增加對觸發(fā)器的覆蓋。

美國圣地亞哥大學的幾位研究人員提出了一種更好的檢測方式,名為AdaTest。該檢測方式通過加強學習產生了一組多樣的測試輸入,通過迭代的方式逐步產生高回報值的測試矢量。此外,AdaTest會著重關注為硬件木馬檢測提供更多信息的測試樣本,從而減少樣本數量提高樣本質量。

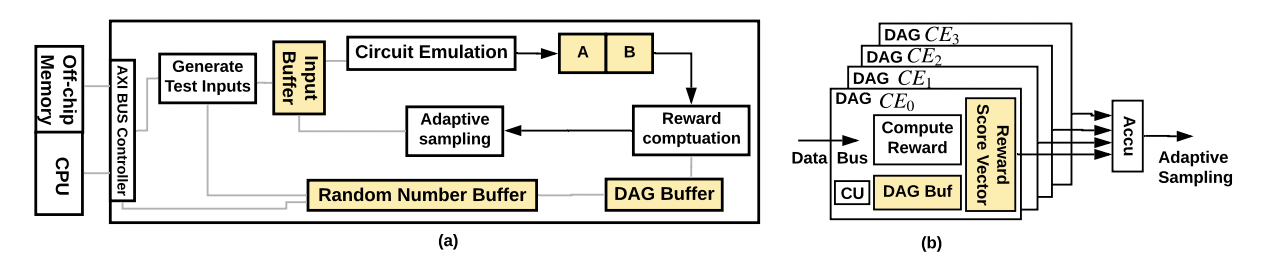

AdaTest的流程圖 / 圣地亞哥大學

為了減小硬件開銷,AdaTest能在可編程硬件上部署電路仿真,從而加速測試輸入的回報值評估;其次,通過自動構建輔助電路進行測試輸入生成、回報值評估和自適應采樣,AdaTest中的每個計算階段都被流水線化。與傳統(tǒng)的邏輯測試相比,AdaTest的測試生成速度提高了兩個數量級,與此同時測試樣本大小減小了兩個數量級,卻因此實現了同樣或者更高的硬件木馬檢測率。

由上可知,與預防硬件木馬一樣,植入硬件木馬同樣不是一件易事,所以代工廠出現這類硬件木馬出現的概率比較小,但不代表不存在這樣的安全威脅,畢竟人為設計失誤都出現了,人為篡改也不是不可能的,設計者對這樣的疏忽也不可不防。

-

集成電路

+關注

關注

5381文章

11389瀏覽量

360892 -

能源

+關注

關注

3文章

1577瀏覽量

43424 -

編程軟件

+關注

關注

3文章

143瀏覽量

23464

發(fā)布評論請先 登錄

相關推薦

IBM、富士通或投資Rapidus晶圓代工廠

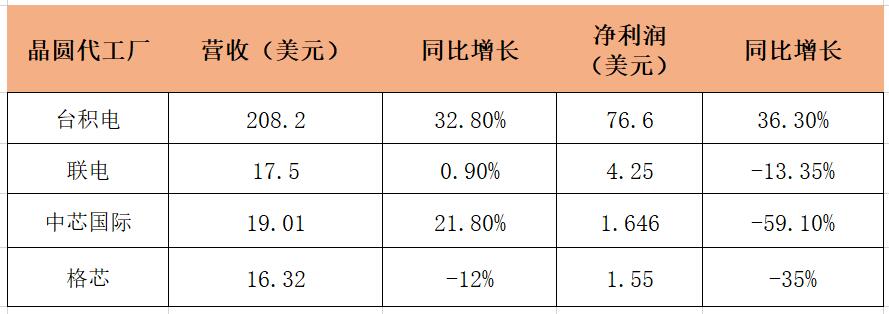

晶圓出貨量增長!臺積電Q2營收飆漲,四大芯片代工廠財報有何亮點?

三星否認晶圓代工廠生產缺陷傳聞

中芯國際躍升至全球第三大晶圓代工廠

SK海力士系統(tǒng)IC將出售無錫晶圓廠49.9%股權

SK海力士向中企出售無錫晶圓代工廠近50%股權

美國純MEMS代工廠RVM宣布新建12英寸MEMS晶圓代工產線

2023年全球晶圓代工市場營收狀況:晶合集成在價格戰(zhàn)中逆勢上揚

英特爾:互不干涉晶圓代工 2030年成全球第二大代工廠

中國晶圓代工廠降低價格吸引客戶

三星晶圓代工一季度將大降價,欲與對手搶單

全球晶圓代工行業(yè)格局及市場趨勢

從晶圓代工廠下黑手?提防集成電路的“硬件木馬”

從晶圓代工廠下黑手?提防集成電路的“硬件木馬”

評論