一、時(shí)鐘相關(guān)概念

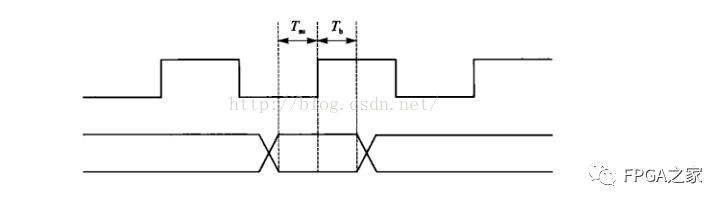

理想的時(shí)鐘模型是一個(gè)占空比為50%且周期固定的方波。Tclk為一個(gè)時(shí)鐘周期,T1為高脈沖寬度,T2為低脈沖寬度,Tclk=T1+T2。占空比定義為高脈沖寬度與周期之比,即T1/Tclk。

圖1 理想時(shí)鐘波形

建立時(shí)間(Tsu):是指在時(shí)鐘上升沿到來(lái)之前數(shù)據(jù)必須保持穩(wěn)定的時(shí)間;

保持時(shí)間(Th):是指在時(shí)鐘上升沿到來(lái)以后數(shù)據(jù)必須保持穩(wěn)定的時(shí)間。如圖2所示。

圖2 建立和保持時(shí)間

一個(gè)數(shù)據(jù)需要在時(shí)鐘的上升沿鎖存,那么這個(gè)數(shù)據(jù)就必須在這個(gè)時(shí)鐘上升沿的建立時(shí)間和保持時(shí)間內(nèi)保持穩(wěn)定。

上面列舉的是一個(gè)理想的時(shí)鐘波形,而實(shí)際時(shí)鐘信號(hào)的分析要比這復(fù)雜得多。時(shí)鐘本身也具有一些不確定性,如時(shí)鐘抖動(dòng)(jitter)和時(shí)鐘偏斜(sknew)等。時(shí)鐘的邊沿變化不可能總是理想的瞬變,它會(huì)有一個(gè)從高到低或者從低到高的變化過(guò)程,實(shí)際的情況抽象出來(lái)就如圖3所示,時(shí)鐘信號(hào)邊沿變化的不確定時(shí)間稱之為時(shí)鐘偏斜(clock skew)。再回到之前定義的建立時(shí)間和保持時(shí)間,嚴(yán)格的說(shuō),建立時(shí)間就應(yīng)該是Tsu+T1,而保持時(shí)間就應(yīng)該是Th+T2。

圖3 時(shí)鐘抖動(dòng)模型

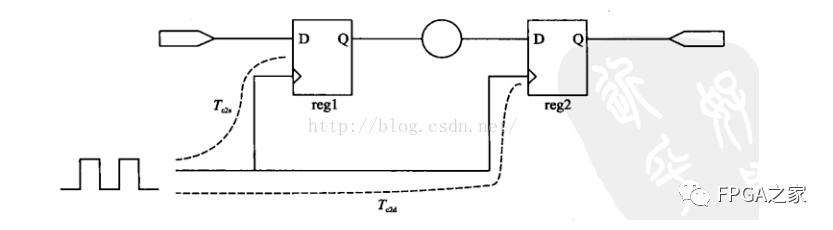

時(shí)鐘分析的起點(diǎn)是源寄存器(reg1),終點(diǎn)是目的寄存器(reg2)。時(shí)鐘和其他信號(hào)的傳輸一樣都會(huì)有延時(shí)。圖4中,時(shí)鐘信號(hào)從時(shí)鐘源傳輸?shù)皆醇拇嫫鞯难訒r(shí)定義為T(mén)c2s,傳輸?shù)侥康募拇嫫鞯难訒r(shí)定義為T(mén)c2d,時(shí)鐘網(wǎng)絡(luò)延時(shí)就定義為T(mén)c2d與Tc2s之差,即Tskew=Tc2d-Tc2s。

圖4 時(shí)鐘偏斜的寄存器傳輸模型

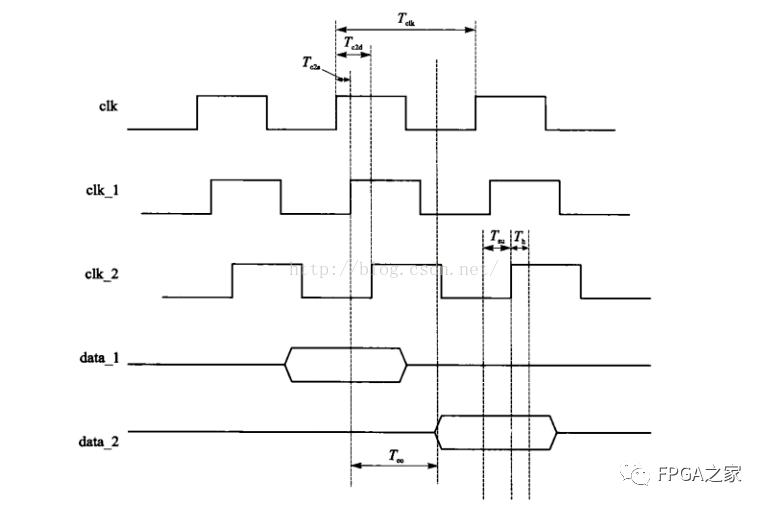

圖5是時(shí)鐘偏斜模型的波形表示。

圖5 時(shí)鐘偏斜的波形圖

clk是源時(shí)鐘,可以認(rèn)為是一個(gè)理想的時(shí)鐘模型。clk_1是時(shí)鐘傳輸?shù)皆醇拇嫫鱮eg1的波形(延時(shí)Tc2s),clk_2是時(shí)鐘傳輸?shù)侥康募拇嫫鱮eg2的波形(延時(shí)Tc2d)。data_1是數(shù)據(jù)在源寄存器reg1的傳輸波形,data_2是數(shù)據(jù)在目的寄存器reg2的傳輸波形。

圖6 數(shù)據(jù)與時(shí)鐘關(guān)系

原文標(biāo)題:時(shí)鐘相關(guān)概念

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

審核編輯:湯梓紅

-

時(shí)鐘

+關(guān)注

關(guān)注

10文章

1676瀏覽量

130975 -

模型

+關(guān)注

關(guān)注

1文章

3032瀏覽量

48376

原文標(biāo)題:時(shí)鐘相關(guān)概念

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

了解一下STM32的時(shí)鐘樹(shù)

關(guān)于藍(lán)牙模塊基礎(chǔ)知識(shí)點(diǎn)介紹的太詳細(xì)了

詳細(xì)了解下ups的相關(guān)計(jì)算

詳細(xì)了解一下STM32F1的具體電路參數(shù)

一文了解透?jìng)髟?b class='flag-5'>基礎(chǔ)知識(shí)

電阻基礎(chǔ)知識(shí)

機(jī)器學(xué)習(xí)的基礎(chǔ)知識(shí)詳細(xì)說(shuō)明

FPGA的入門(mén)基礎(chǔ)知識(shí)詳細(xì)說(shuō)明

了解一下機(jī)器學(xué)習(xí)中的基礎(chǔ)知識(shí)

一文了解IGBT基礎(chǔ)知識(shí)資料下載

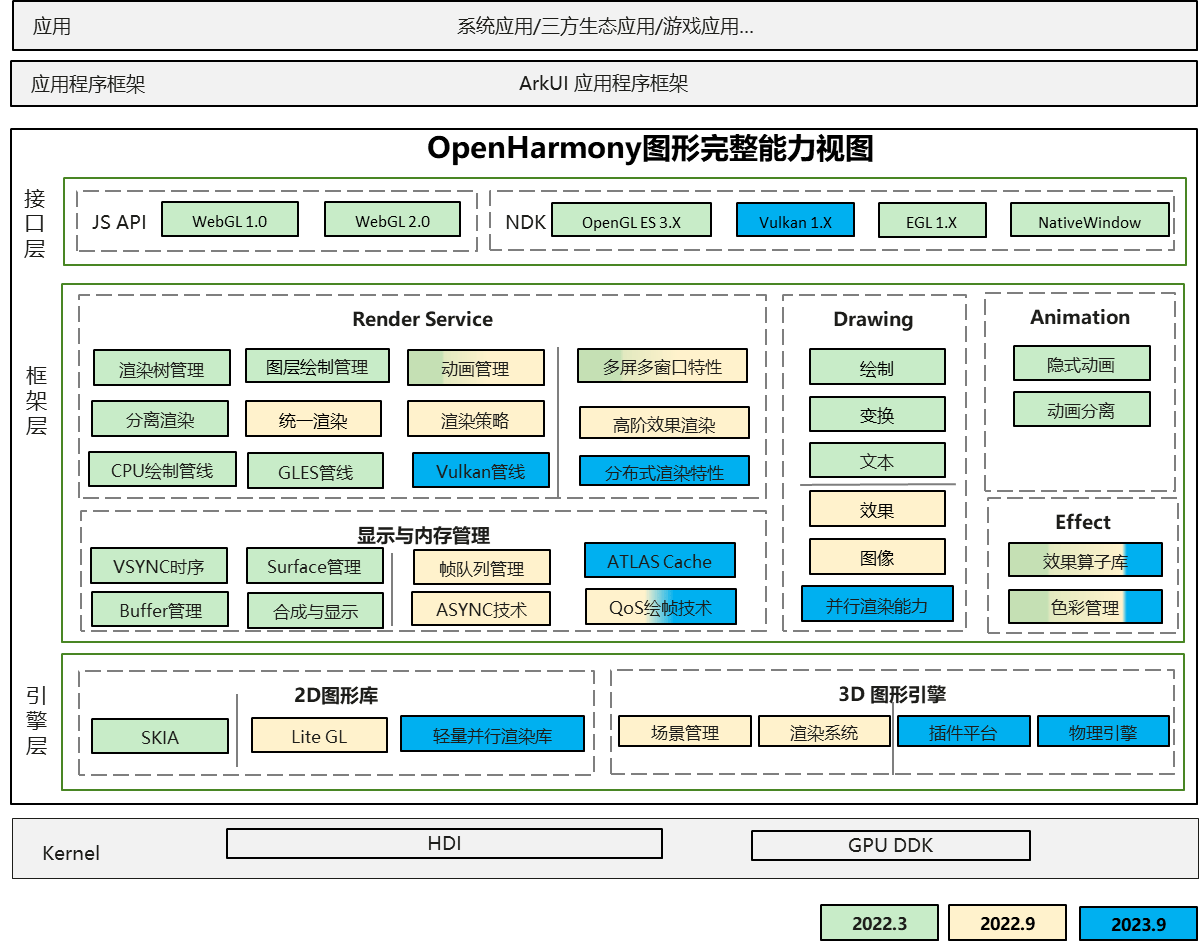

一文詳細(xì)了解OpenHarmony新圖形框架

時(shí)鐘抖動(dòng)解秘—高速鏈路時(shí)鐘抖動(dòng)規(guī)范基礎(chǔ)知識(shí)

一文帶你詳細(xì)了解工業(yè)電腦

一文詳細(xì)了解時(shí)鐘基礎(chǔ)知識(shí)

一文詳細(xì)了解時(shí)鐘基礎(chǔ)知識(shí)

評(píng)論