關于CPU和程序的執行

1、程序的運行過程,實際上是程序涉及到的、未涉及到的一大堆的指令的執行過程。

當程序要執行的部分被裝載到內存后,CPU要從內存中取出指令,然后指令解碼(以便知道類型和操作數,簡單的理解為CPU要知道這是什么指令),然后執行該指令。再然后取下一個指令、解碼、執行,以此類推直到程序退出。

2、這個取指、解碼、執行三個過程構成一個CPU的基本周期。

3、每個CPU都有一套自己可以執行的專門的指令集(注意,這部分指令是CPU提供的,CPU-Z軟件可查看)。 正是因為不同CPU架構的指令集不同,使得x86處理器不能執行ARM程序,ARM程序也不能執行x86程序。(Intel和AMD都使用x86指令集,手機絕大多數使用ARM指令集)。 注:指令集的軟硬件層次之分:硬件指令集是硬件層次上由CPU自身提供的可執行的指令集合。軟件指令集是指語言程序庫所提供的指令,只要安裝了該語言的程序庫,指令就可以執行。

4、由于CPU訪問內存以得到指令或數據的時間要比執行指令花費的時間長很多,因此在CPU內部提供了一些用來保存關鍵變量、臨時數據等信息的通用寄存器。

所以,CPU需要提供 一些特定的指令,使得可以從內存中讀取數據存入寄存器以及可以將寄存器數據存入內存。 此外還需要提供加法、減、not/and/or等基本運算指令,而乘除法運算都是推算出來的(支持的基本運算指令參見ALU Functions),所以乘除法的速度要慢的多。這也是算法里在考慮時間復雜度時常常忽略加減法次數帶來的影響,而考慮乘除法的次數的原因。

5、除了通用寄存器,還有一些特殊的寄存器。典型的如:

PC:program counter,表示程序計數器,它保存了將要取出的下一條指令的內存地址,指令取出后,就會更新該寄存器指向下一條指令。

堆棧指針:指向內存當前棧的頂端,包含了每個函數執行過程的棧幀,該棧幀中保存了該函數相關的輸入參數、局部變量、以及一些沒有保存在寄存器中的臨時變量。

PSW:program status word,表示程序狀態字,這個寄存器內保存了一些控制位,比如CPU的優先級、CPU的工作模式(用戶態還是內核態模式)等。

6、在CPU進行進程切換的時候,需要將寄存器中和當前進程有關的狀態數據寫入內存對應的位置(內核中該進程的棧空間)保存起來,當切換回該進程時,需要從內存中拷貝回寄存器中。即上下文切換時,需要保護現場和恢復現場。

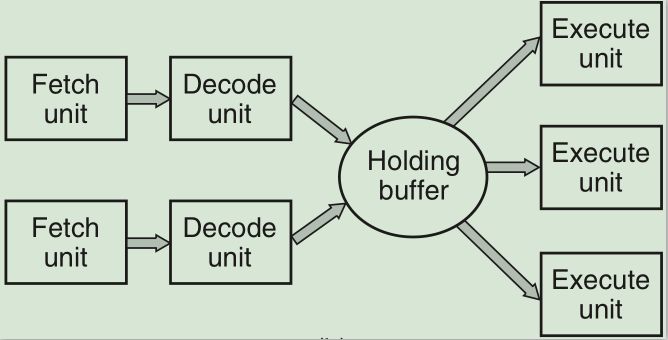

7、為了改善性能,CPU已經不是單條取指--》解碼--》執行的路線,而是分別為這3個過程分別提供獨立的取值單元,解碼單元以及執行單元。這樣就形成了流水線模式。 例如,流水線的最后一個單元——執行單元正在執行第n條指令,而前一個單元可以對第n+1條指令進行解碼,再前一個單元即取指單元可以去讀取第n+2條指令。這是三階段的流水線,還可能會有更長的流水線模式。

8、更優化的CPU架構是superscalar架構(超標量架構)。這種架構將取指、解碼、執行單元分開,有大量的執行單元,然后每個取指+解碼的部分都以并行的方式運行。比如有2個取指+解碼的并行工作線路,每個工作線路都將解碼后的指令放入一個緩存緩沖區等待執行單元去取出執行。

9、除了嵌入式系統,多數CPU都有兩種工作模式:內核態和用戶態。這兩種工作模式是由PSW寄存器上的一個二進制位來控制的。

10、內核態的CPU,可以執行指令集中的所有指令,并使用硬件的所有功能。

11、用戶態的CPU,只允許執行指令集中的部分指令。一般而言,IO相關和把內存保護相關的所有執行在用戶態下都是被禁止的,此外其它一些特權指令也是被禁止的,比如用戶態下不能將PSW的模式設置控制位設置成內核態。

12、用戶態CPU想要執行特權操作,需要發起系統調用來請求內核幫忙完成對應的操作。其實是在發起系統調用后,CPU會執行trap指令陷入(trap)到內核。當特權操作完成后,需要執行一個指令讓CPU返回到用戶態。

13、除了系統調用會陷入內核,更多的是硬件會引起trap行為陷入內核,使得CPU控制權可以回到操作系統,以便操作系統去決定如何處理硬件異常。

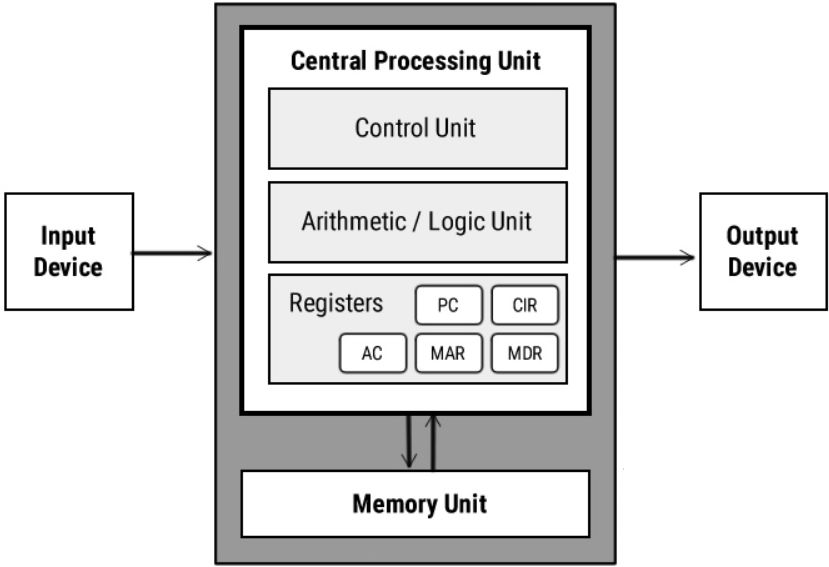

關于CPU的基本組成

1、CPU是用來運算的(加法運算+、乘法運算*、邏輯運算and not or等),例如c=a+b。

2、運算操作涉及到數據輸入(input)、處理、數據輸出(output),a和b是輸入數據,加法運算是處理,c是輸出數據。

3、CPU需要使用一個叫做存儲器(也就是各種寄存器)的東西保存輸入和輸出數據。以下是幾種常見的寄存器(前文也介紹了一些)

MAR: memory address register,保存將要被訪問數據在內存中哪個地址處,保存的是地址值

MDR: memory data register,保存從內存讀取進來的數據或將要寫入內存的數據,保存的是數據值

AC: Accumulator,保存算術運算和邏輯運算的中間結果,保存的是數據值

PC: Program Counter,保存下一個將要被執行指令的地址,保存的是地址值

CIR: current instruction register,保存當前正在執行的指令

4、CPU還要將一些常用的基本運算工具(如加法器)放進CPU,這部分負責運算,稱為算術邏輯單元(ALU, Arithmetic Logic Unit)。

5、CPU中還有一個控制器(CU, Control Unit),負責將存儲器中的數據送到ALU中去做運算,并將運算后的結果存回到存儲器中。

控制器還包含了一些控制信號。

6、控制器之所以知道數據放哪里、做什么運算(比如是做加法還是邏輯運算?)都是由指令告訴控制器的,每個指令對應一個基本操作,比如加法運算對應一個指令。 7、例如,將兩個MDR寄存器(保存了來自內存的兩個數據)中的值拷貝到ALU中,然后根據指定的操作指令執行加法運算,將運算結果拷貝會一個MDR寄存器中,最后寫入到內存。 8、這就是馮諾依曼結構圖,也就是現在計算機的結構圖。

關于CPU的多核和多線程

1、CPU的物理個數由主板上的插槽數量決定,每個CPU可以有多核心,每核心可能會有多線程。

2、多核CPU的每核(每核都是一個小芯片),在OS看來都是一個獨立的CPU。

3、對于超線程CPU來說,每核CPU可以有多個線程(數量是兩個,比如1核雙線程,2核4線程,4核8線程),每個線程都是一個虛擬的邏輯CPU(比如windows下是以邏輯處理器的名稱稱呼的),而每個線程在OS看來也是獨立的CPU。

這是欺騙操作系統的行為,在物理上仍然只有1核,只不過在超線程CPU的角度上看,它認為它的超線程會加速程序的運行。

4、要發揮超線程優勢,需要操作系統對超線程有專門的優化。 5、多線程的CPU在能力上,比非多線程的CPU核心要更強,但每個線程不足以與獨立的CPU核心能力相比較。

6、每核上的多線程CPU都共享該核的CPU資源。

例如,假設每核CPU都只有一個“發動機”資源,那么線程1這個虛擬CPU使用了這個“發動機”后,線程2就沒法使用,只能等待。

所以,超線程技術的主要目的是為了增加流水線(參見前文對流水線的解釋)上更多個獨立的指令,這樣線程1和線程2在流水線上就盡量不會爭搶該核CPU資源。所以,超線程技術利用了superscalar(超標量)架構的優點。

7、多線程意味著每核可以有多個線程的狀態。比如某核的線程1空閑,線程2運行。

8、多線程沒有提供真正意義上的并行處理,每核CPU在某一時刻仍然只能運行一個進程,因為線程1和線程2是共享某核CPU資源的。可以簡單的認為每核CPU在獨立執行進程的能力上,有一個資源是唯一的,線程1獲取了該資源,線程2就沒法獲取。 但是,線程1和線程2在很多方面上是可以并行執行的。比如可以并行取指、并行解碼、并行執行指令等。所以雖然單核在同一時間只能執行一個進程,但線程1和線程2可以互相幫助,加速進程的執行。 并且,如果線程1在某一時刻獲取了該核執行進程的能力,假設此刻該進程發出了IO請求,于是線程1掌握的執行進程的能力,就可以被線程2獲取,即切換到線程2。這是在執行線程間的切換,是非常輕量級的。(WIKI: if resources for one process are not available, then another process can continue if its resources are available)

9、多線程可能會出現一種現象:假如2核4線程CPU,有兩個進程要被調度,那么只有兩個線程會處于運行狀態,如果這兩個線程是在同一核上,則另一核完全空轉,處于浪費狀態。更期望的結果是每核上都有一個CPU分別調度這兩個進程。

關于CPU上的高速緩存

1、最高速的緩存是CPU的寄存器,它們和CPU的材料相同,最靠近CPU或最接近CPU,訪問它們沒有時延(《1ns)。但容量很小,小于1kb。

32bit:32*32比特=128字節

64bit:64*64比特=512字節

2、寄存器之下,是CPU的高速緩存。分為L1緩存、L2緩存、L3緩存,每層速度按數量級遞減、容量也越來越大。

3、每核心都有一個自己的L1緩存。L1緩存分兩種:L1指令緩存(L1-icache)和L1數據緩存(L1-dcache)。L1指令緩存用來存放已解碼指令,L1數據緩存用來放訪問非常頻繁的數據。

4、L2緩存用來存放近期使用過的內存數據。更嚴格地說,存放的是很可能將來會被CPU使用的數據。

5、多數多核CPU的各核都各自擁有一個L2緩存,但也有多核共享L2緩存的設計。無論如何,L1是各核私有的(但對某核內的多線程是共享的)。

審核編輯 :李倩

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

嵌入式系統

+關注

關注

41文章

3570瀏覽量

129252 -

cpu

+關注

關注

68文章

10829瀏覽量

211193

原文標題:關于CPU的一些基本知識總結

文章出處:【微信號:Imgtec,微信公眾號:Imagination Tech】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么外設要通過接口與CPU相連

CPU主要參數有哪些

CPU線程和程序線程的區別

cpu控制器負責什么運算

簡述cpu控制器的工作原理

cpu控制器和運算器組成的部件有哪些

cpu控制器的主要作用是什么

服務器中的CPU核心和線程到底是什么?

CPU與PUA的區別

secondary cpu執行流程介紹

CPU和程序的執行

CPU和程序的執行

評論