固定外形開關

比薩盒開關在辦公室和企業中變得越來越普遍,制造商已努力在降低成本的同時增加更多功能。披薩盒式交換機采用緊湊型設計,適用于高密度、高可靠性和靈活部署。與大型機架配置交換機相比,披薩盒交換機設備的功耗可以大大降低,以及對空間、電源、空調等機房基礎設施的要求,幫助運營商降低總體擁有成本(TCO) )。

高速 SerDes 的時鐘要求

在過去十年中,隨著數據速率和數據中心數量的快速增長,現在可以支持新興的數據密集型計算應用程序(例如機器學習和神經網絡)。如果我們使用 SerDes 數據速率作為指標,當今最先進的 4 級脈沖幅度調制 (PAM4) SerDes 運行速度為 112Gbps。現在可以在單個通道中支持 100G 以太網,這在 21 世紀初只有 180 個并行通道才有可能。為了支持用于設計 400G 或 800G 以太網和光網絡的 112Gbps PAM4 技術,SerDes 的物理層參考時鐘需要具有低于 150fs RMS 的相位抖動。如果加上 PCB 上的噪聲考慮、元件布局限制、信號布線要求和電源去耦,硬件開發人員更喜歡這些物理層時鐘的相位抖動接近 100fs RMS。由于典型的網絡交換機還包括其他時鐘,包括用于同步的時鐘(下一節將詳細介紹)、處理器、ASIC、內存等,因此這是一種超高性能計時 IC,可在單芯片是首選。這有助于 PCB 設計人員擁有針對成本、面積、功率和性能進行優化的時鐘樹解決方案。瑞薩電子現在提供可滿足上述所有要求的 ClockMatrix 2。首選在單個芯片中生成所有時鐘要求的超高性能定時 IC。這有助于 PCB 設計人員擁有針對成本、面積、功率和性能進行優化的時鐘樹解決方案。瑞薩電子現在提供可滿足上述所有要求的 ClockMatrix 2。首選在單個芯片中生成所有時鐘要求的超高性能定時 IC。這有助于 PCB 設計人員擁有針對成本、面積、功率和性能進行優化的時鐘樹解決方案。瑞薩電子現在提供可滿足上述所有要求的 ClockMatrix 2。

什么是時鐘同步?

5G 正在實現連接的下一個前沿,恰如其分地命名為“物聯網”,提供迄今為止最快的移動數據傳輸和廣泛的覆蓋范圍。這種處理新服務的能力也對網絡覆蓋、網絡性能和調度管理提出了新的挑戰。運營商需要一個能夠處理高數據速率和帶寬、大用戶群、更好的業務體驗和更高效的運維的無線網絡。

為了實現網絡效率和保證小區覆蓋,同步是所有電信網絡的基本前提。5G 網絡尤其提出了新的挑戰,對在整個網絡中分配同步參考的準確性和可靠性的需求不斷增加。

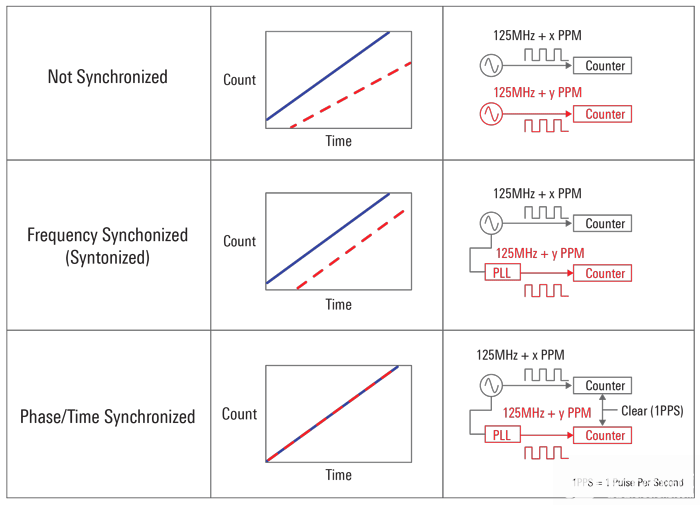

圖 1 是在不同步的網絡中會發生的情況的示例。如果沒有完整的時間和頻率同步,任何關鍵服務,如移動切換(支持移動用戶的呼叫或數據傳輸的無縫轉換,在傳輸過程中,從一個基站到另一個基站,防止掉線或中止數據傳輸)都是不可能的。 此外,還需要頻率同步來優化基站利用率并提高其效率。時間要求嚴格的應用程序和診斷也需要時間同步。

圖像

圖 1. 網絡同步

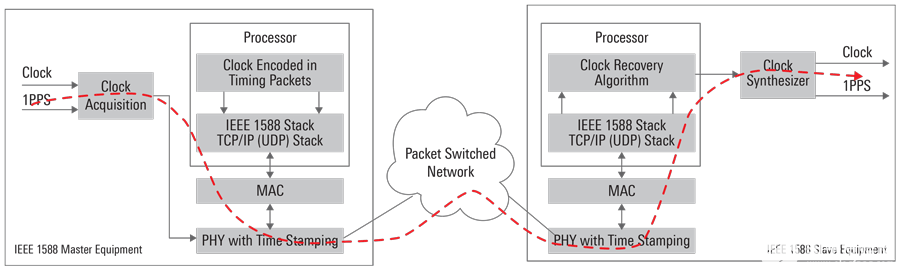

對以太網系統的時序要求變得越來越嚴格。傳統上,這些系統是在集中式架構中實現的,在這種架構中,通過仔細注意編程以及具有確定性延遲的通信技術來滿足時序約束。近年來,越來越多的此類系統利用更分布式的架構和現代網絡技術,其時序規范比舊的更專業的技術更不嚴格。這導致了在此類系統中強制執行時序要求的替代方法。一種這樣的技術是使用包含實時時鐘的系統組件,所有這些都在系統內相互同步。IEEE 1588 精確時間協議 (PTP) 是一種跨分組交換網絡 (PSN) 傳輸同步的時間協議。Master 將時鐘編碼為數據包,然后發送到 Slave。IEEE 1588 可以在沒有網絡支持的情況下用于端到端解決方案,也可以在網絡支持的情況下使用(圖 2)。

圖像

圖 2. IEEE 1588 精確時間協議

介紹時鐘矩陣 2

ClockMatrix 2 是一種超高性能、高精度、多通道定時解決方案,針對 400/800Gbps 光傳輸和有線網絡應用進行了優化。基于 2019 年推出的用于 5G 無線和 100/200Gbps 有線網絡應用的 ClockMatrix 設備,第二代系列提供了改進的性能,相位抖動低至 88fs RMS。

高度集成的器件提供了實現 IEEE 1588 的所有操作模式所需的所有功能,并具有抖動衰減功能。該器件提供超低抖動時鐘輸出,可用于數據速率高達 112Gbps PAM4 的同步以太網 SerDes,降低了設計復雜性和物料清單 (BOM) 要求,同時還允許客戶將計時器件應用于廣泛的各種網絡應用。

ClockMatrix 2 系列的主要特點

高度集成的 6 通道精密定時源,無需為高速接口添加額外的抖動衰減器

時鐘輸出上的 88fs RMS 相位抖動支持高速串行鏈路的超低抖動時鐘輸出(高達 112Gbps PAM4 SerDes)

支持多種標準和協議,包括同步以太網 (Sync-E) 和 IEEE 1588

完全符合 ITU-T G.8262.1 和 G.8262 同步以太網標準以及根據 ITU-T G.8273.2 超過 C 類和 D 類時間精度要求的電信邊界時鐘要求

ClockMatrix 2 系統同步器可以與瑞薩電子互補的模擬和電源產品相結合,為各種應用創建全面的解決方案。例如,ClockMatrix 2與瑞薩的模擬和電源產品一起集成到200/400/800Gbps 固定外形開關解決方案的成功組合中。瑞薩電子提供 250 多種與兼容設備的成功組合,適用于廣泛的應用和終端產品。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17605瀏覽量

249563 -

以太網

+關注

關注

40文章

5385瀏覽量

171164

發布評論請先 登錄

相關推薦

具有EEPROM的LMK05028低抖動雙通道網絡同步器時鐘數據表

LMK05318具有兩個頻域的超低抖動網絡同步器時鐘數據表

采用JESD204B的LMK5C33216超低抖動時鐘同步器數據表

LMK5B12204具有兩個頻域的超低抖動網絡同步器時鐘數據表

CDCE72010十路輸出高性能時鐘同步器、抖動消除器和時鐘分配器數據表

時鐘抖動和時鐘偏移的區別

時鐘抖動與相位噪聲的關系

FPGA如何消除時鐘抖動

簡述時鐘抖動的產生原因

毫微微時鐘網絡同步器、抖動衰減器和時鐘發生器RC32112A 數據表

FemtoClock2抖動衰減器和時鐘發生器RC325008A數據手冊

使用ClockMatrix 2解決同步和時鐘抖動挑戰

使用ClockMatrix 2解決同步和時鐘抖動挑戰

評論