PS配置啟動過程

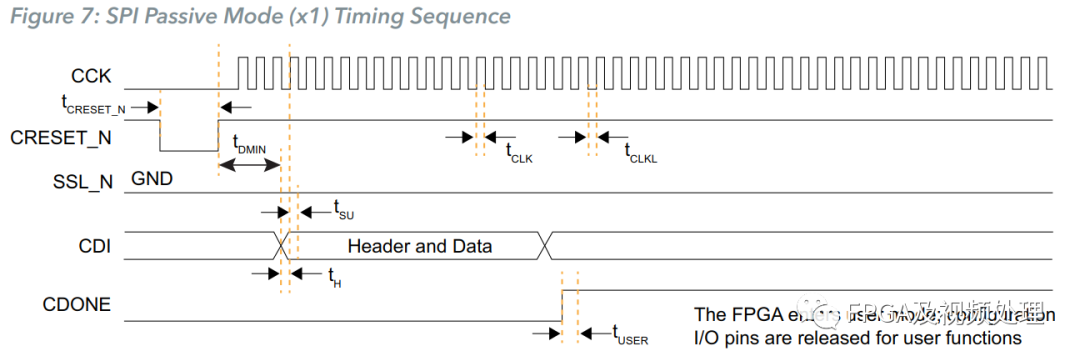

這里以X1模式為例,PS的配置過程如下:

(1)在啟動配置之前要先把CRESET_N拉低tCRESET_N,然后拉高;

(2)在CRESET_N拉高之后,要等待tDMIN,才可以發送同步碼,這期間可以翻轉CCK;

(3)發送同步碼,數據與時鐘為上升沿觸發;要求外部處理器連續發送數據直到數據完成;

(4)數據發送完成后,繼續發送CCK時鐘100周期,或者一邊發送一邊檢測CDONE,直到CDONE為高。實際上也確實有客戶因為沒有拉時鐘而啟動不了的情況。

控制信號處理

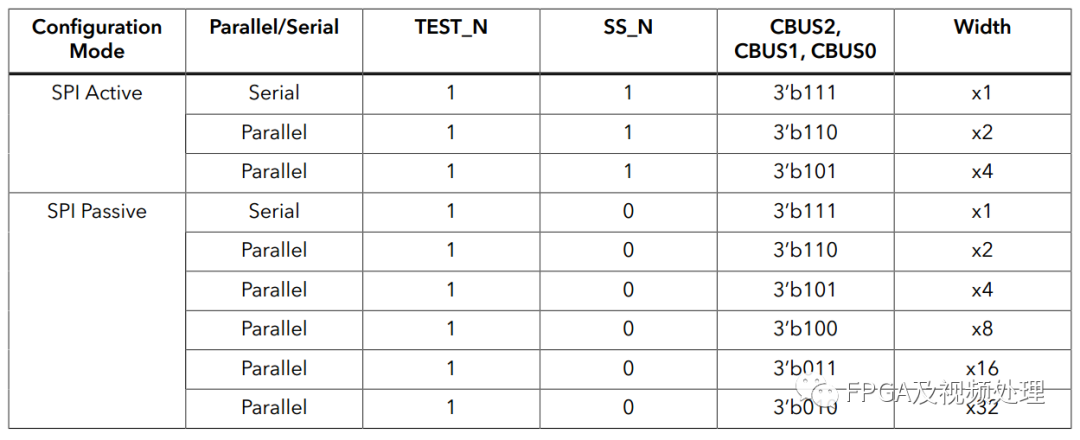

易靈思Trion FPGA的配置模塊主要由CBUS[2:0]、SS_N和TEST_N,CSI幾個信號控制。FPGA進入用戶模式前不要對這幾個信號進行翻轉。

目前易靈思的Programmer工具只支持PS x1模式,x2及更高位寬需要通過外部微處理器,如MCU來操作。

這里需要注意的是在配置過程中,控制信號不要進行翻轉,目前看到的現象是在多次配置過程中,在連續兩次配置過程中,由于CSI翻轉造成第二次配置失敗。

應用案例

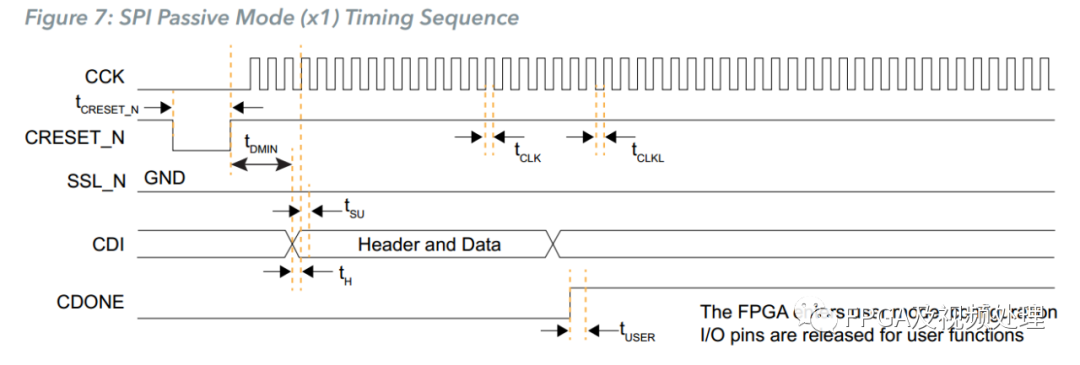

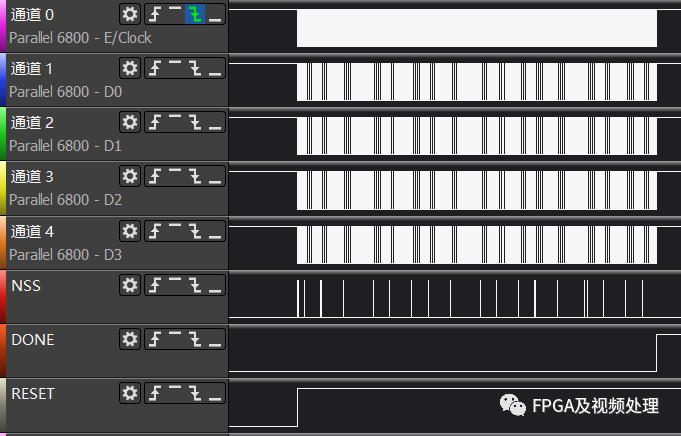

目前T20F169測試PS x4模式。時鐘為30MHz,tCRESET_N拉低790ns,tDMIN為2us,數據配置完成后又繼續發送時鐘100個以上。可以啟動。用時104ms

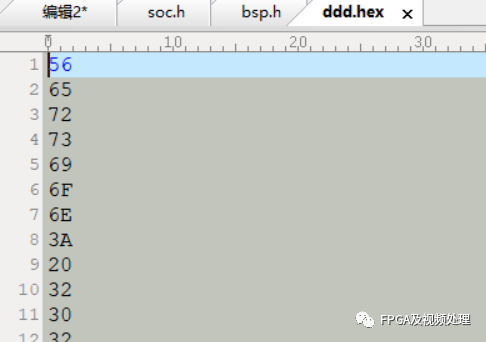

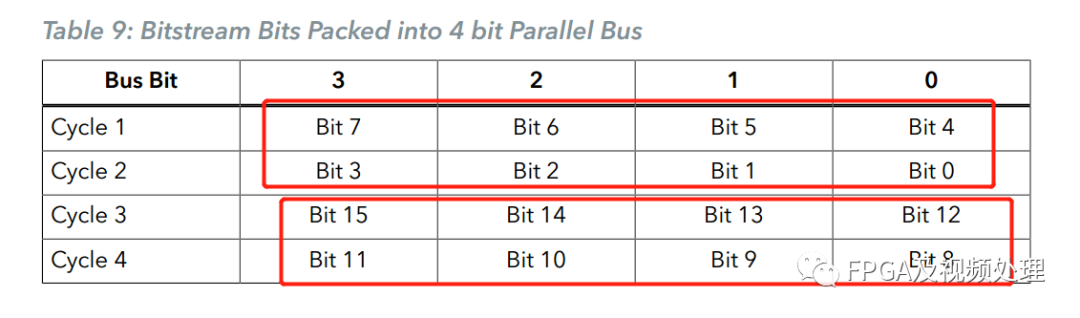

另外要提下數據順序問題,實際在發送過程是依次發送的。

整體配置過程波形如下,SS_N有時會有很多毛刺,時鐘之間也會有一些持續拉高的時間,但都不影響。

審核編輯 :李倩

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601883 -

控制信號

+關注

關注

0文章

162瀏覽量

11948 -

易靈思

+關注

關注

5文章

45瀏覽量

4852

原文標題:易靈思Trion FPGA PS配置模式--update(2)

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

固化FPGA配置芯片的方式

易靈思Trion FPGA PS配置模式--update(6)

FPGA的配置模式有哪些?具體配置過程是怎樣的?

Trion DSP 原語使用問題 - 1

Zynq-7000為何不是FPGA?

易靈思RAM使用--Update5

國產FPGA應用專題--易靈思Efinity軟件使用心得

易靈思RAM使用--Update4

易靈思Jtag_bridge_loader生成-v2

AMD進軍低成本FPGA市場,滿足邊緣應用需求

解析FPGA競爭格局背后的驅動因素

易靈思RAM使用--Update3

易靈思Trion FPGA PS配置模式--update

易靈思Trion FPGA PS配置模式--update

評論