先進(jìn)封裝的出現(xiàn),讓業(yè)界看到了通過(guò)封裝技術(shù)推動(dòng)芯片高密度集成、性能提升、體積微型化和成本下降的巨大潛力。隨著集成電路制造工藝沿著摩爾定律發(fā)展的步伐放緩,先進(jìn)封裝技術(shù)正成為集成電路產(chǎn)業(yè)發(fā)展的新引擎。

1. 集成電路與封裝的發(fā)展

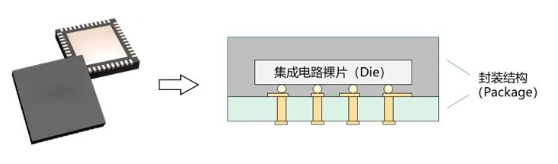

芯片由集成電路裸片(Die)與外圍封裝結(jié)構(gòu)組成,二者共同決定了芯片的性能。國(guó)際半導(dǎo)體技術(shù)路線(xiàn)圖(ITRS)指出,集成電路技術(shù)會(huì)沿More Moore(延續(xù)摩爾定律)和More than Moore(拓展摩爾定律)兩個(gè)方向發(fā)展。延續(xù)摩爾定律的技術(shù)路線(xiàn)主要關(guān)注減小晶體管尺寸、增加集成電路密度;而拓展摩爾定律技術(shù)路線(xiàn)則更關(guān)注利用封裝技術(shù)提高芯片和系統(tǒng)的集成度。

隨著先進(jìn)制程逐漸向原子尺寸逼近,短溝道效應(yīng)和量子隧穿效應(yīng)使晶體管的制造難度呈指數(shù)級(jí)增加。并且,隨著制程提高,整體成本會(huì)大幅增加,5nm芯片設(shè)計(jì)成本已經(jīng)是28nm芯片的8倍,這對(duì)于多數(shù)企業(yè)是難以承受的。縱觀(guān)全世界,僅有臺(tái)積電、三星和英特爾具備7nm制程工藝且有實(shí)力向3nm、2nm發(fā)展。因此,通過(guò)封裝技術(shù)降低成本,將系統(tǒng)微型化、多功能化成為芯片產(chǎn)業(yè)發(fā)展的新引擎動(dòng)力。

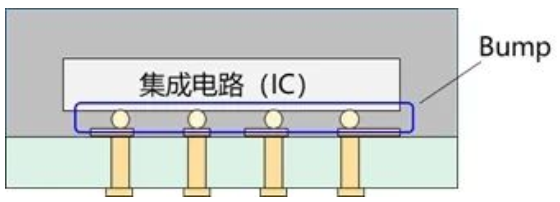

圖1 芯片結(jié)構(gòu)示意圖

2. 半導(dǎo)體封裝技術(shù)

封裝是將集成電路芯片包封在某一標(biāo)準(zhǔn)組件中的方法、結(jié)構(gòu)和工藝,具有保護(hù)、固定、密封以及增強(qiáng)芯片電熱性能的作用,是連接芯片與系統(tǒng)的橋梁,封裝后的芯片可作為標(biāo)準(zhǔn)組件安裝在印刷電路板(PCB)上實(shí)現(xiàn)應(yīng)用。

圖2 芯片封裝示意圖

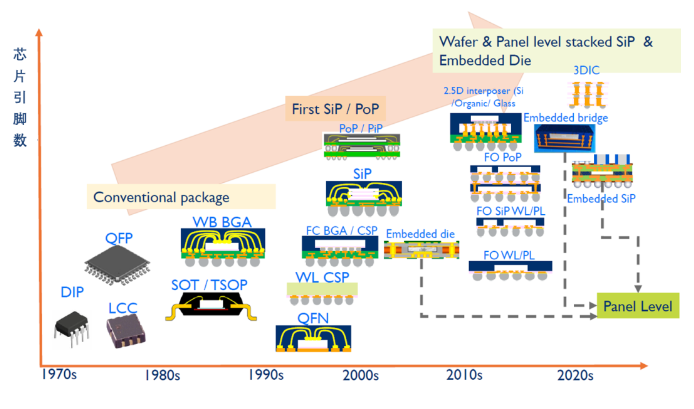

隨著半導(dǎo)體工藝的發(fā)展,芯片引腳數(shù)逐漸增加,封裝形式也由傳統(tǒng)封裝(引線(xiàn)框架作為載體,采用引線(xiàn)鍵合互連)向先進(jìn)封裝發(fā)展。在單芯片封裝方面,先進(jìn)封裝較傳統(tǒng)封裝提升了芯片的集成密度和電氣互聯(lián)速度,降低了設(shè)計(jì)門(mén)檻,優(yōu)化了功能搭配的靈活性。隨著封裝形式的多樣化、組合化發(fā)展,先進(jìn)封裝不僅指單芯片封裝,還包括將至少兩顆以上芯片集成在一起的系統(tǒng)級(jí)封裝(SiP)。

圖3 芯片封裝技術(shù)的發(fā)展(來(lái)源:yole)

表1 傳統(tǒng)封裝與先進(jìn)封裝

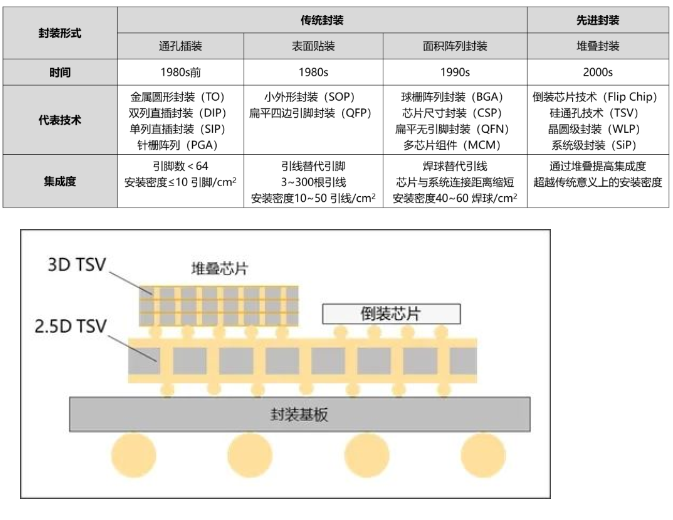

圖4 單芯片封裝與系統(tǒng)極封裝(SiP)

3. 先進(jìn)封裝技術(shù)解析

目前,先進(jìn)封裝包含的代表技術(shù)包括倒裝芯片技術(shù)(Flip Chip)、硅通孔技術(shù)(TSV)、晶圓級(jí)封裝(WLP)、系統(tǒng)級(jí)封裝(SiP)技術(shù)。

倒裝芯片技術(shù)(Flip Chip)

Flip Chip是將芯片通過(guò)bump(凸點(diǎn)結(jié)構(gòu))直接與封裝基板上的接口進(jìn)行連接。

圖5 Flip Chip示意圖

相比傳統(tǒng)引線(xiàn)鍵合封裝,倒裝主要有如下優(yōu)勢(shì):1)性能方面,可減少引線(xiàn)帶來(lái)的寄生電容,有利于提高頻率、改善電學(xué)及熱學(xué)性能;2)經(jīng)濟(jì)性方面,工藝簡(jiǎn)單,成本較低;3)空間方面,減小封裝體積,使封裝成品與芯片尺寸相當(dāng),實(shí)現(xiàn)芯片尺寸封裝(Chip-Size Packaging,CSP)。

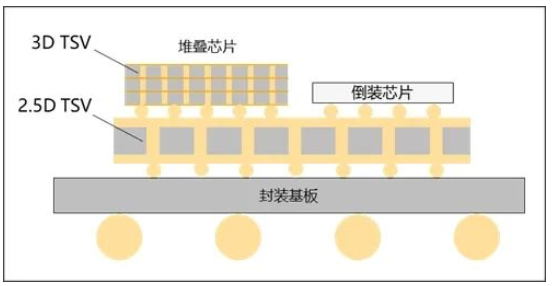

硅通孔技術(shù)(TSV)

TSV(Through Silicon Via, 硅通孔)技術(shù)主要用于立體封裝,在垂直方向?yàn)樾酒?a target="_blank">供電氣延伸和互連。按照集成類(lèi)型的不同TSV分為2.5D和3D,2.5D通孔位于中介層,而3D通孔貫穿芯片本身,直接連接上下層芯片。

3D TSV技術(shù)使上下兩片結(jié)構(gòu)相同的芯片直接連接,從而實(shí)現(xiàn)大帶寬、低時(shí)延的數(shù)據(jù)傳輸。這一特性與存儲(chǔ)芯片的需求極度匹配,可提高存儲(chǔ)芯片間的傳輸速度并降低功耗,已被大量應(yīng)用于高端Flash和DRAM堆疊中。

2.5D TSV技術(shù)可以為同一封裝體內(nèi)的多個(gè)芯片提供大帶寬、低時(shí)延的數(shù)據(jù)傳輸,與3D TSV結(jié)合的封裝方式,已被大量應(yīng)用于CPU、GPC當(dāng)中。

圖6 TSV技術(shù)示意圖

晶圓級(jí)封裝(WLP)

傳統(tǒng)封裝工藝是先將晶圓切割為裸片再進(jìn)行封裝,而晶圓級(jí)封裝是先進(jìn)行封裝再切割。晶圓級(jí)封裝能明顯縮小芯片封裝后的尺寸,還能提升數(shù)據(jù)傳輸?shù)乃俣扰c穩(wěn)定性,被廣泛應(yīng)用于消費(fèi)電子芯片。

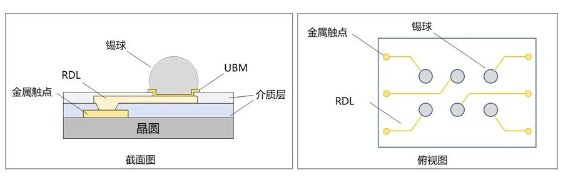

RDL(ReDistribution Layer)重布線(xiàn)層作為晶圓級(jí)封裝中的核心技術(shù),起著XY平面電氣延伸和互聯(lián)的作用。在芯片設(shè)計(jì)和制造時(shí),IO端口一般分布在芯片的邊沿或者四周,為了便于與外界相連,需要在晶圓表面沉積金屬層和相應(yīng)的介質(zhì)層,并形成金屬布線(xiàn),將IO端口重新排布到位置較寬松的區(qū)域,并形成面陣列排布。

圖7 RDL技術(shù)示意圖

系統(tǒng)級(jí)封裝(SiP)

SiP(System in Package,系統(tǒng)級(jí)封裝)將多個(gè)具有不同功能的有源電子元件(通常是裸芯片)、無(wú)源器件及其他器件(MEMS或光學(xué)器件等)構(gòu)成一個(gè)系統(tǒng)或子系統(tǒng),并將多個(gè)系統(tǒng)組裝到一個(gè)封裝體內(nèi)部,使其成為具有一定功能的單體封裝件。從連接方式上看,倒裝(FC)、重布線(xiàn)(RDL)和嵌入式(Embedded Die)是實(shí)現(xiàn)SiP的三條常見(jiàn)技術(shù)路線(xiàn)。

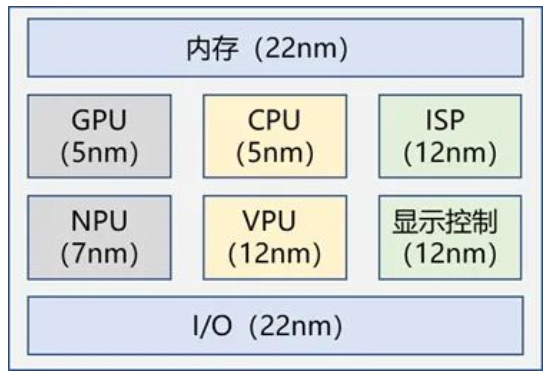

Chiplet技術(shù)是如今被廣泛研究的SiP技術(shù),它將單顆芯片的各功能區(qū)分解成多顆獨(dú)立的芯片,并通過(guò)封裝技術(shù)重新組成一個(gè)完整的系統(tǒng)。與傳統(tǒng)的單一芯片相比,采用Chiplet技術(shù)的單顆芯片面積較小,可提高制造良率和實(shí)現(xiàn)異構(gòu)集成。

圖8 Chiplet技術(shù)示意圖

4. 先進(jìn)封裝的應(yīng)用案例

半導(dǎo)體行業(yè)已經(jīng)基本實(shí)現(xiàn)分工精細(xì)化,產(chǎn)業(yè)鏈主要由設(shè)計(jì)、生產(chǎn)、封測(cè)等環(huán)節(jié)組成。先進(jìn)封裝推動(dòng)前后道工藝相互滲透融合,具有較高技術(shù)壁壘和技術(shù)積累的廠(chǎng)商會(huì)向上下游工序延伸。如今,前、后道的頭部廠(chǎng)商憑借各自?xún)?yōu)勢(shì)入局,成為先進(jìn)封裝行業(yè)的主力軍,其中,前道主要有英特爾、三星、臺(tái)積電,后道主要有日月光、安靠、長(zhǎng)電科技等。

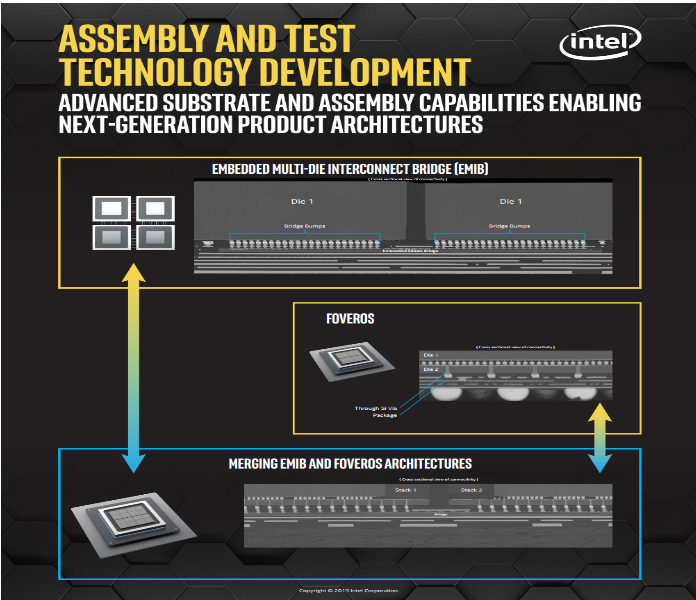

以英特爾為例,作為IDM代表性企業(yè),在先進(jìn)封裝領(lǐng)域也不斷推陳出新,而先進(jìn)封裝也是英特爾IDM2.0計(jì)劃的關(guān)鍵點(diǎn)之一[7](圖11)。2017年,英特爾推出的EMIB(Embedded Multi-die Interconnect Bridge 嵌入式多核心互聯(lián)橋接)是其推進(jìn)先進(jìn)封裝的重要一步。EMIB封裝技術(shù)可以根據(jù)需要將CPU、IO、GPU甚至FPGA、AI等芯片封裝到一起,能夠把10nm、14nm、22nm等多種不同工藝的芯片封裝在一起做成單一芯片,適應(yīng)靈活的業(yè)務(wù)的需求。2019年,英特爾推出Foveros技術(shù),開(kāi)始將芯片豎直堆疊,進(jìn)行橫向和縱向之間的互連,一定意義上實(shí)現(xiàn)了3D堆疊。緊接著,在2019年的SEMICON West上,英特爾又將EMIB與Foveros技術(shù)結(jié)合。

圖9 英特爾先進(jìn)封裝技術(shù) (來(lái)源:英特爾官網(wǎng))

總結(jié)

當(dāng)前半導(dǎo)體領(lǐng)域處于高速發(fā)展的新階段,先進(jìn)封裝是后摩爾時(shí)代系統(tǒng)集成與功能融合的關(guān)鍵路徑,成為芯片制造與封裝企業(yè)的新賽道,國(guó)內(nèi)企業(yè)需抓住機(jī)會(huì),在不斷追趕國(guó)際半導(dǎo)體制造先進(jìn)制程的同時(shí),大力發(fā)展先進(jìn)封裝技術(shù),在芯片制造領(lǐng)域縮短與世界領(lǐng)先水平的距離。

-

集成電路

+關(guān)注

關(guān)注

5382文章

11396瀏覽量

360953

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

集成電路封裝技術(shù)專(zhuān)題 通知

先進(jìn)封裝技術(shù)的發(fā)展趨勢(shì)

中國(guó)半導(dǎo)體封裝技術(shù)有望實(shí)現(xiàn)“彎道超車(chē)”

華進(jìn)半導(dǎo)體作為國(guó)家級(jí)先進(jìn)封裝技術(shù)研發(fā)中心的探索之路

半導(dǎo)體先進(jìn)封裝技術(shù)峰會(huì)與您3月春天見(jiàn),向未來(lái)再出發(fā)!

多家半導(dǎo)體知名企業(yè)齊聚深圳,亮相先進(jìn)封裝技術(shù)發(fā)展大會(huì)!

半導(dǎo)體封裝技術(shù)研究

什么是先進(jìn)封裝技術(shù)的核心

什么是先進(jìn)封裝?先進(jìn)封裝技術(shù)包括哪些技術(shù)

半導(dǎo)體先進(jìn)封裝技術(shù)

半導(dǎo)體封裝技術(shù)的可靠性挑戰(zhàn)與解決方案

半導(dǎo)體封裝技術(shù)的類(lèi)型和區(qū)別

人工智能半導(dǎo)體及先進(jìn)封裝技術(shù)發(fā)展趨勢(shì)

淺談半導(dǎo)體封裝技術(shù)和先進(jìn)封裝技術(shù)解析

淺談半導(dǎo)體封裝技術(shù)和先進(jìn)封裝技術(shù)解析

評(píng)論