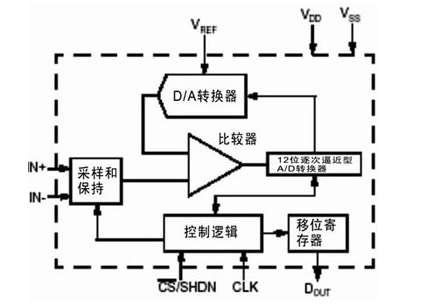

當(dāng)今的信號處理系統(tǒng)普遍需要使用混合信號器件,例如為了處理寬動(dòng)態(tài)范圍的模擬信號,高速高性能的ADC信號顯得更加重要。為了在惡劣的數(shù)字環(huán)境中保持模擬信號寬動(dòng)態(tài)范圍和低噪聲,就要熟知PCB布線技巧以進(jìn)行良好的高速電路設(shè)計(jì)。本文將為您闡述使用高速轉(zhuǎn)換器時(shí),必須遵循的那些重要PCB布局布線規(guī)則。

AGND和DGND接地層應(yīng)當(dāng)分離嗎?

簡單回答是視情況而定,詳細(xì)回答則是通常不分離。因?yàn)樵诖蠖鄶?shù)情況下,分離接地層只會(huì)增加返回電流的電感,它所帶來的壞處大于好處。從公式V = L(di/dt)可以看出,隨著電感增加,電壓噪聲會(huì)提高。而隨著開關(guān)電流增大(因?yàn)?a target="_blank">轉(zhuǎn)換器采樣速率提高),電壓噪聲同樣會(huì)提高。因此,接地層應(yīng)當(dāng)連在一起。

一個(gè)例子是,在一些應(yīng)用中,為了符合傳統(tǒng)設(shè)計(jì)要求,必須將臟亂的總線電源或數(shù)字電路放在某些區(qū)域,同時(shí)還受尺寸限制的影響,使得電路板無法實(shí)現(xiàn)良好的布局分割,在這種情況下,分離接地層是實(shí)現(xiàn)良好性能的關(guān)鍵。然而,為使整體設(shè)計(jì)有效,必須在電路板的某個(gè)地方通過一個(gè)電橋或連接點(diǎn)將這些接地層連在一起。因此,應(yīng)將連接點(diǎn)均勻地分布在分離的接地層上。最終,PCB上往往會(huì)有一個(gè)連接點(diǎn)成為返回電流通過而不會(huì)導(dǎo)致性能降低的最佳位置。此連接點(diǎn)通常位于轉(zhuǎn)換器附近或下方。

設(shè)計(jì)電源層時(shí),應(yīng)使用這些層可以使用的所有銅線。如果可能,請勿讓這些層共用走線,因?yàn)轭~外的走線和過孔會(huì)將電源層分割成較小的碎塊,從而迅速損害電源層。由此產(chǎn)生的稀疏電源層可以將電流路徑擠壓到最需要這些路徑的地方,即轉(zhuǎn)換器的電源引腳。擠壓過孔與走線之間的電流會(huì)提高電阻,導(dǎo)致轉(zhuǎn)換器的電源引腳發(fā)生輕微的壓降。

最后,電源層的放置至關(guān)重要,切勿將高噪聲的數(shù)字電源層疊放在模擬電源層上,否則二者雖然位于不同的層,但仍有可能耦合。為將系統(tǒng)性能下降的風(fēng)險(xiǎn)降至最低,設(shè)計(jì)中應(yīng)盡可能將這些類型的層隔開而不是疊加在一起。

PCB的輸電系統(tǒng)(PDS)設(shè)計(jì)能忽略嗎?

PDS的設(shè)計(jì)目標(biāo)是將響應(yīng)電源電流需求而產(chǎn)生的電壓紋波降至最低。所有電路都需要電流,有些電路需求量較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的PCB層疊,可以將因電路的電流需求而產(chǎn)生的電壓紋波降至最低。例如,如果設(shè)計(jì)的開關(guān)電流為1A,PDS的阻抗為10mΩ,則最大電壓紋波為10mV。

首先,應(yīng)當(dāng)設(shè)計(jì)一個(gè)支持較大層電容的PCB層疊結(jié)構(gòu)。例如,六層堆疊可能包含頂部信號層、第一接地層、第一電源層、第二電源層、第二接地層和底部信號層。規(guī)定第一接地層和第一電源層在層疊結(jié)構(gòu)中彼此靠近,這兩層間距為2到3密爾,形成一個(gè)固有層電容。此電容的最大優(yōu)點(diǎn)是它是免費(fèi)的,只需在PCB制造筆記中注明。如果必須分割電源層,同一層上有多個(gè)VDD電源軌,則應(yīng)使用盡可能大的電源層。不要留下空洞,同時(shí)也應(yīng)注意敏感電路。這將使該VDD層的電容最大。如果設(shè)計(jì)允許存在額外的層,則應(yīng)將兩個(gè)額外的接地層放在第一和第二電源層之間。在核心間距同樣為2到3密爾的情況下,此時(shí)層疊結(jié)構(gòu)的固有電容將加倍。

對于理想的PCB層疊,電源層起始入口點(diǎn)和DUT周圍均應(yīng)使用去耦電容,這將確保PDS阻抗在整個(gè)頻率范圍內(nèi)均較低。使用若干0.001μF至100μF的電容有助于覆蓋該范圍。沒有必要各處都配置電容;電容正對著DUT對接會(huì)破壞所有的制造規(guī)則。如果需要這種嚴(yán)厲的措施,則說明電路存在其它問題。

裸露焊盤(E-Pad)的重要性

這是一個(gè)容易忽視的方面,但它對于實(shí)現(xiàn)PCB設(shè)計(jì)的最佳性能和散熱至關(guān)重要。

裸露焊盤(引腳0)指的是大多數(shù)現(xiàn)代高速IC下方的一個(gè)焊盤,它是一個(gè)重要的連接,芯片的所有內(nèi)部接地都是通過它連接到器件下方的中心點(diǎn)。裸露焊盤的存在使許多轉(zhuǎn)換器和放大器可以省去接地引腳。關(guān)鍵是將該焊盤焊接到PCB時(shí),要形成穩(wěn)定可靠的電氣連接和散熱連接,否則系統(tǒng)可能會(huì)遭到嚴(yán)重破壞。

通過以下三個(gè)步驟,可以實(shí)現(xiàn)裸露焊盤的最佳電氣和散熱連接。首先,在可能的情況下,應(yīng)在各PCB層上復(fù)制裸露焊盤,這將為所有接地提供較厚的散熱連接,從而快速散熱,對于高功耗器件尤其重要。在電氣方面,這將為所有接地層提供良好的等電位連接。在底層上復(fù)制裸露焊盤時(shí),它可以用作去耦接地點(diǎn)和安裝散熱器的地方。

其次,將裸露焊盤分割成多個(gè)相同的部分。以棋盤狀最佳,可以通過絲網(wǎng)交叉格柵或焊罩來實(shí)現(xiàn)。在回流焊組裝過程中,無法決定焊膏如何流動(dòng)以建立器件與PCB的連接,因此連接可能存在,但分布不均,更糟糕的情況是連接很小并且位于拐角處。將裸露焊盤分割為若干較小的部分可以使各個(gè)區(qū)域都有一個(gè)連接點(diǎn),從而確保器件與PCB之間形成可靠、均勻的連接。

最后,應(yīng)當(dāng)確保各部分都有過孔連接到地。各區(qū)域通常都很大,足以放置多個(gè)過孔。組裝之前,務(wù)必用焊膏或環(huán)氧樹脂填充每個(gè)過孔,這一步非常重要,這樣才能確保裸露焊盤焊膏不會(huì)回流到過孔空洞中,否則會(huì)降低正確連接的機(jī)率。

PCB中各層面之間交叉耦合的問題

在PCB設(shè)計(jì)中,一些高速轉(zhuǎn)換器的布局布線不可避免地會(huì)出現(xiàn)一個(gè)電路層與另一個(gè)交疊的情況。某些情況下,敏感的模擬層(電源、接地或信號)可能就在高噪聲數(shù)字層的正上方。大多數(shù)設(shè)計(jì)人員認(rèn)為這無關(guān)緊要,因?yàn)檫@些層面位于不同的層。是否如此呢?我們來看一個(gè)簡單的測試。

選擇相鄰層中的一層,并在該層面注入信號,然后,將交叉耦合層連接到一個(gè)頻譜分析儀。可以看到,耦合到相鄰層的信號非常多。即使間距40密爾,某種意義上相鄰 層仍會(huì)形成一個(gè)電容,因此在某些頻率下,信號仍會(huì)從一個(gè)層耦合到另一個(gè)層。

假設(shè)某層上的高噪聲數(shù)字部分具有高速開關(guān)的1V信號,層間隔離為60dB時(shí),非受驅(qū)層將看到從受驅(qū)層耦合而來的1mV信號。對于2Vp-p滿量程擺幅的12位模數(shù)轉(zhuǎn)換器 (ADC)而言,這意味著2LSB(最低有效位)的耦合。對于特定的系統(tǒng),這可能不成問題, 但應(yīng)注意,當(dāng)分辨率從12位提高到14位時(shí),靈敏度會(huì)提高四倍,因而誤差將增大到8LSB。

忽略交叉面/交叉層耦合可能不會(huì)導(dǎo)致系統(tǒng)設(shè)計(jì)失敗,或者削弱設(shè)計(jì),但必須保持警惕,因?yàn)閮蓚€(gè)層面之間的耦合可能比想象的要多。

在目標(biāo)頻譜內(nèi)發(fā)現(xiàn)噪聲雜散耦合時(shí),應(yīng)注意這一點(diǎn)。有時(shí)候,布局布線會(huì)導(dǎo)致非預(yù)期 信號或?qū)咏徊骜詈现敛煌瑢印U{(diào)試敏感系統(tǒng)時(shí)請記住這一點(diǎn):問題可能出在下面一層。

對于高速轉(zhuǎn)換器電路PCB設(shè)計(jì),你有哪些布線經(jīng)驗(yàn)分享呢?歡迎留言,與我們一起探討。

原文標(biāo)題:硬核分享,使用高速轉(zhuǎn)換器時(shí)應(yīng)遵循哪些重要的PCB布線規(guī)則?

文章出處:【微信公眾號:亞德諾半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

adc

+關(guān)注

關(guān)注

98文章

6430瀏覽量

544078 -

PCB布線

+關(guān)注

關(guān)注

20文章

463瀏覽量

42028 -

高速轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

27瀏覽量

11807

原文標(biāo)題:硬核分享,使用高速轉(zhuǎn)換器時(shí)應(yīng)遵循哪些重要的PCB布線規(guī)則?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

高速數(shù)據(jù)轉(zhuǎn)換器專業(yè)版GUI

高速數(shù)模轉(zhuǎn)換器基礎(chǔ)知識

高速模數(shù)轉(zhuǎn)換器基礎(chǔ)知識

如何為電源轉(zhuǎn)換器進(jìn)行PCB建模

高速數(shù)據(jù)轉(zhuǎn)換器的高效PoL電源設(shè)計(jì)

汽車直流/直流轉(zhuǎn)換器的 PCB 熱設(shè)計(jì)技巧

改善升壓轉(zhuǎn)換器PCB布局的五個(gè)步驟

高速pcb布線規(guī)則有哪些

模擬工程師電路設(shè)計(jì)指導(dǎo)手冊:數(shù)據(jù)轉(zhuǎn)換器

A/D轉(zhuǎn)換器所需的PCB布線策略

如何設(shè)計(jì)交流到直流轉(zhuǎn)換器電路

LLC諧振轉(zhuǎn)換器設(shè)計(jì)和PCB布局布線基本技巧概述

高速ADC PCB布局布線技巧分享

DC/DC轉(zhuǎn)換器電路設(shè)計(jì)的技巧分享

高速轉(zhuǎn)換器組表征高速數(shù)模轉(zhuǎn)換器(DAC)的性能測試方法

高速轉(zhuǎn)換器電路設(shè)計(jì)的PCB布線技巧

高速轉(zhuǎn)換器電路設(shè)計(jì)的PCB布線技巧

評論