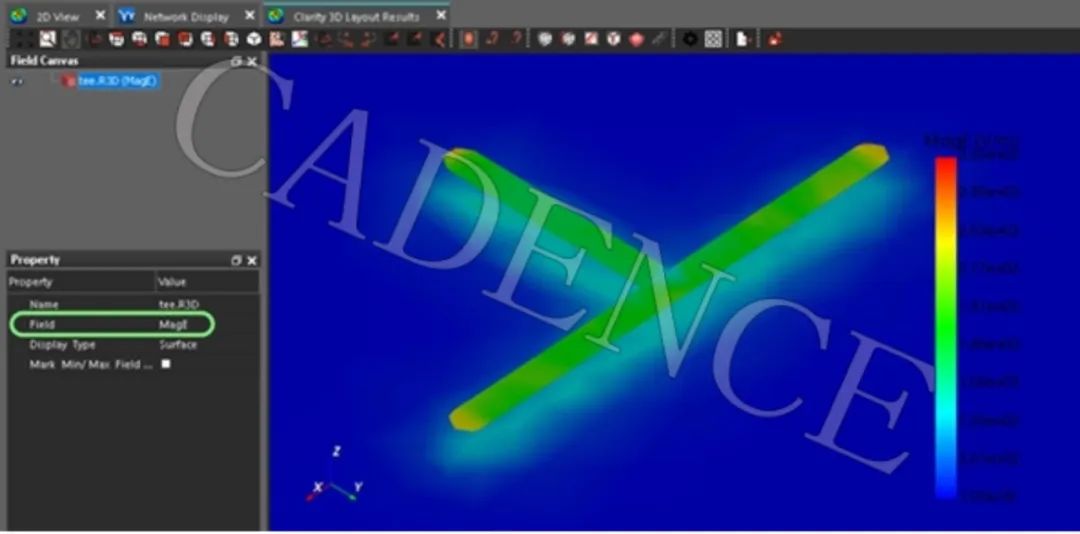

Cadence Clarity 3D Solver 2022版本發(fā)布電磁設(shè)計同步分析功能提高效率

最新的電磁設(shè)計同步分析功能有助于提高 IC、IC 封裝和高性能 PCB 設(shè)計的速度。

美國加州圣何塞(DesignCon)—楷登電子(Cadence Design Systems, Inc.)在近期結(jié)束的 DesignCon 2022 展會上發(fā)布了用于 IC、IC 封裝和高性能 PCB 設(shè)計電磁 (EM) 設(shè)計中同步分析的 Cadence? Clarity? 3D Solver 最新版本。該版本的新功能和工作流程包括:

新的分布式網(wǎng)格劃分功能,可提供至少 10 倍性能

基于人工智能和機器學(xué)習(xí) (AI/ML) 的優(yōu)化功能,有助于快速有效地探索設(shè)計空間并實現(xiàn)最佳設(shè)計

實現(xiàn)與 Cadence Allegro? /Allegro Package Designer Plus、Integrity? 3D-IC、Virtuoso? RF 和 AWR? 微波/射頻平臺無縫集成的工作流程

“

用于 IC 封裝和高性能 PCB 設(shè)計的電磁 (EM) 分析的范圍和復(fù)雜性日益增長,對于中介層和剛?cè)峤Y(jié)合的應(yīng)用來說更是如此。

越來越多的客戶依靠 Cadence Clarity 3D Solver 的速度、精確度和仿真能力來按期完成這些充滿挑戰(zhàn)性的設(shè)計。

——Cadence 多物理場系統(tǒng)分析業(yè)務(wù)部副總裁 Ben Gu

分布式網(wǎng)格劃分

Clarity 3D Solver 新增了分布式網(wǎng)格劃分算法,進一步發(fā)展了其先進的網(wǎng)格劃分技術(shù),包括基于層結(jié)構(gòu)的 LMesh 和任意三維結(jié)構(gòu)的XMesh 兩種方法。這兩種技術(shù)都能將初始網(wǎng)格處理速度提高 10 倍以上,意味著大幅減少的仿真運行時間。

3D-IC 的設(shè)計復(fù)雜性正在不斷增加,對于先進的球柵陣列 (BGA) 基板設(shè)計,我們需要一個更好的網(wǎng)格劃分工具,以確保 3D 有限元法 (FEM) 的提取效率。

與 Clarity 3D Solver 中采用的傳統(tǒng)網(wǎng)格劃分工具相比,我們看到新引入的 XMesh 方法大大減少了高級封裝設(shè)計中的網(wǎng)格劃分時間,此外,還提升了完整模型提取過程中的性能。

——GUC 高速信號和熱仿真部總監(jiān) Stephen Chen 博士

基于 AI 技術(shù)的優(yōu)化

工程師通常利用極其耗費資源和時間的參數(shù)化掃描來優(yōu)化設(shè)計的物理結(jié)構(gòu)和電氣特性。采用了新的 AI/ML 技術(shù)后,Clarity 3D Solver 顯著提高了設(shè)計師的生產(chǎn)力和分析效率,從而可以專心致志實現(xiàn)設(shè)計目標(biāo)。

工作流程

Clarity 3D Solver 依然被集成在 Allegro/Allegro Package Designer Plus、Integrity 3D-IC、Virtuoso RF 和 AWR 微波/射頻平臺中,為設(shè)計師提供無縫的電磁設(shè)計同步分析解決方案,幫助客戶加快從概念到生產(chǎn)的工作流程。

-

Cadence

+關(guān)注

關(guān)注

64文章

915瀏覽量

141868 -

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4670瀏覽量

85290 -

IC封裝

+關(guān)注

關(guān)注

4文章

185瀏覽量

26697 -

電磁設(shè)計

+關(guān)注

關(guān)注

0文章

13瀏覽量

7396

發(fā)布評論請先 登錄

相關(guān)推薦

藍牙定位系統(tǒng):實現(xiàn)精準(zhǔn)定位、提高效率的利器

D類放大器中用于提高效率的 Y 橋應(yīng)用說明

維愛普3D打印設(shè)備工字電感磁芯:驅(qū)動創(chuàng)新與高效的科技核心

取得平衡:可提高效率并控制EMI的汽車設(shè)計

電源設(shè)計:同步整流帶來的不僅僅是高效率

24V/8A大功率低功耗高效率同步整流升壓芯片

提高效率的DC電源模塊設(shè)計技巧

什么是電源模塊效率 如何計算 提高效率的方法

搬運機器人已經(jīng)成為提高效率、降低成本的關(guān)鍵技術(shù)

SOLIDWORKS 3D CAD 2024的10大新增功能

系統(tǒng)分析大講堂:Clarity 3D Solver 課程新內(nèi)容

Cadence AI 驅(qū)動的多物理場系統(tǒng)分析解決方案助力緯創(chuàng)大幅提升產(chǎn)品開發(fā)速度

Clarity 3D Workbench仿真USB2.0實例

洞悉 Omniverse:Autodesk Maya 的 OpenUSD 增強功能讓 3D 工作流變得簡單高效

Cadence Clarity 3D Solver 2022版本發(fā)布 電磁設(shè)計同步分析功能提高效率

Cadence Clarity 3D Solver 2022版本發(fā)布 電磁設(shè)計同步分析功能提高效率

評論