SystemVerilog常用可綜合IP模塊庫(kù)

想擁有自己的SystemVerilog IP庫(kù)嗎?設(shè)計(jì)時(shí)一個(gè)快捷鍵就能集成到自己的設(shè)計(jì),酷炫的設(shè)計(jì)你也可以擁有!

每個(gè)公司應(yīng)該都會(huì)維護(hù)屬于自己公司風(fēng)格的IP庫(kù),作為個(gè)人學(xué)習(xí)或者持續(xù)使用的方式,這種方法很有用。今天肯定不是分享我司的IP庫(kù),而是一個(gè)開源庫(kù),每個(gè)人都可以使用、維護(hù)或者修改,當(dāng)然作為學(xué)習(xí)(多人維護(hù))也是不可多得的資料。把該庫(kù)集成到自己常用的文本編輯器(SublimeVScodeVim等等)可以很快完成代碼設(shè)計(jì)。

簡(jiǎn)介

這是verilog/systemverilog 可綜合模塊的集合。

所有代碼在典型的 FPGA 和主流 FPGA 供應(yīng)商中都具有高度可重用性。

本項(xiàng)目是幾個(gè)常用可綜合模塊集合的集合,下面分別介紹這些項(xiàng)目。

工程鏈接

?https://github.com/suisuisi/basic_systemverilog

詳細(xì)介紹

basic_verilog

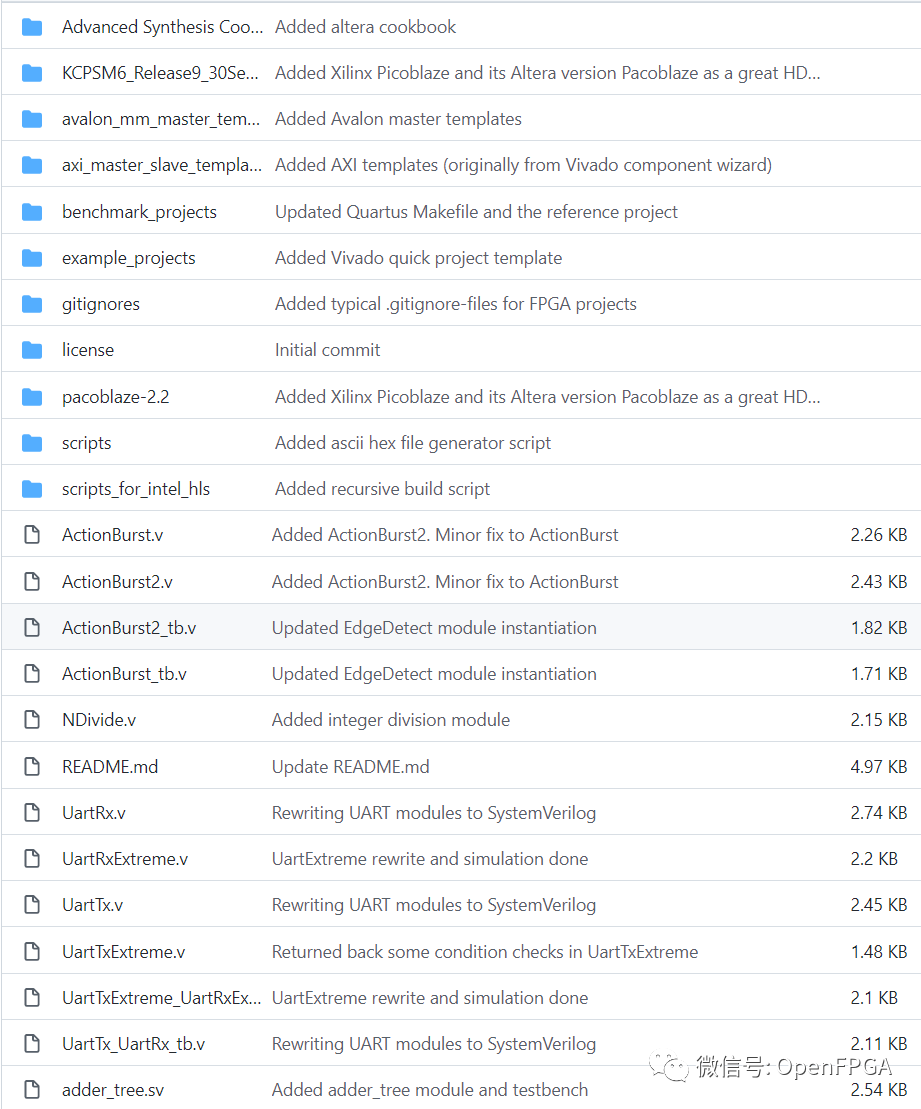

文件夾外的文件根據(jù)文件名很容易判斷其用途,下面著重介紹文件夾內(nèi)部文件:

| 目錄 | 描述 |

|---|---|

| Advanced Synthesis Cookbook/ | Altera cookbook中的有用代碼 |

| KCPSM6_Release9_30Sept14/ | Xilinx 的 Picoblaze 軟處理器 |

| pacoblaze-2.2/ | 適用于 Altera 器件的 Picoblaze 版本 |

| example_projects/ | FPGA 項(xiàng)目示例 |

| benchmark_projects/ | 多種 FPGA 類型的編譯時(shí)間基準(zhǔn) |

| scripts/ | 有用的 TCL 腳本 |

注1:cookbook:類似技巧大全的意思

這里還有一個(gè)TCL腳本文件,再簡(jiǎn)單介紹一下:

| 腳本 | 描述 |

|---|---|

| scripts/allow_undefined_ports.tcl | 允許為 Vivado IDE 生成帶有未定義引腳的測(cè)試項(xiàng)目 |

| scripts/compile_quartus.tcl | Quartus IDE 中用于命令行項(xiàng)目編譯的樣板腳本 |

| scripts/convert_sof_to_jam.bat | Altera/Intel FPGA 配置文件轉(zhuǎn)換器 |

| scripts/convert_sof_to_rbf.bat | 另一個(gè) Altera/Intel FPGA 配置文件轉(zhuǎn)換器 |

| scripts/iverilog_compile.tcl | 使用 iverilog 工具編譯 Verilog 源代碼并在 gtkwave 工具中運(yùn)行模擬的完整腳本 |

| scripts/modelsim_compile.tclModelsim | 無項(xiàng)目模式編譯腳本 |

| scripts/post_flow_quartus.tcl | 英特爾 Quartus IDE 的自定義報(bào)告或報(bào)告分析 |

| scripts/post_flow_vivado.tcl | Xilinx Vivado IDE 的自定義報(bào)告或報(bào)告分析 |

| scripts/program_all.bat | Altera/Intel FPGA 的命令行編程器示例 |

| scripts/project_version_auto_increment.tcl | Quartus IDE 的項(xiàng)目版本自動(dòng)增量腳本 |

| scripts/quartus_system_console_init.tcl | 通過 JTAG-to-Avalon-MM 橋 IP 讀/寫 Avalon-MM 的初始化腳本 |

| scripts/set_project_directory.tcl | 更改當(dāng)前目錄以匹配 Vivado IDE 中的項(xiàng)目目錄 |

| scripts/write_avalon_mm_from_file.tcl | 通過 JTAG-to-Avalon-MM 橋 IP 將二進(jìn)制文件中的批量二進(jìn)制數(shù)據(jù)寫入 Avalon-MM |

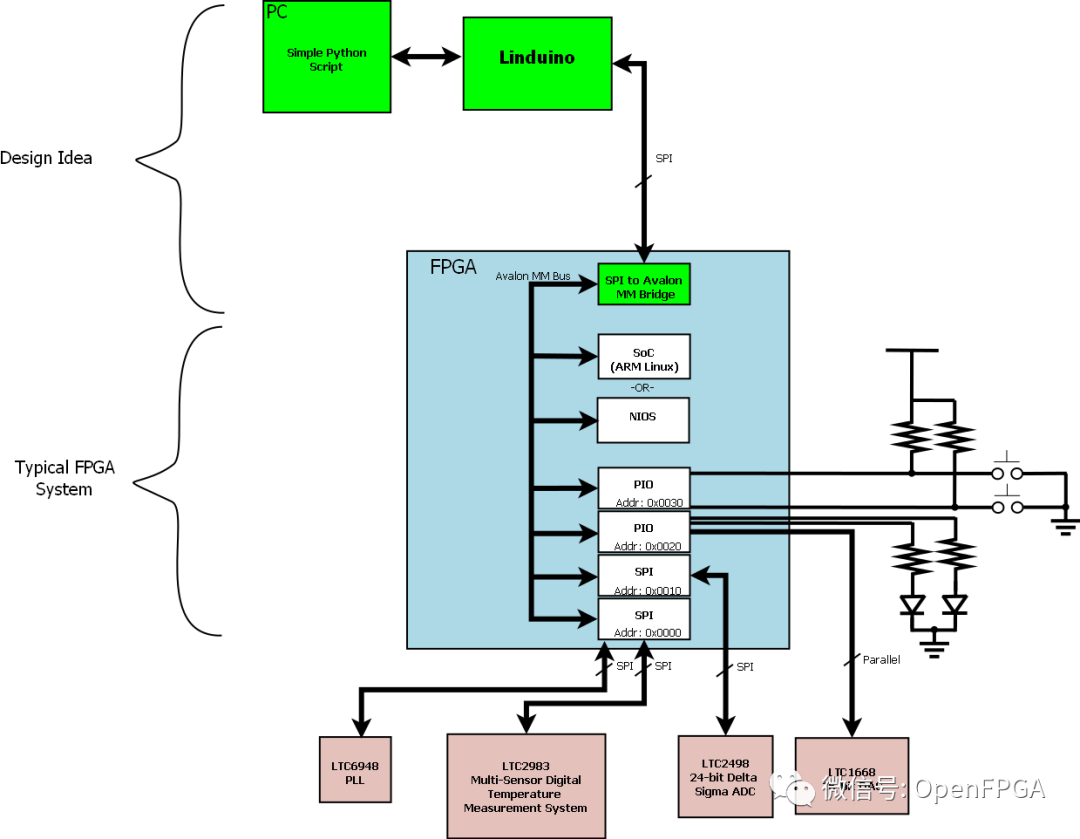

注2:Avalon:ALTERA公司FPGA內(nèi)部使用的總線,下圖是典型Altera FPGA系統(tǒng)

其他模塊說明

| 腳本 | 描述 |

|---|---|

| ActionBurst.v | 多通道一次性觸發(fā)模塊 |

| ActionBurst2.v | 可變步長(zhǎng)的多通道一次性觸發(fā) |

| adder_tree.sv | 將多個(gè)值并行相加 |

| bin2gray.sv | 格雷碼到二進(jìn)制轉(zhuǎn)換器 |

| bin2pos.sv | 將二進(jìn)制編碼值轉(zhuǎn)換為one-hot代碼 |

| clk_divider.sv | 寬參考時(shí)鐘分頻器 |

| debounce.v | 輸入按鈕的兩周期去抖動(dòng) |

| delay.sv | 用于產(chǎn)生靜態(tài)延遲或跨時(shí)鐘域同步的有用模塊 |

| dynamic_delay.sv | 任意輸入信號(hào)的動(dòng)態(tài)延遲 |

| edge_detect.sv | 組合邊沿檢測(cè)器,在每個(gè)信號(hào)邊沿上提供一個(gè)滴答脈沖 |

| lifo.sv | 單時(shí)鐘 LIFO 緩沖器(堆棧)實(shí)現(xiàn) |

| NDivide.v | 原始整數(shù)除法器 |

| prbs_gen_chk.sv | PRBS 模式生成器或檢查器 |

| pulse_gen.sv | 產(chǎn)生具有給定寬度和延遲的脈沖 |

| spi_master.sv | 通用spi主模塊 |

| UartRx.v | 簡(jiǎn)單明了的 UART 接收器 |

| UARTTX.v | 簡(jiǎn)單明了的 UART 發(fā)送器 |

| uart_rx_shifter.sv | 類似 UART 的接收器移位器,用于 FPGA 內(nèi)部或 FPGA 之間的簡(jiǎn)單同步消息傳遞 |

| uart_rx_shifter.sv | 類似 UART 的接收器移位器,用于 FPGA 內(nèi)部或 FPGA 之間的簡(jiǎn)單同步消息傳遞 |

| UartRxExtreme.v | 極小的 UART 接收器實(shí)現(xiàn) |

| UartTxExtreme.v | 極小的 UART 發(fā)送器實(shí)現(xiàn) |

| ... | ... |

generic_systemverilog_designs_library

- binary_counter

SystemVerilog 中具有異步復(fù)位的 n 位二進(jìn)制計(jì)數(shù)器。

- binary_to_gray

SystemVerilog中的n位二進(jìn)制到格雷碼組合轉(zhuǎn)換器電路。

- demultiplexer

具有寬度和輸出端口數(shù)量參數(shù)化的解復(fù)用器。

- full_adder

SystemVerilog 中的 n 位全加器

- full_subtractor

SystemVerilog 中的 n 位全減法器

- gray_counter

使用 SystemVerilog 中的二進(jìn)制計(jì)數(shù)器和二進(jìn)制到格雷碼組合轉(zhuǎn)換器電路實(shí)現(xiàn)的具有異步復(fù)位的 n 位格雷碼計(jì)數(shù)器。

- multiplexer

具有寬度和輸入端口數(shù)量參數(shù)化的多路復(fù)用器。

SvLibDR

包括串口和SPI接口的可綜合IP模塊

SystemVerilog-Bitmap-Library-AXI-Image-VIP

描述

要驗(yàn)證視頻或圖像處理 IP,可能需要將真實(shí)圖像讀取到設(shè)計(jì)中,并通過接口發(fā)送其數(shù)據(jù)。然后,從界面獲取輸出,并將其轉(zhuǎn)換為新圖像,保存或比較。

為了解決這個(gè)復(fù)雜的問題,設(shè)計(jì)了這個(gè)庫(kù),它可以幫助您簡(jiǎn)化設(shè)計(jì)流程。使用一些簡(jiǎn)單的 API 可以輕松地在測(cè)試臺(tái)中讀取和寫入標(biāo)準(zhǔn)位圖文件 (.BMP)。并且,使用 AXI-Stream Video Image VIP,可以輕松地將圖像發(fā)送到與 Xilinx 用戶指南 UG934 兼容的標(biāo)準(zhǔn) AXI-Stream 視頻接口,從輸出接口接收?qǐng)D像并保存。

位圖處理庫(kù)可以通過 System Verilog 將 Windows 位圖文件 (.BMP) 讀取和寫入位數(shù)組(虛擬內(nèi)存),以進(jìn)行 IP 驗(yàn)證。該庫(kù)支持 24 位和 32 位位圖讀入和 32 位位圖寫出。

使用位圖處理庫(kù)的 AXI-Stream Video Image VIP。“axi_stream_video_image_in_vip”IP 可以將位圖文件讀入內(nèi)存,并通過 AXI-Stream 視頻接口(在 Xilinx 用戶指南 UG934 中定義)發(fā)送。而“axi_stream_video_image_out_vip”IP可以監(jiān)控一個(gè)AXI-Stream接口,獲取在接口上傳輸?shù)膸⒈4娴轿粓D文件中。

一般信息

支持的位圖:

輸入:24-bpp/32-bpp RGB/RGBA 位圖輸出:32-bpp RGBA 位圖

這個(gè)庫(kù)的優(yōu)勢(shì)

- 簡(jiǎn)單的 API

- 開源

- 與流行的 EDA 工具兼容(在 Modelsim 和 Qustasim 上測(cè)試)

包中的文件

| 文件 | 描述 |

|---|---|

| bitmap_processing.sv | 位圖處理庫(kù)。 |

| axi_stream_video_image.sv | AXI 流視頻圖像庫(kù)(用于回調(diào)類)。 |

| axi_stream_video_image_in_vip.sv | VIP 用于讀取位圖并將其發(fā)送到接口。 |

| axi_stream_video_image_out_vip.sv | VIP 用于監(jiān)控界面并將圖像保存為位圖。 |

| axi_stream_video_image_example.sv | 如何使用 VIP 和庫(kù)的簡(jiǎn)單示例。 |

關(guān)于包使用等詳細(xì)信息,請(qǐng)查看項(xiàng)目介紹。

總結(jié)

今天只介紹了一個(gè)項(xiàng)目,這個(gè)項(xiàng)目可以給大家提供一個(gè)思路尤其對(duì)于沒有工作或者剛?cè)腴T不久的同行,自己在編寫代碼時(shí)要想著可繼承性,這樣在以后做類似項(xiàng)目時(shí)可以借用,并且長(zhǎng)期維護(hù)一個(gè)代碼對(duì)于這個(gè)模塊的理解有很大幫助。

最后,還是感謝各個(gè)大佬開源的項(xiàng)目,讓我們受益匪淺。后面有什么感興趣方面的項(xiàng)目,大家可以在后臺(tái)留言或者加微信留言,今天就到這,我是爆肝的碎碎思,期待下期文章與你相見。

審核編輯 :李倩

-

System

+關(guān)注

關(guān)注

0文章

165瀏覽量

36885 -

編輯器

+關(guān)注

關(guān)注

1文章

801瀏覽量

31120 -

模塊庫(kù)

+關(guān)注

關(guān)注

0文章

2瀏覽量

5072

原文標(biāo)題:優(yōu)秀的 Verilog/FPGA開源項(xiàng)目介紹(二十二)- SystemVerilog常用可綜合IP模塊庫(kù)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

IP地址歸屬地離線庫(kù)——網(wǎng)絡(luò)安全行業(yè)的基石

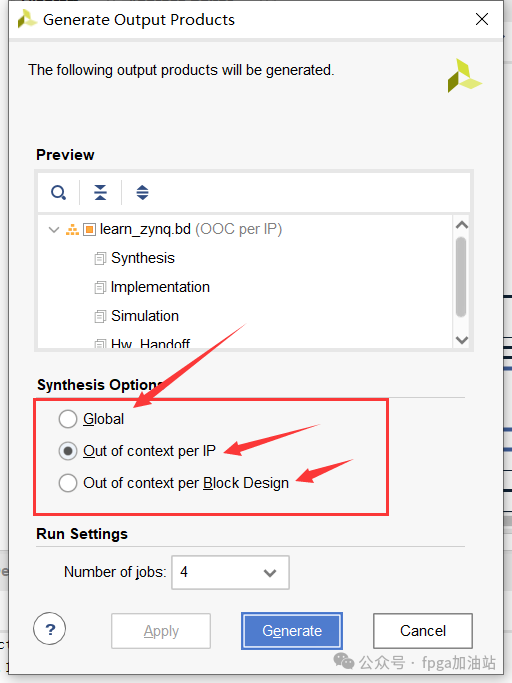

IP綜合時(shí)的幾個(gè)選項(xiàng)是什么含義

IP的綜合選項(xiàng)是什么意思

一種常用嵌入式開發(fā)代碼庫(kù)

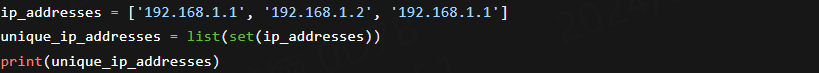

IP地址庫(kù):從收集到處理

Modbus轉(zhuǎn)Ethernet IP網(wǎng)關(guān)模塊與匯川PLC通訊案例

深度學(xué)習(xí)常用的Python庫(kù)

常用的電源模塊有哪些

新加坡裸機(jī)云多IP服務(wù)器網(wǎng)線路綜合測(cè)評(píng)

關(guān)于FPGA IP核

FPGA開源項(xiàng)目:Verilog常用可綜合IP模塊庫(kù)

在Vivado Synthesis中怎么使用SystemVerilog接口連接邏輯呢?

FPGA優(yōu)質(zhì)開源模塊-SRIO IP核的使用

SystemVerilog常用可綜合IP模塊庫(kù)

SystemVerilog常用可綜合IP模塊庫(kù)

評(píng)論