在我們之前關于模數轉換器 (ADC) 重要性的文章中,我們重點介紹了工業物聯網常用的各種架構。特別是,我們研究了哪種架構最適合低延遲、低功耗和高精度應用,每種選擇都有各種優點和缺點。當我們查看需要低延遲和低功耗的應用時,與閃存、delta-sigma 和流水線等其他架構相比,逐次逼近寄存器 (SAR) ADC 提供了最佳的整體解決方案。

對于越來越多需要更快采樣率以滿足機器對機器 (M2M) 連接不斷增長的需求的應用,ADC 的選擇略有不同。在最近的一篇文章中,我們討論了這些連接如何隨著物聯網的發展而急劇增加,而位于模擬前端 (AFE) 中的 ADC 是這些連接的核心。那么,對于需要快速采樣率的應用,需要考慮哪些權衡以及哪種架構優于其他架構?

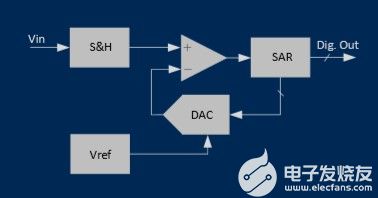

再次考慮 SAR ADC。在這種架構中,模擬輸入信號被采樣,然后通過一個工作在高于采樣率的頻率的比較器與連續的參考電壓進行比較。

圖 1:SAR ADC 框圖

在一個采樣周期內,比較器至少需要做出與轉換器分辨率一樣多的決定。更高的分辨率會降低最大采樣率,這取決于比較器做出決定的速度以及 SAR 邏輯的運行速度。在開關電容實現中,ADC 輸入網絡等效電路,如圖 2 所示,基本上包括一個采樣電容和一個采樣開關。

圖 2:SAR ADC 輸入網絡

采樣和保持 (S&H) 操作嵌入在 DAC 電路中,采樣電容器的大小可滿足噪聲要求。通過這種配置和正確的采樣電容大小,SAR ADC 可以轉換非常高頻的信號(數十 MHz),而不會導致高功耗。

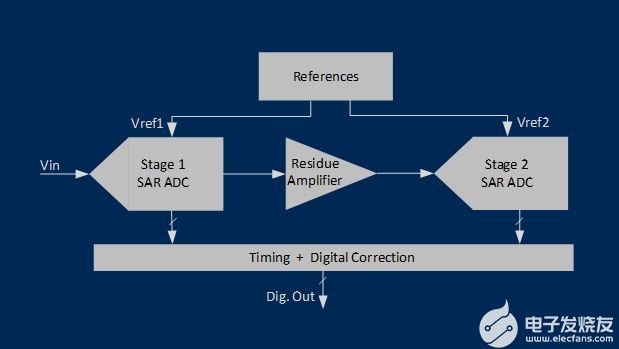

第二種需要考慮的架構是 SAR 輔助流水線 ADC,如圖 3 所示。該 ADC IP 可以通過兩個較低分辨率的 SAR ADC 級和一個剩余放大器來實現。第一階段解析數字輸出字的最高有效位。殘留物被第二階段放大和取樣。由于每個階段都使用較低的分辨率,因此可以實現每個階段的快速轉換時間。兩個階段同時工作;在第二階段轉換殘留放大信號時,第一階段已經在采樣并轉換下一個樣本。與單個 SAR 架構相比,這種流水線可以顯著提高最大采樣率。

圖 3:SAR 輔助流水線 ADC 框圖

Adesto 的所有 ADC IP 內核都提供的另一個考慮因素是參考電壓生成。在 ADC 內核附近生成參考電壓很重要,因為它可以防止性能下降。優化和高效的參考電壓生成和緩沖對于穩健、節能和高精度的轉換器至關重要。

Adesto擁有經過硅驗證的大型 SAR 和流水線輔助 SAR ADC IP 塊產品組合,可用于許可,包含滿足應用程序的采樣率、功率和延遲要求所需的所有元素。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8625瀏覽量

146862 -

SAR

+關注

關注

3文章

412瀏覽量

45894 -

adc

+關注

關注

98文章

6430瀏覽量

544079

發布評論請先 登錄

相關推薦

用于高采樣率應用的SAR ADC

用于高采樣率應用的SAR ADC

評論