文/蔣修國

編者注:在5G和高速數據傳輸的當前,設計和生產中往往會隱藏著很多問題小魔鬼,只有知其然,才能更好地找到解決之道。

不管是高速電路、高頻電路還是毫米波,只要是電子產品基本都需要使用到PCB。PCB板的加工是一個非常復雜的系統工程,涉及到各個方面的問題,比如PCB材料、藥水、加工工藝等等。在這個過程中會有很多因素對傳輸線的阻抗造成影響,比如PCB材料所涉及的銅箔厚度、介質厚度、介電常數、介質損耗角的影響,加工中涉及到的蝕刻因子(Etch),蝕刻藥水的特性、加工穩定性等等。本文將從仿真的角度分析其中幾個影響因子對阻抗的影響,當我們分析阻抗問題的時候可以多個思路。

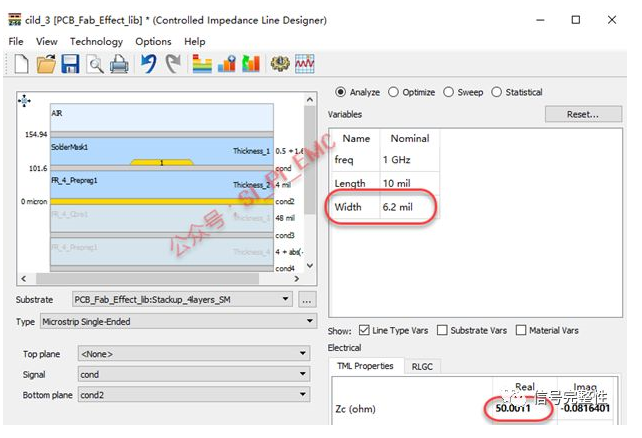

1、傳輸線的線寬

在以前的文章中介紹了很多關于線寬影響信號完整性的內容,我們知道線寬會直接影響到傳輸線的阻抗和損耗。大多數優秀工程師都會在給PCB生產商出Gerber時規定好線寬調整的范圍,比如當線寬設計為6.2時,其阻抗為50ohm:

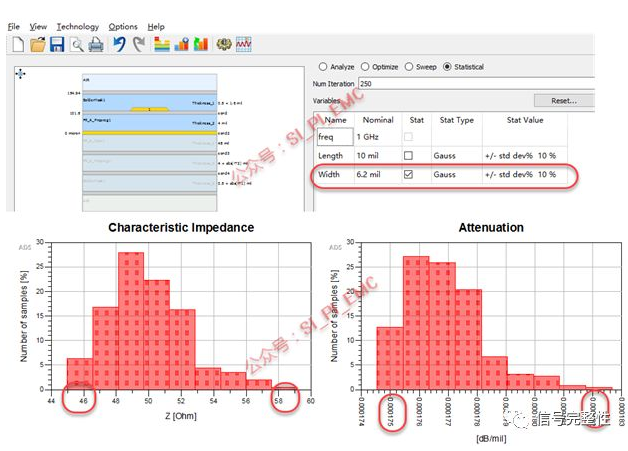

如果PCB在生產過程中工藝不穩定,導致線寬變化。依據與很多數廠商合作過的經驗看來,傳輸線線寬的變化會在10%左右,所以把線寬變化的類型設置為Gauss分布,std設置為10%,進行統計學分析,在ADS CILD中仿真分析結果如下:

從結果上分析,阻抗最低會達到46ohm,而最高達到了58ohm;如果是在一段很長的傳輸線上,出現極端的狀態是會存在的,那這時就會導致回波損耗比較大,同樣插入損耗也有所增加。

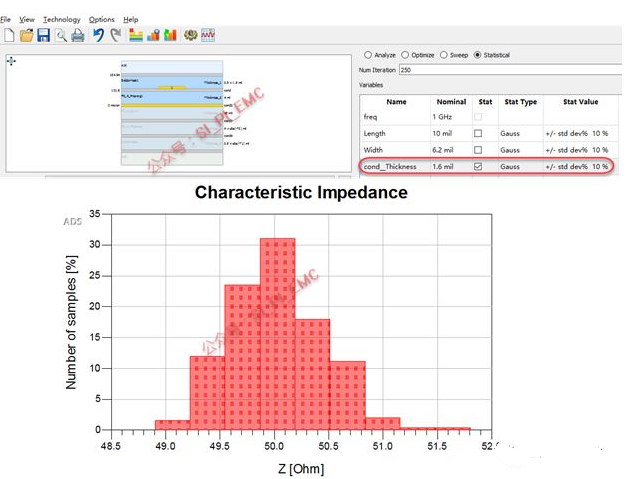

2、銅箔/鍍銅厚度

在PCB產品中,銅厚分為基銅厚度和鍍銅厚度,基銅一般會比較均勻(這是相對的,其實也并不是完全均勻的),而鍍銅的均勻性會隨著工廠穩定性不同而不同,有的相差還比較大。鍍銅厚度不同,同樣會導致傳輸線阻抗和損耗的變化。把鍍銅的變化范圍假定為10%,在ADS CILD中進行統計分析,結果如下:

從結果分析來看,阻抗主要在49.5到51ohm之間變化。相對于線寬而言,變化區間會小不少。

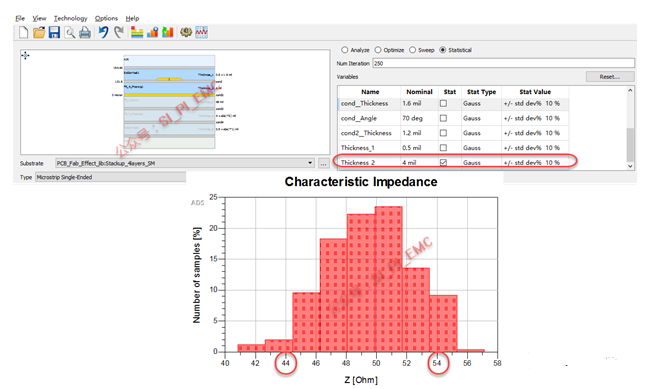

3、介質的厚度

在PCB生產中,介質厚度變化的主要來源是原材料和生產過程中的壓合以及填膠。如果介質厚度變化,會造成阻抗的變化,以及損耗的變化,嚴重的情況會導致傳輸線很大的損耗。

從結果上分析,阻抗變化分布在44ohm到54ohm之間。阻抗變化的范圍達到了10ohm之多。

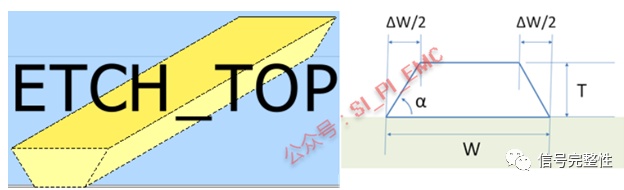

4、蝕刻因子

由于導體都是有一定厚度的,所以在生產中導致蝕刻出來的導線并不是一個標準的“矩形”結構,而是一個接近于“梯形”的結構(其實真實的狀況也并不是完全的梯形結構),如下圖所示為導體的一個示意圖:

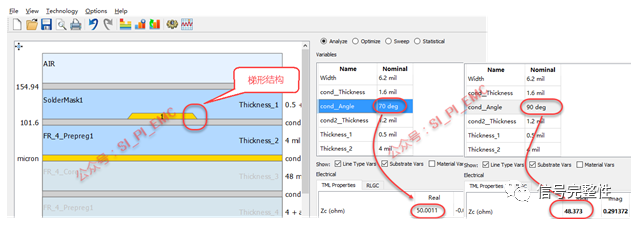

這個梯形的角度會隨著銅厚的變化而變化(鍍銅亦是如此),厚度越薄,角度越接近90°。這個角度的大小會影響到阻抗的大小。如下圖所示為90°與70°結果的對比:

當角度為70°時,阻抗約為50ohm;當角度為90°時,阻抗約為48.37ohm。

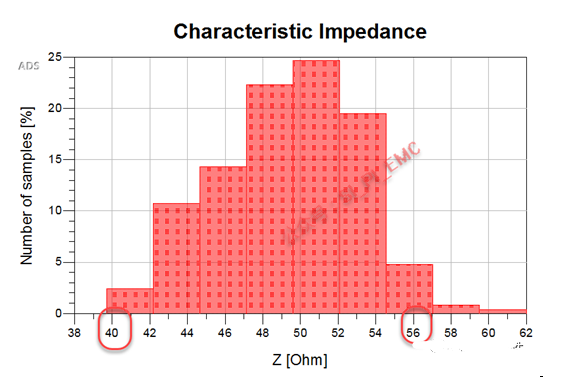

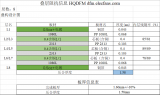

以上都是在單個因素變化下做的實驗,而在生產過程中,并不是單一變量的變化,可能會同時發生。如果同時發生,那么其統計結果如下圖所示:

從結果中可以看到阻抗主要在40ohm到56ohm之間變化,這個已經遠遠超過了一般50±10%的要求。而在整個生產過程中還不止這些參數的變化會導致阻抗的變化。所以對于高速高頻電路的產品,或者是高端產品,整個PCB設計和生產過程中都要嚴格控制好每一種物料以及每一個環節,否則就會導致產品出現一些意想不到的問題。

-

pcb

+關注

關注

4317文章

23014瀏覽量

396380 -

信號完整性

+關注

關注

68文章

1398瀏覽量

95388 -

5G

+關注

關注

1353文章

48375瀏覽量

563426

發布評論請先 登錄

相關推薦

淺談PCB疊層設計原則及阻抗設計

PCB線路板為什么要做阻抗?

PCB加工如何做好阻抗控制?

PCB板加工中影響信號完整性的關鍵因素

淺談PCB板加工中影響因子對阻抗的影響

淺談PCB板加工中影響因子對阻抗的影響

評論