雙向端口簡介

三態緩沖器也稱三態門,其典型應用是雙向端口,常用于雙向數據總線的構建。在數字電路中,邏輯輸出有兩個正常態:低電平狀態(邏輯0)和高電平狀態(邏輯1),此外,電路還有不屬于0和1的高阻態(邏輯Z)。所謂高阻,即輸出端屬于浮空狀態,只有很小的漏電流流動,其電平隨外部電平的高低而定,門電平放棄對輸出電路的控制。或者可以理解為輸出和電路是斷開的。

在應用代碼中,verilog HDL程序模塊首先進行端口(input:輸入端口;output:輸出端口;inout:輸入/輸出端口)定義,然后是邏輯功能的描述。在verilog HDL中,output端口信號可以被定義為reg類型,并在always塊中賦值使用,而inout端口不能被定義為reg類型,不能再always塊中直接賦值使用,這一點與VHDL中的雙向端口使用方法不同。

由于FPGA需要與外部存儲器或CPU進行頻繁的數據交換,以及引腳資源有限,使用雙向端口設計可以成倍的節省數據引腳線。在設計中需要注意兩點:其一,要用三態門的控制來處理實現雙向端口;其二,要分別指定雙向端口作為輸入、輸出端口時,對外部對象的數據操作。

2. 雙向端口應用實例

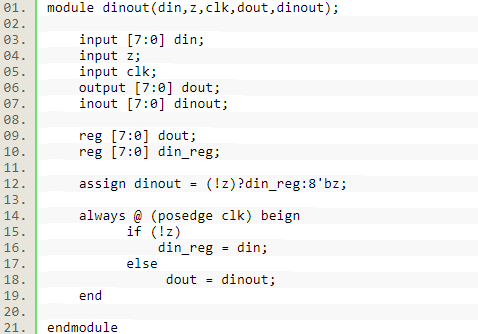

1. 雙向端口的verilog HDL描述

如果輸入輸出端口都是16位,那么總共需要32根數據線,使用雙向端口,只需要16根數據線。實例:

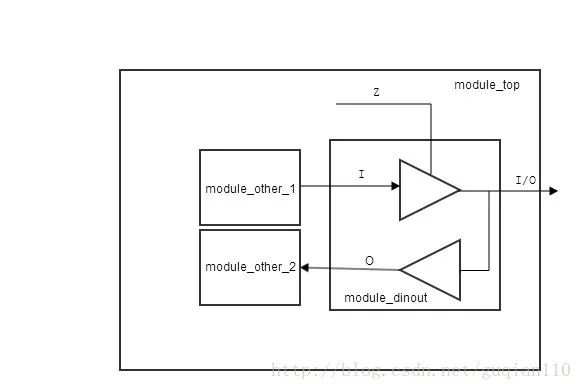

模塊示意圖:

dinout為雙向端口,即可作為輸入端口,又可作為輸出端口;

當 z = 0 時,三態門選通,從模塊module_other_1 輸出的數據 data 的流動方向為 I ---> I/O ,I/O 作為系統(module_top)的輸出端口;(對于模塊module_dinout,I 的類型是input,I/O的類型聲明為inout,此時作為輸出端口)

當 z = 1 時,三態門關閉,數據 data 的流動方向為 O <--- I/O ,data輸入到模塊module_other_2 中,供其使用,I/O 作為系統(module_top)的輸入端口;(對于模塊module_dinout,O 的類型是output,I/O的類型聲明為inout,此時作為輸入端口)

2. 雙向端口的仿真

編寫測試模塊時,對于inout類型的端口,需要定義成wire類型,而其他輸入端口定義為reg類型。此外,對于雙向端口本身,仿真輸出端口和輸入端口的語法是不同的。

輸出端口仿真

當作為輸出端口時,不需要對其進行初始化,只要開通三態門即可。

輸入端口仿真

當作為輸入端口時,需要對其進行初始化賦值并關閉三態門。而如果直接把它跟一般的輸入口一樣直接初始化賦值,則會出錯,因為它的定義是wire類型而不是reg類型。這里需要用到force命令。

審核編輯 :李倩

-

存儲器

+關注

關注

38文章

7452瀏覽量

163606 -

端口

+關注

關注

4文章

955瀏覽量

32014

原文標題:2. 雙向端口應用實例

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

內部端口和外部端口怎么填

外部端口和內部端口是什么意思

控制端口和數據端口怎么區別

雙向可控硅觸發電路的工作原理、設計方法和應用實例

TS5USBC41雙向低功耗雙端口高速USB 2.0模擬開關數據表

雙向端口應用實例

雙向端口應用實例

評論