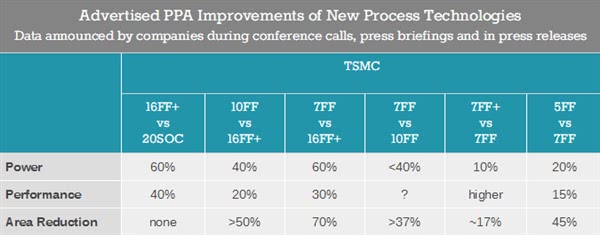

領先的芯片制造商臺積電和三星正在大批量生產 5nm 器件,而臺積電正在推進到年底推出首款 3nm 芯片的計劃。但要實現如此激進的目標,工程師必須比以前更快地識別缺陷并提高良率。

處理 EUV 隨機缺陷——非重復圖案缺陷,如微橋、斷線或缺失觸點——是這一挑戰的核心。這需要強大的高通量檢測策略來檢測和修復常見問題,例如缺少通孔。

良率工程師會定期識別芯片上需要針對性檢查的關鍵區域。KLA營銷副總裁 Satya Kurada 說:“檢測配方在確定檢測到哪些缺陷以及檢測到多少缺陷方面發揮著關鍵作用。 ” “20 年前,運營商會為邏輯芯片設置兩個護理區域——一個用于隨機模式,一個用于 SRAM 區域。今天,我們的檢測系統使用專利技術,根據用戶定義的興趣模式自動生成數十億個非常微小的護理區域。”

投入 EUV 光刻

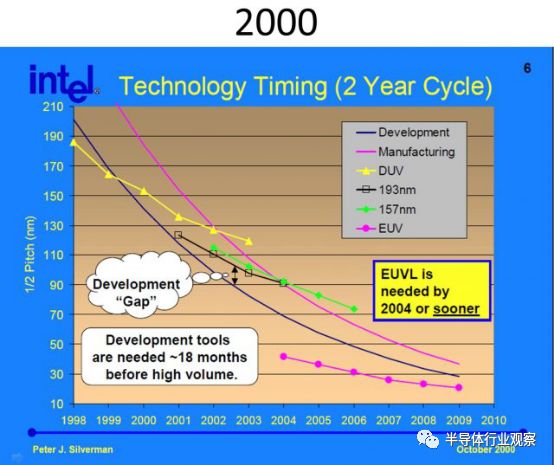

晶圓廠最重要的產量和成本驅動因素之一是極紫外(EUV,13.5nm)掩模層的凈數量。EUV光刻是在 7nm 晶圓廠生產線中引入最關鍵的層,但在 5nm 節點,可能有 75% 的總層(邏輯器件中超過 50 個)需要 EUV 圖案化。使用 193nm 曝光或 EUV 最常見的隨機缺陷是隨機打印失敗。

“微橋與來自光刻膠或工藝工具的傳統缺陷沒有明顯區別。因此,正在同時努力消除傳統缺陷,通過設計新的光刻膠或改進干法蝕刻工藝來減少這些缺陷,”三星電子副總裁 Ki Chul Park 表示,他在 IITC [1 ]。“總成本的最大貢獻者是用于細間距金屬和通孔層圖案化的 EUV 層數。添加 EUV 層后,總成本大約會增加 1% 到 2% [2],這意味著添加 EUV 層必須導致面積減少 1% 到 2% 以上。” Park 指出,領先的 EUV 光刻膠能夠單次曝光印刷 30nm 金屬節距線,具有可制造的缺陷。

幾十年來一直主導該行業的化學放大抗蝕劑 (CAR) 現在正受到新型金屬氧化物抗蝕劑 (MOR) 的挑戰。由 JSR 公司 Inpria 首創的 MOR 的優勢在于它們更好地吸收 EUV,因此它們可以比 CAR 更薄,并且不太可能遭受圖案崩潰的影響。其他選項也在出現,包括非 CAR 旋涂抗蝕劑,以及 Lam Research 的干法抗蝕劑沉積和去除工藝。有趣的是,EUV 掃描儀產生的光子量約為1/14由 ArF (193nm) 掃描儀生產的產品,再加上更精細的功能,解釋了 Imec、ASML 和光刻膠制造商 JSR、信越化學和富士膠片之間的密集研發,以及 TEL 的光刻膠涂層/烘烤/顯影工藝流程擴展 EUV 圖案化能力。

解決隨機變化

隨機缺陷是任何隨機的、孤立的缺陷,它們會導致諸如微橋接、局部斷線以及觸點丟失或合并等問題。線邊緣保真度的損失稱為線寬粗糙度(LWR)和線邊緣粗糙度(LER)。在光刻中,臨界尺寸 (CD) 不均勻性可以是局部的(一條線到另一條線)或全局的(跨晶圓),并且可能由標線錯誤、掃描儀錯誤或蝕刻和沉積錯誤引起。重疊誤差是特征之間的對齊錯誤。如果邊緣放置錯誤(EPE) 足夠關閉,則金屬之間可能會發生短路,或者微小的通孔可能會完全消失,從而導致電氣開路。

D2S首席執行官 Aki Fujimura 表示:“芯片制造商必須區分隨機指標和系統缺陷,即它們在一定程度上可以平等地擴展,這意味著特定設計中存在某種使其易受攻擊的東西。 ” 他補充說,處于領先地位的芯片制造商必須解決系統變化的來源,并將隨機(隨機)缺陷控制在被認為可以接受大批量生產的水平。

隨機圖案缺陷是一個大問題。“這是一個價值數十億美元的問題,因為隨機因素在晶圓廠邊緣放置錯誤預算中所占的比例要大得多,”Fractilia 首席執行官 Ed Charrier 解釋說。“隨機指標一直存在,但它們只占特征大小的一小部分,所以我們一直能夠忽略它們,直到最近的節點,”Fractilia 的首席技術官 Chris Mack 說。在 22 納米節點,隨機缺陷占邊緣放置誤差 (EPE) 預算的 5%,但在 5 納米節點,它占 EPE 總預算的 40%,在 3 納米節點攀升至 50%,以此類推。更糟糕的是,在抗蝕劑中反應的光子數量非常少——稱為 EUV 散粒噪聲(類似于霰彈槍彈丸擴散)——4 到 5 個光子,會增加線邊緣粗糙度。

“你有 4 個還是 5 個有很大的不同,”D2S 的 Fujimura 說。新的 EUV 工藝,包括先進的光刻膠,專注于提高 CAR 光刻膠的量子效率,以加快 EUV 吞吐量,同時最大限度地減少隨機性。在 CAR 中,每個進入的光子會去保護多個抗蝕劑分子(化學放大)。增加量子效率意味著更大比例的可用光子導致光酸產生事件,或者每個光酸分子去保護更多的抗蝕劑分子,或兩者兼而有之。光子引起的變化和稀有的 EUV 光子轉化為成像事件會導致 EUV 中更高的隨機后果。

量化變化

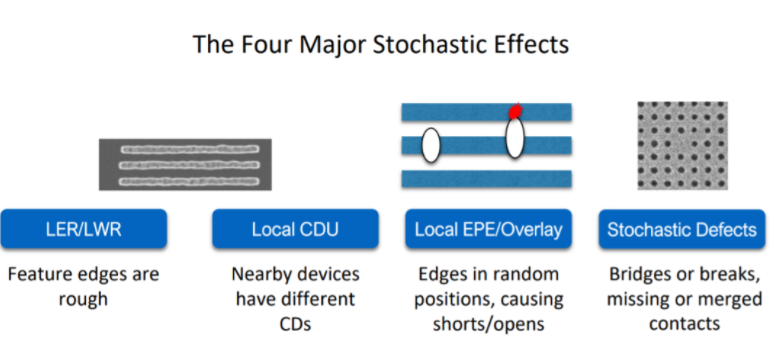

隨機缺陷分為四類(如圖1所示):線邊緣和線寬粗糙度;特征之間的 CD 不均勻性;疊加錯誤;并具有靠得太近(導致短路)或太遠(導致開路)的邊緣。

“所有這些因素都會影響設備性能、良率和可靠性,”Fractilia 的 Mack 說。在光刻單元中,光學檢測工具與速度慢得多的掃描電子顯微鏡 (SEM) 相輔相成,后者可測量 CD 或提供在線缺陷審查和分類。CD-SEM 成像結果包含印刷線和空間的實際粗糙度,但也包含 SEM 噪聲造成的粗糙度。Mack 解釋說,傳統的圖像處理過濾器將平均粗糙度而不顯示實際粗糙度。“我們開發了在頻域而不是空間域中運行的工具,我們使用功率譜密度來查看長尺度和短尺度尺度的粗糙度,”他解釋道。“我們可能會在晶圓上發生的實際變化之上測量 4.3 納米的計量噪聲,但通過減去計量噪聲的處理,我們可能只會得到 1.3 納米的粗糙度,”他說。然后,該工具對圖案進行反向建模,以查看晶圓上的實際圖像是什么。向前然后向后的模型允許在單個分析中捕獲所有隨機缺陷。它還為工程師提供了一種優化 SEM 使用的方法,即使使用來自不同供應商的工具,也能實現工具對工具的匹配。

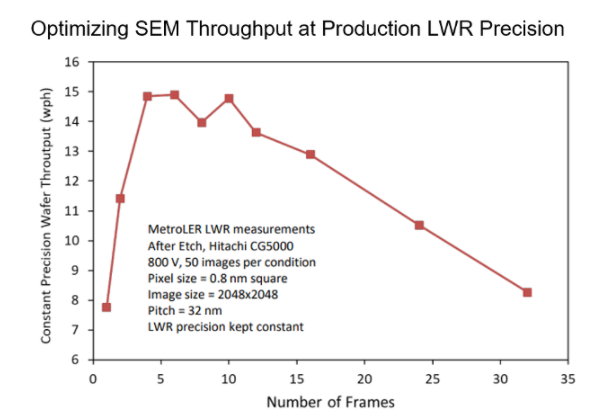

Fractilia 的工具還加快了 SEM 的吞吐量。與電視圖像一樣,SEM 使用光柵掃描平均數幀(4 到 32)來生成最終圖像,因此更高的圖像分辨率包含更多幀但會延長測量時間。Fractilia 的工具允許在給定的測量精度(見圖 3)下優化幀速率以獲得更高的 SEM 吞吐量,工程師為給定的工藝層選擇該精度。由于晶圓廠通常在生產車間擁有多個 SEM(由 KLA、應用材料、日立等制造),因此該軟件工具還改進了 SEM 到 SEM 的匹配,以改進過程控制。

Imec 使用 Fractilia 的工具進行的一項研究表明,40nm 觸點上的隨機缺陷與線寬粗糙度之間存在相關性 [3]。換句話說,LWR 充當制造中隨機缺陷的代表。Mack 補充說,粗糙度測量不僅在制造中至關重要,而且在評估新光刻膠的研發環境中也很重要。“可能有 20 種材料可供選擇,公司正在運行大量晶圓并測量 CD,以查看哪種材料產生更好的焦深和提供更好的粗糙度。通常,粗糙度的差異可能為 10%,但不同的材料可能具有影響粗糙度 10% 或 20% 的特性。是抗蝕劑之間的差異還是由于 SEM?這是一個大問題,”他說。“相反,我們可以去除 SEM 噪音并比較材料。”

圖 1:隨機指標包括與線邊緣/線寬粗糙度、CD 不均勻性、重疊(對齊)錯誤和特征缺陷相關的缺陷。資料來源:Fractilia

圖 2:對于這些數據,MetroLER 軟件提供了最佳的 SEM 捕獲率,可在 10 幀左右平衡精度、準確度和吞吐量。資料來源:Fractilia

捕獲丟失的過孔

在先進的邏輯芯片上,過孔數達到數百萬甚至數十億,準確捕獲丟失的過孔或觸點對良率工程師來說是一項重大挑戰。近年來,光學檢測工具的供應商大幅更新了他們的工具和軟件,以檢測越來越多的越來越小的缺陷,并使用更智能的(支持人工智能的)軟件更快地表征它們。檢查工具“recipe”(給定工藝層的設置)包括以下選項:

光學設置(焦點偏移、放大倍率等);

指定護理區域(將檢查哪些模具區域),以及

KLA 的 Kurada 表示,該公司的寬帶等離子 (BBP) 光學圖案化晶圓檢測儀的另一個參數是可調波段(深紫外到紅外),它可以提高不同薄膜(光刻膠、金屬、低- k 電介質等)

但是工程師如何確定給定設備的護理區域?事實證明,通常使用兩種方法。第一個使用基于歷史的已知缺陷或麻煩位置。第二個方法使用已知的薄弱點或設計中具有風險特征的區域(例如密集的細線)從 IC 設計文件(例如 GDSII)中識別位置。然后,該軟件會獲取所有感興趣的模式并自動生成護理區域。

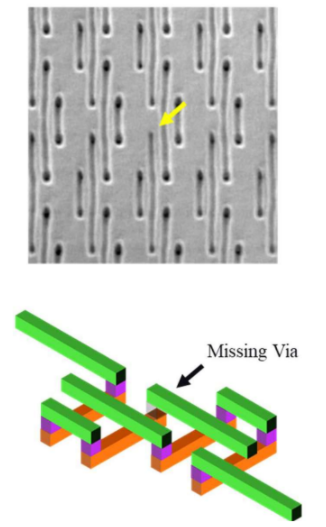

例如,KLA 和 IBM Research 的工程師最近開發了一種基于重復陣列的分箱技術,該技術通過缺陷檢測數據將缺失與晶圓位置相關聯。[4] 工程師發現了以前的工具未捕獲的先前缺失的通孔,他們將問題追溯到晶圓上的特定區域,這表明反應離子蝕刻 (RIE) 步驟存在問題。

圖 3:互連線之間的過孔缺失是蝕刻后檢測監控的關鍵缺陷。資料來源:KLA、IBM、IEEE ASMC

在這項研究中,IBM 和 KLA 工程師開發了一種可靠的過程控制方法,用于在線捕獲 BEOL 邏輯器件中缺失的過孔。[4] 工程師使用 KLA 的檢測方法在 RIE 的通孔鏈圖案上定義設計中的關注區域(每個通孔周圍),以提高對丟失通孔缺陷的捕獲靈敏度。使用寬帶等離子 (BBP) 光學檢查工具檢查護理區域,然后在 SEM 審查工具上對缺陷進行表征,該工具按類型對缺陷進行分類(在這種情況下是缺失通孔??與有害缺陷)。測試結構基于檢測靈敏度最高的最小重復模式。

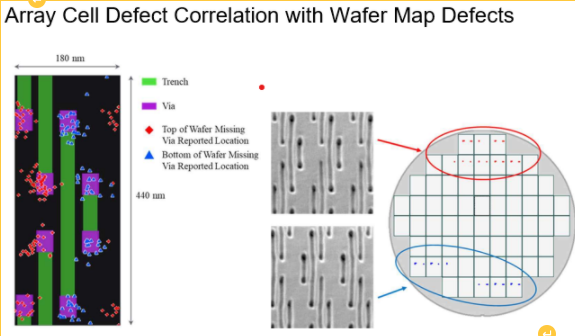

圖 4:通孔鏈圖案左側的單元級缺陷顯示為晶圓頂部的缺陷,而右側缺失的通孔則識別出以前檢查遺漏的全新缺陷。識別的圖案成為蝕刻后在線監測的基礎。資料來源:KLA、IBM、ASMC

結果顯示了單元級特征(參見圖 4,重復單元疊加),其中通路鏈左側的缺失通路僅出現在晶圓頂部,而右側缺失的通路與晶圓底部相關。該團隊懷疑缺失的通孔缺陷是由于先前的通孔蝕刻由于圖案未對準而被阻塞造成的。之前的檢測方法沒有檢測到晶圓底部的缺陷,這意味著該策略可用于選擇具有代表性的采樣率,以便更有效地在線監測生產中缺失過孔的缺陷。“來自 BPP 系統的檢查結果,包括分箱信息,為工藝工程師提供了可操作的數據,以便他們能夠做出明智的決策,”Kurada 說。

缺陷審查替代方案

良率上升和良率偏差幾乎總是使用光學檢測系統和 SEM 審查來控制,但在某些情況下,其他技術可以更好地滿足要求。布魯克運營總監 Igor Schmidt 表示:“20nm 量級的隨機缺陷變得越來越難以分類,而 AFM 尤其有用的地方是在需要拓撲數據時,例如檢測 CMP 后的凹陷和腐蝕數據。 ” 他指出,雖然原子力顯微鏡(AFM) 往往以低吞吐量著稱,但它們每小時可以監控 340 個位置,以進行光刻、蝕刻或 CMP 工藝的工藝控制。

原子力顯微鏡 (AFM) 審查工具可以從光學系統獲取晶圓圖數據,驅動到感興趣的缺陷(使用機器視覺的 x、y、z 和旋轉位置)并掃描 30 x 30 μm 的區域以對缺陷進行成像。缺陷圖像顯示具有最大高度 (z) 信息和粘性的 3D 尺寸。“這就像你踩在口香糖上而不是踩在石頭上一樣。在這種情況下,如果我們的缺陷具有較大的形貌和較大的附著力,則可能表明有機顆粒或聚合物掉落在晶圓上。另一方面,如果您的地形較大且附著力較弱或沒有附著力,則這更有可能是顆粒,可能是硅顆粒或碎片。如果您有孔且沒有粘附,則可能是堆疊默認或結晶缺陷,或者如果您沒有顆粒但粘附,這可能表明某處機器有油和問題。因此,這是一種對缺陷進行分類的強大技術,”他說。

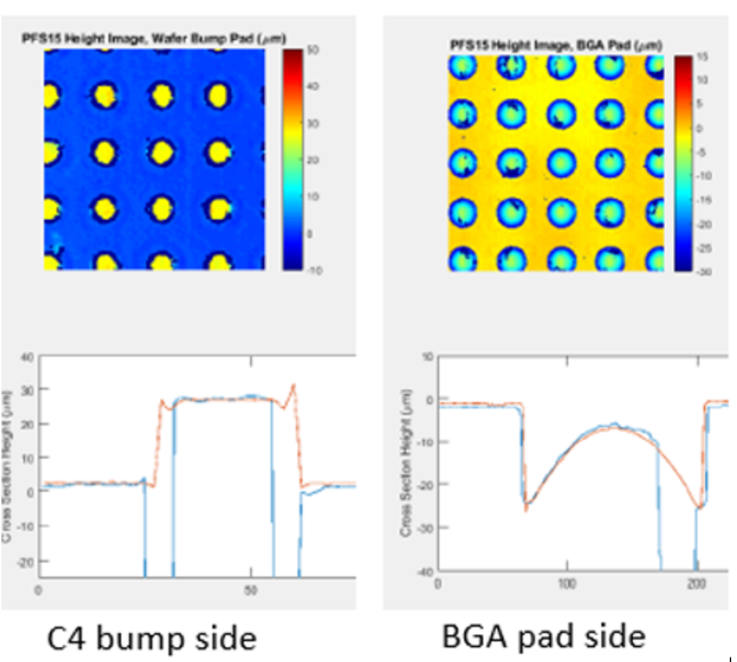

封裝、智能、良率

對于進行異構集成的 IC 公司而言,最昂貴的良率之一是凸塊良率。與連接 IC 上的銅線的密集通孔類似,金屬凸點互連越來越密集。同時,先進的封裝技術支持各種 3D 方案,芯片制造商正在開發這些方案。

“現在有這么多的堆疊,這帶來了很多好處,但與此同時,顛簸的數量已經爆炸式增長。Cyber??Optics 總裁兼首席執行官Subodh Kulkarni 表示,當我們與晶圓廠交談時,他們的頭號痛點是提供 100% 的凹凸檢測成本效益。

Kulkarni 指出,由于有數百萬個凸塊和自動光學檢測吞吐量,每小時 10 到 15 個晶圓(300 毫米)的速度是不夠的。“最佳點是每小時交付 25 到 30 個晶圓,在價格低于 100 萬美元的工具上具有 1 億個凸點能力。因為這是他們今天損失大量產量的地方,”他說。

銅凸塊的光學檢測包括測量共面性、檢測異常值(高于最高規格或短于最短規格)、凸塊位置和尺寸,以及凸塊上的缺陷。“對于異常值,客戶希望我們存儲該凹凸圖像,但還要確定是否存在裂縫,或者我們是否看到一些污染或凹凸的一部分已被切掉。” 所有這些信息都很重要。

圖 5:MRS 光學檢測圖像顯示了銅凸點和焊盤上的形狀、尺寸和潛在缺陷,以及高度輪廓。資料來源:賽博光學

結論

先進 5nm 器件或先進封裝的良率提升需要識別和去除從光刻到封裝材料的關鍵缺陷,因此智能和快速的晶圓級檢測必不可少。

從 22nm 到 5nm,隨機缺陷成為一個越來越大的問題,并且會顯著影響器件的良率和可靠性。工程師正在使用新工具來識別和消除隨機缺陷,同時實現更準確的 SEM 審查、工具匹配和提高晶圓廠的 SEM 吞吐量。將設計感知軟件與光學和電子束審查工具相結合,可以提高對難以成像的良率殺手(如缺少通孔)的捕獲。銅凸點的高吞吐量、100% 晶圓檢測是先進封裝實現高良率的關鍵。

參考

[1] KC Park 和 H. Simka,“超越 5nm 的高級互連挑戰和可能的解決方案”,IEEE 國際互連技術會議 (IITC),2021 年。

[2] BS Kasprowicz 等人,EUVL 研討會,2017 年。

[3 ] D. De Simone,“Imec 的 EUV 材料狀態”,Imec PTW,2019 年 4 月

。 [4] G. Jensen 等人,“使用新穎的高精度陣列分割檢測技術增強缺失通孔缺陷捕獲技術, ” IEEE 先進半導體制造會議 (ASMC),2021 年。

-

光刻

+關注

關注

8文章

318瀏覽量

30120 -

EUV

+關注

關注

8文章

604瀏覽量

85971

發布評論請先 登錄

相關推薦

臺積電早期5nm測試芯片良率80%,HVM將于2020上半年推出

消息稱三星5nm等部分工藝良率低于50%,三星沒否認

EUV光刻機何以造出5nm芯片?

全球進入5nm時代

EUV極紫外真難!臺積電首次揭秘5nm:頻率僅提升15%

5nm芯片為何集體翻車?

中科院5nm光刻技術與ASML光刻機有何區別?

EUV光刻機何以造出5nm芯片

各種光刻技術你都了解嗎?

如何加快5nm芯片良率 ,EUV光刻或是關鍵要素

如何加快5nm芯片良率 ,EUV光刻或是關鍵要素

評論