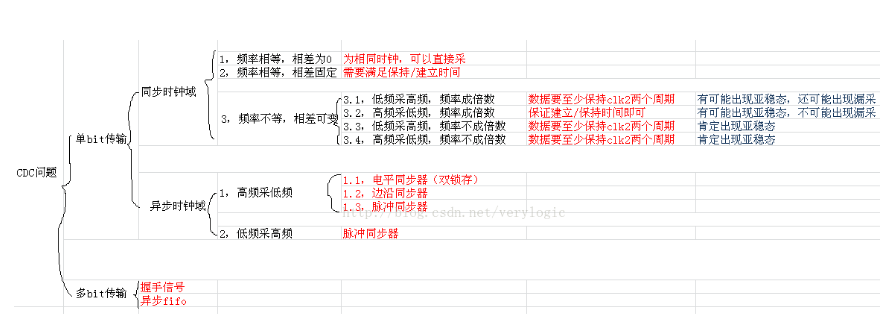

CDC(不同時鐘之間傳數據)問題是ASIC/FPGA設計中最頭疼的問題。CDC本身又分為同步時鐘域和異步時鐘域。這里要注意,同步時鐘域是指時鐘頻率和相位具有一定關系的時鐘域,并非一定只有頻率和相位相同的時鐘才是同步時鐘域。異步時鐘域的兩個時鐘則沒有任何關系。這里假設數據由clk1傳向clk2。

單bit傳輸時,同步時鐘域因為頻率和相位關系都是已知的,可以推導的,所以不需要采用額外的硬件電路就可以解決CDC問題,只需要源數據在clk1端保持足夠長時間即可。讓其保持足夠長時間有兩個好處:即便出現亞穩態,也可以在兩個clk2時鐘周期后數據變得穩定下來,從而采到正確的結果。還可以防止低頻采高頻時,因為頻率跟不上而導致數據丟失。

單bit傳輸時,異步時鐘域的傳輸就必須使用額外的電路模塊(同步器)來保證數據正確的傳輸。最基本的同步器是雙鎖存結構的電平同步器,其余的同步器都是由其衍生而來。該同步器的基本原理,也是讓數據至少在clk2的時鐘下保存兩個周期,消除亞穩態。當然同步器能解決異步時鐘域的同步問題,自然也可以拿來解決同步時鐘域的問題,畢竟同步時鐘域更簡單一些。

實際的電路設計中,才不會管那么多細節,不管你是同步時鐘域還是異步時鐘域,只要是不同的時鐘之間傳數據,就加上同步器的結構,這當然是一種偷懶的解決辦法。脈沖同步器就是這么一種萬能的結構,對于單bit跨時鐘域傳輸而言,使用脈沖同步器就夠了,不需要區分時鐘有沒有關系,也不需要區分是高頻采低頻還是低頻采高頻,畢竟也很少有人能掌握這么全的細節。

對于多bit傳輸,不能采用單bit傳輸的方法。原因在于,單bit傳輸時,不能確定該數據到底經過1個clk2時鐘周期之后有效還是兩個clk2時鐘周期之后才有效。所以對多個bit各自采用單bit的同步機制,會導致輸出一些錯誤的中間狀態。對于多bit傳輸,只能使用握手信號或者異步fifo。

總結如下:

1、有關系的時鐘之間傳單bit數據,理論上只需要源數據保持足夠長的時間(clk2的兩個周期)即可;

2、無關系的時鐘之間傳單bit數據,必須要使用同步器;

3、不管有無關系的時鐘進行單bit傳輸,脈沖同步器都可以解決這個問題;

4、多bit傳輸只能使用握手機制或者異步fifo;

5、低頻采高頻,為防止數據不丟失,應當讓源數據變慢,多保持一些周期;高頻采低頻則不需要,但是高頻采低頻得到的結果可能帶有很多冗余。

原文標題:FPGA學習-CDC問題的解決方案總結--異步時鐘

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601807 -

asic

+關注

關注

34文章

1193瀏覽量

120320 -

異步時鐘

+關注

關注

0文章

17瀏覽量

9402 -

同步時鐘

+關注

關注

0文章

44瀏覽量

3216

原文標題:FPGA學習-CDC問題的解決方案總結--異步時鐘

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ASIC和FPGA的優勢與劣勢

cogoask講解fpga和ASIC是什么意思

如何在FPGA和ASIC設計中結合高速USB功能

ASIC設計-FPGA原型驗證

FPGA和ASIC芯片解密有哪些性能分析

高密度IC設計中ASIC與FPGA選擇誰

ASIC和FPGA有什么區別

ASIC和FPGA設計中的多點綜合技術

ASIC設計轉FPGA時的注意事項

如何使用report_cdc命令分析、調試和修復CDC問題

FPGA_ASIC-MAC在FPGA中的高效實現

ASIC/FPGA設計中的CDC問題分析

ASIC/FPGA設計中的CDC問題分析

評論