1 Synopsys 系列工具包含

1)Library Compiler

2)Design Compiler和Design Vision

3)Physical Compiler

4)PrimeTime

5)DFT Compiler

6)Formality

2 Library Compiler

任何ASIC設(shè)計的核心都包含一組邏輯單元的工藝庫,庫可以包含每個單元的功能描述、時序、面積及其他相關(guān)信息。在轉(zhuǎn)換為可被Synopsys應(yīng)用程序使用的格式前,Library Compiler(LC)會分析文本信息的完整性與正確性。

可以在命令行輸入lc_shell啟動,LC的功能在dc_shell中也可以使用。

$ lc_shell

Library Compiler (TM)

DesignWare Developer (TM)

Version D-2010.03 for linux -- Feb 22, 2010

Copyright (c) 1988-2009 by Synopsys, Inc.

ALL RIGHTS RESERVED

This software and the associated documentation are confidential and

proprietary to Synopsys, Inc. Your use or disclosure of this software

is subject to the terms and conditions of a written license agreement

between you, or your company, and Synopsys, Inc.

The above trademark notice does not imply that you are licensed to use

all of the listed products. You are licensed to use only those products

for which you have lawfully obtained a valid license key.

Initializing...

Settings:

search_path: . /Tools/dc/libraries/syn /Tools/dc/dw/syn_ver /Tools/dc/dw/sim_ver ../ref/db ./scripts ./rtl ./mapped ./unmapped

link_library: * sc_max.db

target_library: sc_max.db

symbol_library: sc.sdb

I am ready ...

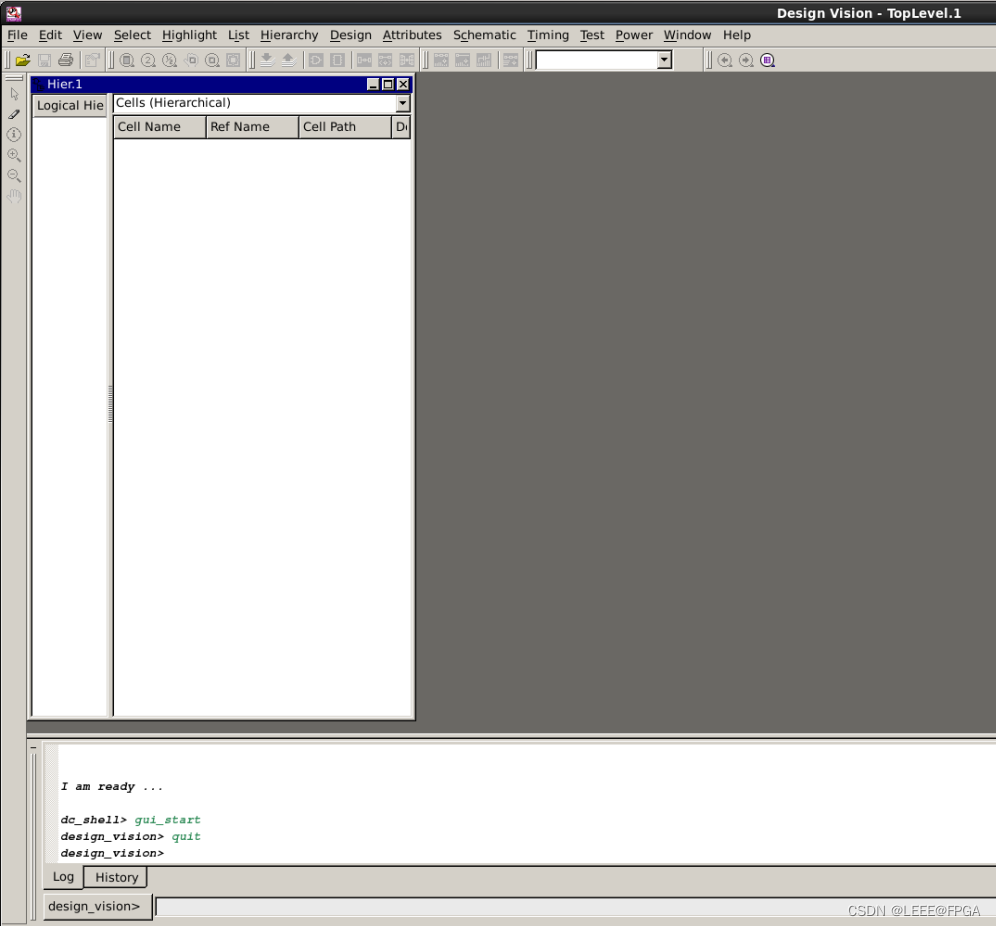

3 Design Compiler和Design Vision

Synopsys Design Compiler(DC)和Design Vision(DV)構(gòu)成一套功能強大的邏輯綜合工具,根據(jù)設(shè)計規(guī)范和時序約束,提供最佳的門極綜合網(wǎng)表。除了高層次綜合能力,還包含一個靜態(tài)時序分析引擎,提供FPGA綜合和links-to-layout(LTL)解決方案。

可以在命令行輸入dc_shell進(jìn)入DC,也可以輸入design_vision進(jìn)入DV,DV是DC的圖形化版本,也可以使用命令dc -gui進(jìn)入。

$design_vision

DC Professional (TM)

DC Expert (TM)

DC Ultra (TM)

FloorPlan Manager (TM)

HDL Compiler (TM)

VHDL Compiler (TM)

Library Compiler (TM)

DesignWare Developer (TM)

DFT Compiler (TM)

BSD Compiler

Power Compiler (TM)

Version D-2010.03 for linux -- Feb 22, 2010

Copyright (c) 1988-2009 by Synopsys, Inc.

ALL RIGHTS RESERVED

This software and the associated documentation are confidential and

proprietary to Synopsys, Inc. Your use or disclosure of this software

is subject to the terms and conditions of a written license agreement

between you, or your company, and Synopsys, Inc.

The above trademark notice does not imply that you are licensed to use

all of the listed products. You are licensed to use only those products

for which you have lawfully obtained a valid license key.

Initializing...

Settings:

search_path: . /Tools/dc/libraries/syn /Tools/dc/dw/syn_ver /Tools/dc/dw/sim_ver ../ref/db ./scripts ./rtl ./mapped ./unmapped

link_library: * sc_max.db

target_library: sc_max.db

symbol_library: sc.sdb

I am ready ...

4 Physical Compiler

Physical Compiler(PhyC)是DC的一個超集。除了包含DC全部的綜合和優(yōu)化功能,還提供了根據(jù)設(shè)計的時序和/或面積約束同時優(yōu)化放置單元的能力。

5 PrimeTime

PrimeTime(PT)是Synopsys的簽約級、全芯片、門級靜態(tài)時序分析工具。它是一個獨立運行的工具,可以通過命令行輸入pt_shell進(jìn)入。

PrimeTime(PT)是Synopsys的sign-off quality的靜態(tài)時序分析工具。PrimeTime可以集成于邏輯綜合和物理綜合的流程,讓設(shè)計者分析并解決復(fù)雜的時序問題,并提高時序收斂的速度。

6 DFT Compiler

DFT Compiler(DFTC)是包含在DC全套工具中的測試插入工具,用于向設(shè)計中插入DFT特征,如掃描插入和邊界掃描,可以直接在dc_shell中調(diào)用所有指令。

6.1. 關(guān)鍵性功能

DFT Compiler及DFTMAX 工具提供以下功能:

· 一步到位的測試綜合,即一次性完成所有掃描單元的連接。

· 綜合流程中RTL級和門級代碼的DFT設(shè)計規(guī)則檢查

· 快速的掃描綜合

· DFTMAX 掃描壓縮

· 分層次的掃描綜合(標(biāo)準(zhǔn)掃描和壓縮掃描)

· 測試點插入(Test point insertion)

· 自動修復(fù)DFT違例(AutoFix)

· 基于位置的掃描排序

· 基于時序的掃描排序

6.2. 關(guān)鍵性優(yōu)勢

DFT Compiler可使你快速精確地計算可測性并在設(shè)計周期早期解決任何測試問題。RTL測試設(shè)計規(guī)則檢查可幫你寫出在one-pass測試綜合環(huán)境中易于綜合的RTL代碼。DC環(huán)境中測試的整合可保證可預(yù)測的時序收斂并實現(xiàn)掃描設(shè)計的物理優(yōu)化。

下面簡單列一下DFT Compiler的優(yōu)勢:

· 在綜合流程中提供透明的DFT實現(xiàn)

· 在設(shè)計周期早期計算RTL代碼的可測性

· 在設(shè)計周期后端刪除不可測性

· 實現(xiàn)的可測的時序、功率、及測試同時發(fā)生的信號完整性收斂

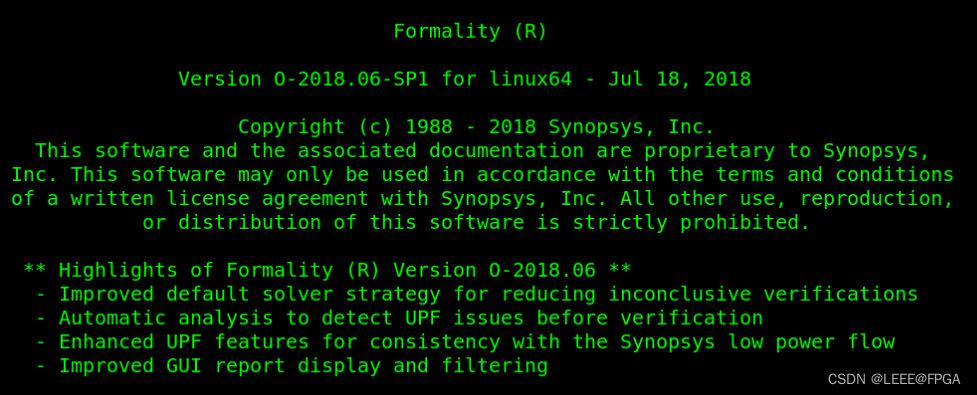

7 Formality

Formality是Synopsys的形式驗證工具,是一種邏輯等價檢測工具,以檢查設(shè)計的RTL和門級網(wǎng)表描述是否代表相同的設(shè)計。是否DC將部分邏輯消除了。

審核編輯 :李倩

-

Synopsys

+關(guān)注

關(guān)注

2文章

157瀏覽量

90127 -

應(yīng)用程序

+關(guān)注

關(guān)注

37文章

3243瀏覽量

57603

原文標(biāo)題:7 Formality

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

CDCI6214EVM里面是否包含有I2C轉(zhuǎn)UART接口板對程序進(jìn)行EPROM的燒錄?

FPGA仿真工具包軟件EasyGo Vs Addon介紹

采用德州儀器 (TI) 工具包進(jìn)行模擬前端設(shè)計應(yīng)用說明

使用freeRTOS開發(fā)工具包時,在哪里可以找到freeRTOS的版本?

Synopsys推出一款低功耗靜態(tài)規(guī)則檢查工具—VCLP

QE for Motor V1.3.0:汽車開發(fā)輔助工具解決方案工具包

求助,請問有沒有l(wèi)abview opc ua工具包 2018 啊

GreenHills Software、HighTec、Synopsys、Tasking、Windriver的開發(fā)環(huán)境有什么好處嗎?

Synopsys將以350億美元并購Ansys

labview工具包下載

利用ProfiShark 構(gòu)建便攜式網(wǎng)絡(luò)取證工具包

解決方案工具包QE顯示[RX,RA]V3.2.0:用于顯示應(yīng)用程序的開發(fā)輔助工具

![解決方案<b class='flag-5'>工具包</b>QE顯示[RX,RA]V3.2.0:用于顯示應(yīng)用程序的開發(fā)輔助<b class='flag-5'>工具</b>](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

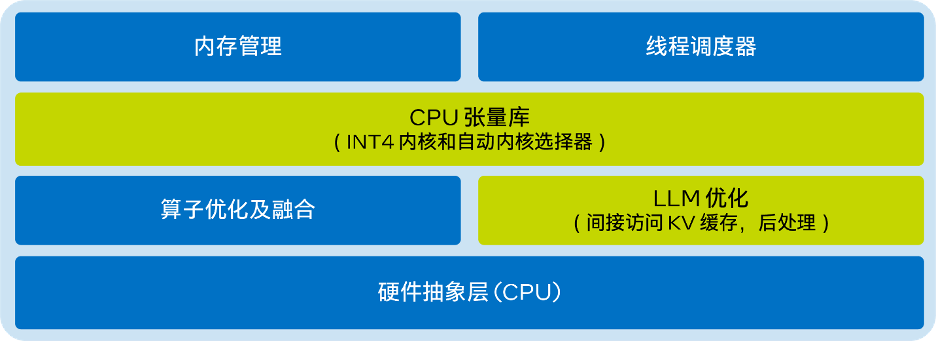

用上這個工具包,大模型推理性能加速達(dá)40倍

Synopsys系列工具包含

Synopsys系列工具包含

評論