UltraScale和UltraScale+進一步增強了Clock root的概念,從芯片架構和Vivado支持方面都體現了這一點。為了理解這一概念,我們先看看UltraScale/UltraScale+的時鐘資源。

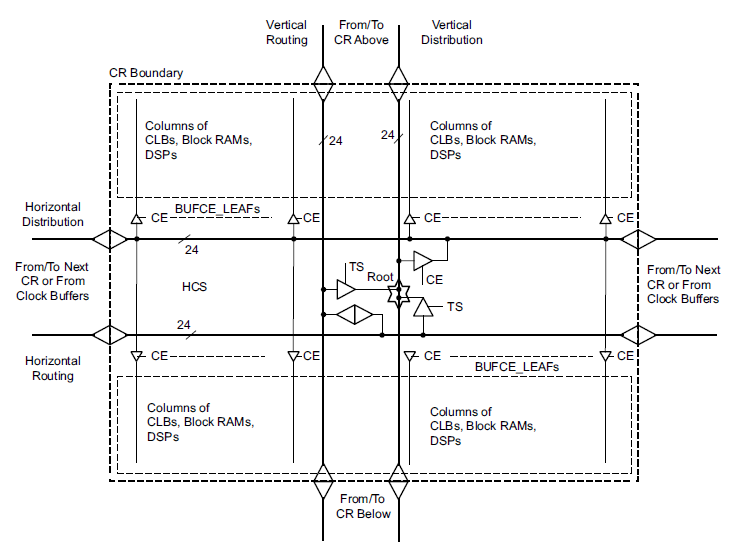

每個時鐘區域有24個水平分發軌道(HorizontalDistribution)和水平布線軌道(HorizontalRouting),同時,垂直方向也有24個分發軌道(VerticalDistribution)和24個布線軌道(Vertical Routing),如下圖所示。

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時鐘

+關注

關注

10文章

1720瀏覽量

131364 -

UltraScale

+關注

關注

0文章

117瀏覽量

31450

原文標題:設計中的Clock root可以修改嗎?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件可快速啟動汽車、工業、視頻和通信應用設計。AMD/Xilinx MPSoC ZCU102 評估套件采用

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

電子發燒友網站提供《為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電.pdf》資料免費下載

發表于 09-25 10:54

?0次下載

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

電子發燒友網站提供《使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電.pdf》資料免費下載

發表于 09-21 11:11

?0次下載

一個更適合工程師和研究僧的FPGA提升課程

設計;

● UltraFast 設計方法;

● 使用UltraScale和UltraScale+架構進行設計;

● FPGA 功耗最優化;

● 使用 Vivado Design Suite 4

發表于 06-05 10:09

中高端FPGA如何選擇

為了使數據傳輸更加高效,Achronix FPGA上的Memory資源也是非常給力,不管是片上Ram還是DDR接口,都比Virtex Ultrascale+有很大優勢。

在Speedster7t

發表于 04-24 15:09

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 已經擁有 Zynq UltraScale+ 和 Artix UltraScale+ 系列,而 Spartan UltraScale+ FPGA 系列的推出使其不斷現代化。

發表于 03-18 10:40

?348次閱讀

AMD 擴展市場領先的 FPGA 產品組合,推出專為成本敏感型邊緣應用打造的AMD Spartan UltraScale+ 系列

股票代碼:AMD)今日宣布推出 AMD Spartan? UltraScale+? FPGA 系列,這是廣泛的 AMD 成本優化型 FPGA 和自適應 SoC 產品組合的最新成員。Spartan

發表于 03-07 15:17

?451次閱讀

AMD推出Spartan UltraScale+ FPGA系列產品

AMD公司,全球知名的芯片巨頭,近日宣布推出全新的AMD Spartan UltraScale+ FPGA系列產品組合。這一新系列作為AMD成本優化型FPGA、自適應SoC產品家族的最新成員,特別針對成本敏感型邊緣應用進行了優化,旨在提供更高的成本效益和能效性能。

為嵌入式應用選擇AMD Spartan UltraScale+FPGA

全新 AMD Spartan UltraScale+ FPGA 系列在價格、功耗、功能和尺寸之間取得了良好的平衡。了解該系列器件如何幫助設計人員以低成本推動 I/O 密集型應用產品快速上市。

AMD 擴展市場領先的 FPGA 產品組合,推出專為成本敏感型邊緣應用打造的AMD Spartan UltraScale+ 系列

股票代碼:AMD)今日宣布推出 AMD Spartan? UltraScale+? FPGA 系列,這是廣泛的 AMD 成本優化型 FPGA 和自適應 SoC 產品組合的最新成員。Spartan

發表于 03-06 11:17

?333次閱讀

AMD推出全新Spartan UltraScale+ FPGA系列

AMD日前正式推出了全新的Spartan UltraScale+ FPGA系列,該系列作為AMD廣泛的成本優化型FPGA和自適應SoC產品組合的最新成員,專為邊緣端各種I/O密集型應用設計。

1.25G突發時鐘數據恢復/ UltraScale中的2.5G PON應用設備總結

電子發燒友網站提供《1.25G突發時鐘數據恢復/ UltraScale中的2.5G PON應用設備總結.pdf》資料免費下載

發表于 01-14 09:56

?0次下載

針對UltraScale/UltraScale+芯片DFX應考慮的因素有哪些(2)

UltraScale/UltraScale+芯片開始支持BUFG_*、PLL和MMCM出現在動態區,在7系列FPGA中這些時鐘資源只能在靜態區。

UltraScale/UltraScale+的時鐘資源

UltraScale/UltraScale+的時鐘資源

評論