關于RISC和CISC處理器的區別,大多數人會認為是一些特性、指令,或者是晶體管數量的差異。但實際上兩者之間的差別不能簡單的一概而論。

少量指令并不意味著RISC

首先,我們需要摒棄一些非常明顯的誤解。因為RISC的意思是簡化指令集計算機(Reduced Instruction Set Computer),所以很多人認為RISC處理器只是一個沒有多少指令的CPU。如果是這樣的話,那么6502處理器將是有史以來最RISCy的處理器之一,它只有56條指令。甚至英特爾8086也可以算作RISC處理器,因為它只有81條指令。即使是后來的Intel 80286也只有大約100條指令。 像AVR這樣簡單的8位RISC處理器有78條指令。如果您看看最早的32位RISC處理器之一,比如PowerPC 601(1993年發布),它有273個指令。 MIPS32指令集來源于伯克利的原始RISC處理器,它也有200多條指令。 我們可以將其與CISC 32位處理器(如80386)進行比較,后者只有略多于170條指令。差不多時間亮相的MIPS R2000處理器在大約有92條指令。

For the curios:

x86 instruction listings

Pentium instruction set

6502 Instruction Set

MIPS R2000 InstructionSet

古玩: x86指令列表 奔騰指令集 6502指令集 MIPS R2000指令集 也就是說,類似x86指令集、奔騰指令集、6502指令集、MIPS R2000指令集一開始都具有很少指令集,但它們都不是RISC處理器。

少數晶體管并不意味著RISC

CISC和RISC處理器之間的晶體管數量的分界點是多少?根本沒有。6502有4528個晶體管。第一個ARM處理器有25000個晶體管。 或者這個有趣的小事實。摩托羅拉68060被認為是那個時代最具代表性的CISCy的處理器之一,它只有250萬個晶體管,比1994年發布的IBM PowerPC 601的280萬個晶體管還要少。 如果你看一下幾乎同時發布的RISC和CISC處理器,沒有明顯的趨勢表明RISC處理器比CISC處理器有更少的晶體管和更少的指令。

上世紀90年代初流行的RISC和CISC處理器晶體管和指令的比較 所以讓我們得出結論,我們不能根據晶體管或指令數量區分RISC或CISC芯片。但是問題仍然存在,到底是什么是RISC微處理器或CISC微處理器?

RISC和CISC是不同的晶體管預算理念

當你的老板告訴你“這里,有一百萬個晶體管,給我做一個快速的處理器!”,那么你就有很多方法可以實現這個目標。對于相同數量的晶體管,RISC和CISC的設計者將會做出不同的選擇。 伯克利的David A. Patterson廣為人所知的可能是他在1980年發表的論文《簡化指令集計算機的案例》中推廣了RISC處理器的思想。 Patterson在這篇論文中概述的并不是芯片制造的詳細藍圖,而更像是哲學指導方針。 在現實世界的程序中,添加這個指令會提高多少性能?硬件方面的影響是什么?我們是否需要存儲大量復雜的狀態,這使得上下文切換和無序執行更加復雜,因為需要存儲大量的狀態? 一個設計良好的簡單指令的組合能以相當的性能完成同樣的工作嗎? 我們是否可以利用現有的算術邏輯單元(ALUs)和CPU上的其他資源來添加這條指令,或者我們需要添加很多新東西? 如果不添加這條指令,這些晶體管的其他用途是什么?更多的緩存嗎?更好的分支預測嗎? 重要的是要理解這些規則適用于給定的晶體管預算。如果你有更多的晶體管,你可以添加更多的指令,甚至更復雜的指令。 然而,RISC的哲學優先考慮保持指令集的簡單。這意味著RISC設計者首先會嘗試通過其他方法來提高性能,而不是添加如下指令:

使用晶體管增加更多的緩存

更多的CPU寄存器

更好的管道

更好的分支預測

超標量體系結構的體系結構

添加更多的指令解碼器

亂序執行

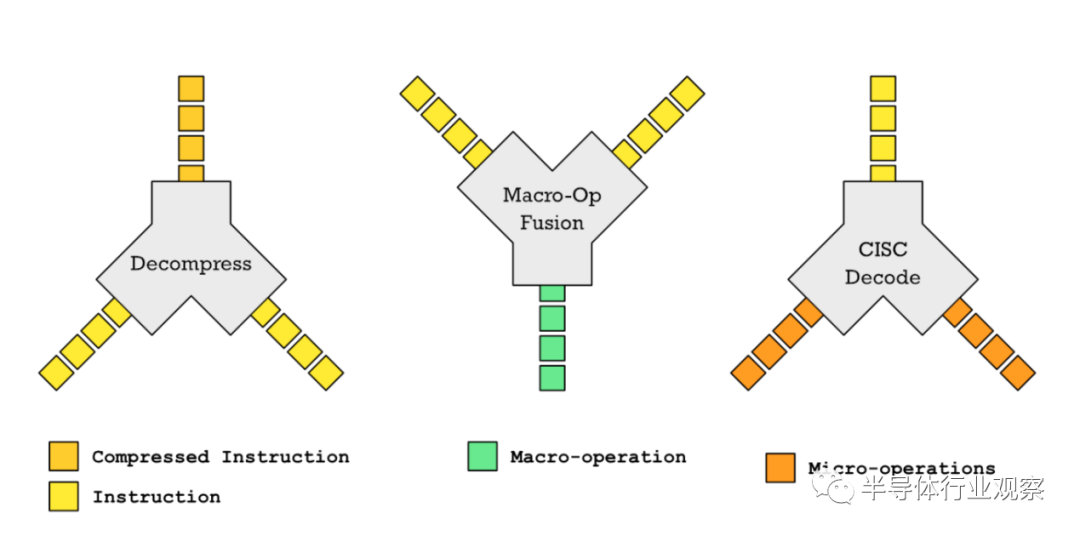

Macro-operation融合

壓縮指令

因此,設計一個好的RISC指令集(ISA)的一個關鍵目標是使設計不妨礙未來的微架構優化。 這與CISC設計者設計CPU的方式不同。為了能夠提供更好的性能,那么CISC設計者將添加引入更多狀態以跟蹤狀態寄存器等復雜指令。

CISC設計理念的問題

問題是CISC的設計師沒有超前思考。將來你的晶體管預算可能會增加。突然之間,你有了所有這些好的晶體管,可以用來創建無序(OoO)超標標量處理器邏輯。這意味著您在每個時鐘周期解碼多個指令,并將它們放在一個指令隊列中。然后,OoO邏輯會找出哪些指令不相互依賴,以便它們可以并行運行。 如果您是軟件開發人員,您可以考慮函數式編程(functional programming)和命令式編程(imperative programming)之間的區別。為了獲得短期性能收益而改變全局數據可能很誘人。然而,一旦你并行運行,而全局狀態被多個函數改變了,這可能會在多個線程中并行運行,這絕對是一場噩夢。 函數式編程喜歡只依賴于輸入而不依賴全局數據的純函數。這些函數可以很容易地并行運行。同樣的機制也適用于CPU。不依賴于全局狀態(如狀態寄存器)的匯編代碼指令可以更容易地并行或流水線運行。 RISC-V就是這種思想的一個很好的例子。RISC-V沒有狀態寄存器。比較和跳轉指令合二為一。除非運行額外的計算來確定是否發生了溢出,否則無法用狀態寄存器捕獲整數溢出。 這應該會給你一些關于RISC和CISC區別的線索。

一個RISC處理器設計的優先級

如果10條新指令對微架構沒有顯著影響,那么RISC設計者添加10條新指令不一定會有問題。如果一條指令要求在CPU中表示更多的全局狀態,那么RISC設計人員將會非常不愿意添加一條指令。 這種哲學的最終結果是,從歷史上看,在RISC處理器上添加管道和超標量架構比CISC處理器更容易,因為人們避免了添加指令,從而引入狀態管理或控制邏輯,這使得添加這些微架構創新變得困難。 這就是為什么RISC-V團隊更喜歡進行宏操作(macro-operation)融合,而不是添加支持復雜尋址模式或整數溢出檢測的指令。 RISC的理念導致了不斷出現的特殊設計選擇,這讓我們能夠討論在比較RISC和CISC處理器時所觀察到的更具體的差異。讓我們看看這些。

現代RISC和CISC處理器的特點

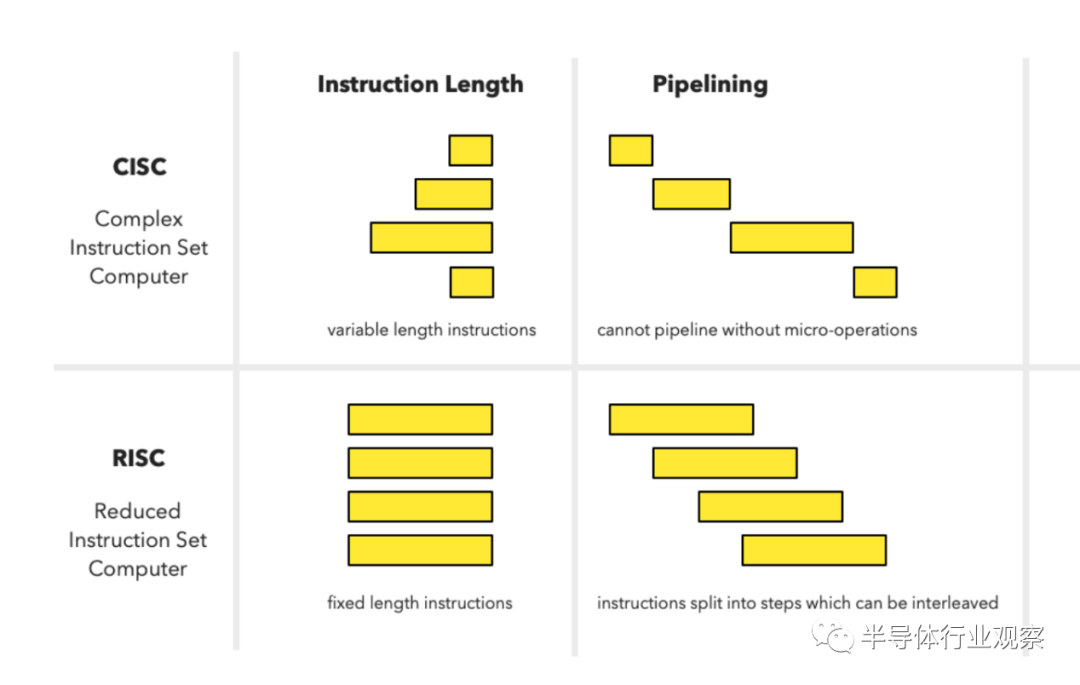

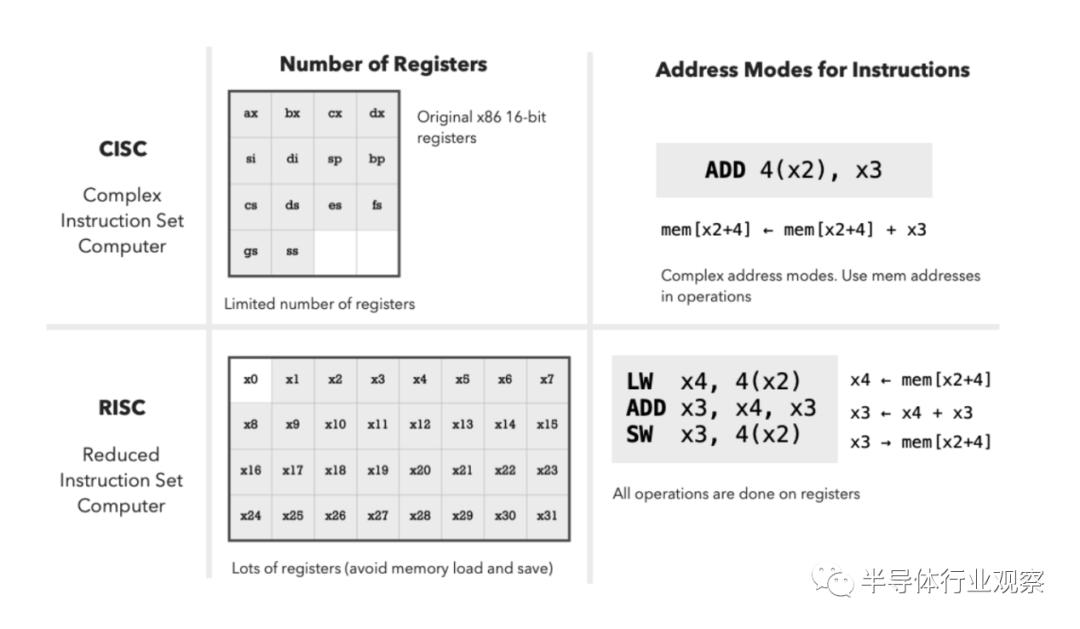

某些設計選擇不斷出現在許多不同的RISC處理器上。通常情況下,RISC處理器傾向于使用固定長度的32位指令。也有一些例外,比如AVR,它使用固定長度的16位指令。相比之下,Intel x86處理器的指令長度為1到15字節。摩托羅拉68k處理器,另一個著名的CISC設計,有2到10字節長的指令(16位到80位)。

對于匯編程序員來說,變長指令實際上非常方便。我的第一臺電腦是Amiga 1000,它有一個摩托羅拉68k處理器,所以它向我介紹了68k組裝,坦白說非常整潔。它有將數據從一個內存位置移動到另一個內存位置的指令,或者可以將數據從寄存器A1給出的地址移動到另一個寄存器A2給出的內存位置。 ; 68k Assembly code

MOVE.B 4, 12 ; mem[4] → mem[12]

MOVE.B (A1), (A2) ; mem[A1] → mem[A2] 這樣的指令使CPU易于編程,但這意味著沒有辦法將支持的每條指令都放在32位內,因為表示完整的源地址和目的地址將只消耗64位。因此,通過使用變長指令,我們可以很容易地在任何指令中包含完整的32位內存地址。 然而,這種便利是有代價的。變長指令更難以流水線處理,如果你想讓一個超標標量處理器并行解碼兩條或多條指令,你很難做到這一點,因為你不知道每條指令在哪里開始和結束,直到你解碼它們。

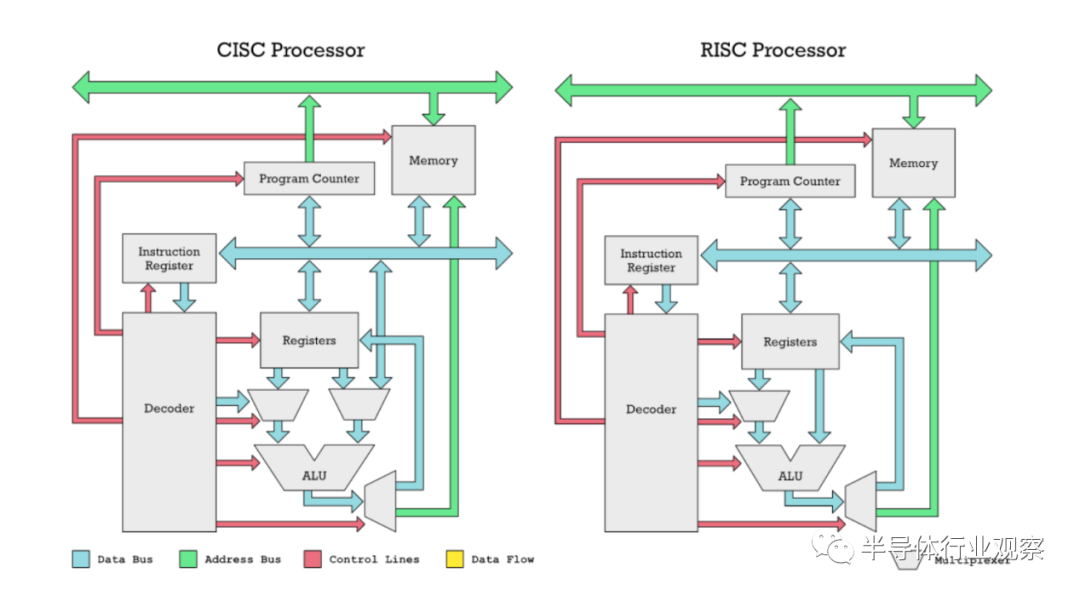

使用超標量處理器,可以有多個指令解碼器并行工作。 RISC處理器傾向于避免使用可變長度指令,因為這不符合RISC不添加指令的理念,這也使得添加更高級的微架構優化變得更加困難。 固定長度的指令會造成不便。您不能將內存地址放入任何操作中,只能放入特定的操作,如加載和存儲指令。

在RISC處理器中的算術邏輯單元(ALU)只能從寄存器而不是內存中獲取輸入。

加載/存儲體系結構

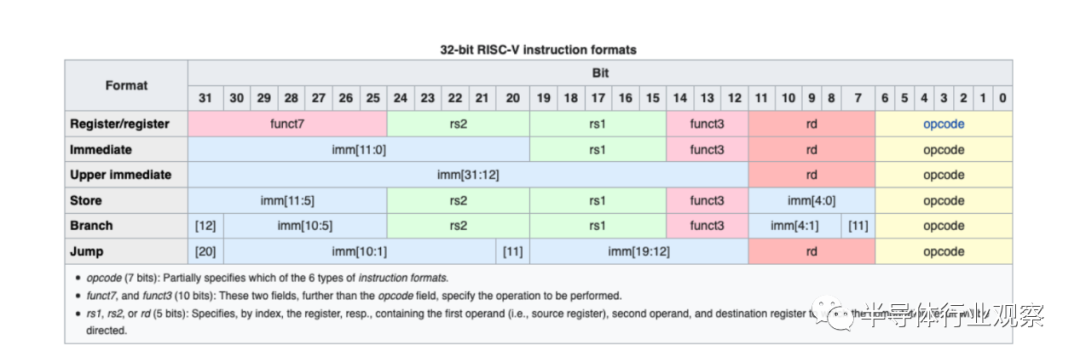

機器代碼指令必須對正在執行的信息進行編碼,例如它是在執行ADD、SUB還是MUL。它還必須對輸入的信息進行編碼。輸入寄存器和輸出寄存器是什么。一些指令需要對要加載數據的地址進行編碼。在RISC-V指令中是這樣編碼的:

上圖顯示了如何使用32位字中的每一位為RISC-V指令集編碼一條指令 我們執行的特定指令稱為操作碼(上圖黃色),它消耗7位。我們指定的每個寄存器輸入或輸出都需要5位。從這里應該很清楚,擠入一個32位地址是不可能的。即使是一個較短的地址也是困難的,因為你需要位來指定在操作中使用的寄存器。對于CISC處理器,這不是一個問題,因為您可以自由地使用超過32位的指令。 這種緊湊的空間要求使得RISC處理器具有我們所說的加載/存儲架構。只有專用的加載和存儲指令,如RISC-V上的LW和SW,才能用于訪問內存。 對于CISC處理器,如68k,幾乎任何操作,如ADD、SUB、AND和OR,都可以使用內存地址作為操作數(參數)。在下面的例子中,4(A2)計算到一個內存地址,我們使用它來讀取一個操作數(參數)到ADD指令。最終的結果也存儲在那里(在68k上destination是右參數)。 ; 68k assembly

ADD.L D3, 4(A2) ; D3 + mem[4 + A2] → mem[4 + A2] 典型的RISC處理器(如基于RISC- v指令集的處理器)需要將加載(LW)和存儲(SW)作為單獨的指令進行存儲。 # RISC-V assembly

LW x4, 4(x2) # x4 ← mem[x2+4]

ADD x3, x4, x3 # x3 ← x4 + x3

SW x3, 4(x2) # x3 → mem[x2+4] 你不需要通過結合地址寄存器(A0到A7)來計算地址。你可以直接指定一個內存地址,比如400: ; 68k assembly

ADD.L 400, D4 ; mem[400] + D4 → D4 但即使是這樣一個看似簡單的操作也需要多個RISC指令。 # RISC-V assembly

LW x2, 400(x0) # x3 ← mem[x0 + 400]

ADD x4, x4, x3 # x4 ← x4 + x3 在很多RISC設計中,x0寄存器總是0,這意味著即使你只對絕對內存地址感興趣,你也可以始終使用偏移加基寄存器的形式。雖然這些偏移量看起來與您在68k上所做的非常相似,但它們的限制要大得多,因為您總是需要適合一個32位字。使用68k,可以給ADD.L一個完整的32位地址。你不能用RISC-V LW和SW。獲得完整的32位地址是相當麻煩的。假設您希望從32位地址:0x00042012加載數據,則必須分別加載上面的20位和下面的12位,以形成一個32位地址。 # RISC-V assembly

LUI x3, 0x42 # x3[31:12] ← 0x42 put in upper 20-bits

ADDI x3, x3, 0x12 # x3 ← x3 + x3 + 0x12

LW x4, 0(x3) # x4 ← mem[x3+0] 實際上這可以簡化為:LUI x3, 0x42 LW x4, 0x12(x3) 我記得當我從68k組裝轉到PowerPC(蘋果以前使用的RISC處理器)時,這讓我很惱火。當時我認為RISC意味著一切都將變得更容易。我發現x86很麻煩,很難處理。然而,對于匯編編碼員來說,RISC不像68k那樣方便地使用CISC指令集。幸運的是,有一些簡單的技巧可以使這個過程在RISC處理器上變得更容易。RISC-V定義了一些偽指令,以簡化匯編代碼的編寫。使用LA (load address)偽指令,我們可以像這樣編寫前面的代碼: # RISC-V assembly with pseudo instructions

LI x3, 0x00042012 # Expands to a LUI and ADDI

LW x4, 0(x3) 總而言之:雖然加載/存儲體系結構使編寫匯編代碼變得更麻煩,但它允許我們保持每個指令為32位長。這意味著創建一個可以并行解碼多個指令的超標標量微體系結構需要更少的晶體管來實現。流水線化每條指令變得更容易,因為它們中的大多數可以適合經典的5步RISC流水線。

RISC處理器有很多寄存器

使用像68k這樣的高級CISC處理器,您可以用一條指令做很多事情。假設您想將數字從一個數組復制到另一個數組。下面是一個使用指針的C語言例子: // C code

int data[4] = {4, 8, 1, 2, -1};

int *src = data;

while (*xs > 0)

*dst++ = *src++; 如果你在68k處理器上將指針src存儲在地址寄存器A0中,將指針dst存儲在地址寄存器A1中,你可以在一條指令中復制并向前移動每個指針4個字節: ; 68k assembly

MOVE.L (A0)+,(A1)+ ; mem[A1++] → mem[A2++] 這只是一個例子,但是一般來說,您可以使用CISC指令做更多的事情。這意味著您需要更少的代碼。因此,RISC設計者意識到他們的代碼會變得臃腫。因此,RISC的設計者們分析了真實的代碼,提出了一種方案,可以在不使用復雜指令的情況下減少代碼的大小。他們發現很多代碼只是用來加載和存儲內存中的數據。通過添加大量寄存器,可以將臨時結果保存在寄存器中,而無需將它們寫入內存。這將減少需要執行的加載和存儲指令的數量,從而減少代碼的RISC代碼大小。 因此,MIPS、SPARC、Arm(64位)和RISC-V處理器有32個通用寄存器。我們可以對比一下原來的x86,它只有8個通用寄存器。

復雜性的RISC/CISC視角

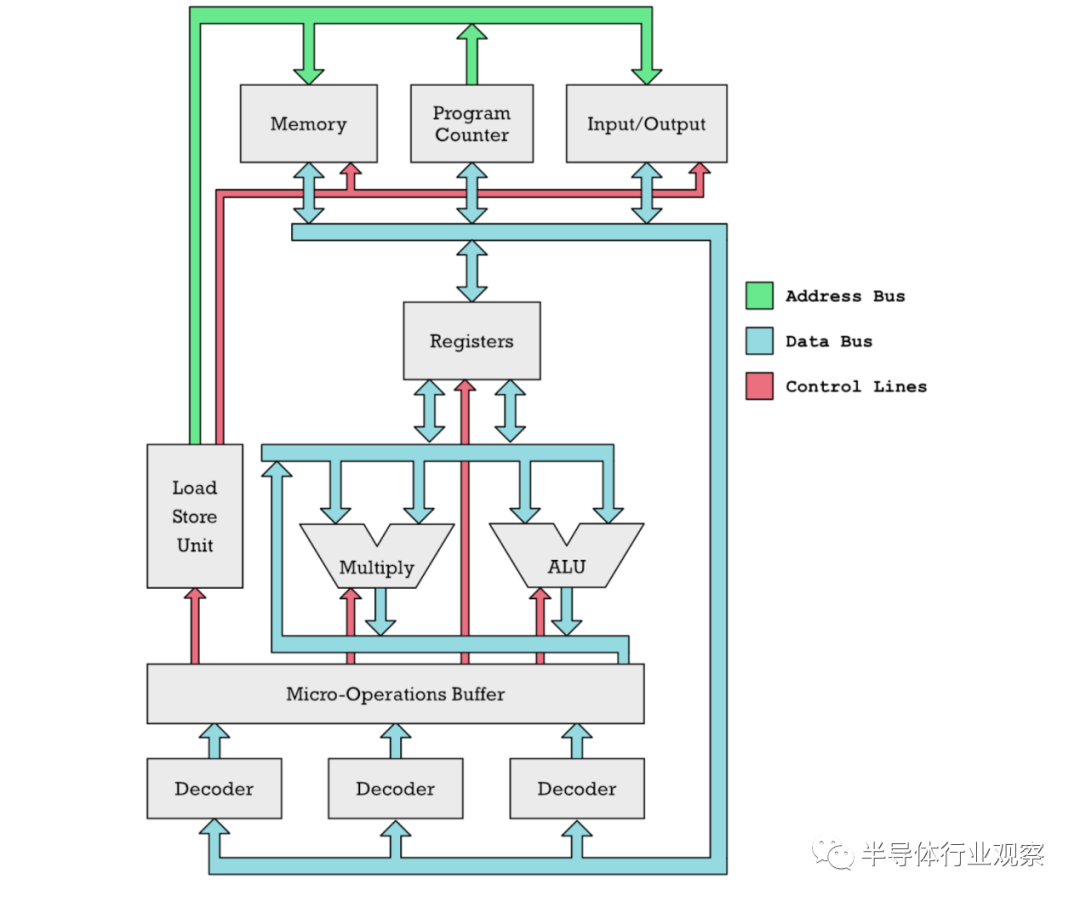

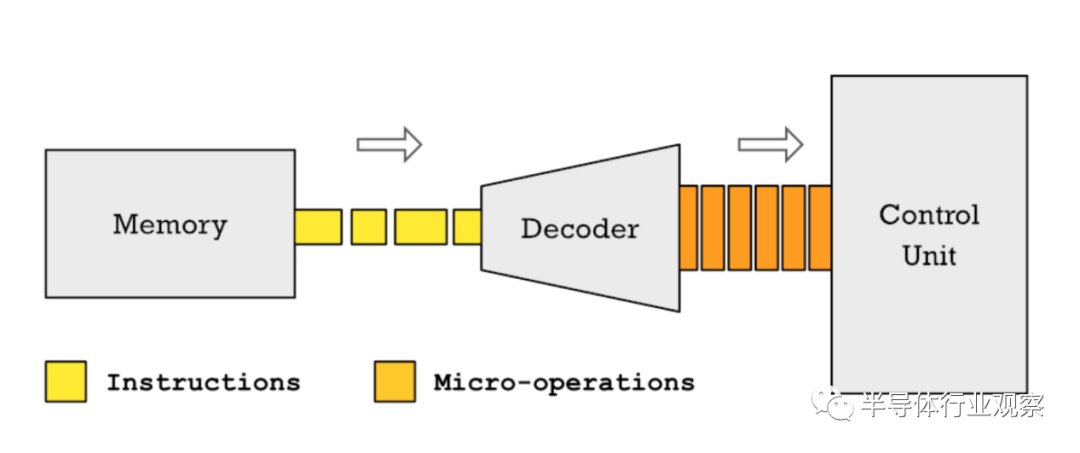

我在這個故事中想要說明的是,RISC處理器并不比CISC處理器差。區別在于RISC和CISC的設計者選擇增加復雜性。 CISC設計人員將復雜性放在指令集體系結構(ISA)中,而RISC設計人員寧愿將復雜性添加到他們的微體系結構中,但正如我一直強調的,他們不希望指令集在微架構中強加復雜性。 讓我來比較一下MIPS R4000,摩托羅拉68040和英特爾486,以強調理念上的差異。它們都有大約120萬個晶體管,幾乎同時發布(1989年至1991年)。 RISC處理器(R4000)是64位的,其他是32位的。 R4000有8級pipeline ,允許比6級pipeline 的68040和5級pipeline 的486更高的時鐘頻率。 更長的pipeline 給R4000從100-200 Mhz遠遠超過68040的40Mhz和486DX2得到66Mhz (100Mhz在一個更晚的模型)。 最終在1993/1994年出現了速度更快的CISC處理器,如68060和Pentium。但與此同時出現了MIPS R8000,它是一種可以并行解碼4條指令的超標量結構。奔騰處理器每個時鐘周期只能解碼2條指令。 所以我們可以看到RISC的設計者們是如何喜歡花哨的微架構而不是花哨的指令的。 “但是現代CISC處理器有復雜的微架構!” 您可能會抗議說,今天的CISC處理器有復雜的微架構。他們所做的。一個現代的Intel或AMD處理器有多個解碼器、微操作緩存、高級分支預測器、無序(OoO)執行引擎。然而,這并不奇怪。記住我關于晶體管預算理念的關鍵點:今天每個人都有很多晶體管可以使用,所以所有高端芯片都將有很多先進的微架構功能。他們可以負擔得起他們的預算。 關鍵在于:這些復雜的微體系結構特性中的許多都是由復雜的CISC指令集強加的。例如,為了使pipelines 工作,x86處理器將其冗長復雜的指令分解成微操作。微操作很簡單,行為更像RISC操作,因此它們可以更容易地流水線化。

問題是把CISC指令分解成更簡單的微觀操作并不容易。因此,許多現代的超標標量x86處理器對簡單指令有3個指令解碼器,對復雜指令有1個解碼器。由于您不知道每條指令從哪里開始和結束,CISC處理器不得不進行一場涉及許多晶體管的復雜的猜謎游戲。 RISC處理器避免了這種復雜性,可以將所有浪費的晶體管用于添加更多的解碼器或進行其他優化,如使用壓縮指令或宏操作融合(將非常簡單的指令組合成更復雜的指令)。

在不同的CPU設計中,指令可以以不同的方式組合或分割。 如果你將蘋果的M1處理器(這是一個基于RISC的處理器)與AMD和英特爾的處理器做比較,你會注意到它有更多的指令解碼器。CISC的設計人員試圖通過添加微操作緩存來緩解這個問題。有了微操作緩存,CISC處理器就不必克服障礙,也不必一遍又一遍地解碼相同的復雜指令。然而,增加這一功能顯然會消耗晶體管的成本。它不是免費的。因此,你正在把你的晶體管預算浪費在微架構的復雜性上,這只是因為ISA的復雜性。

Arm vs RISC-V設計理念

比較現代RISC和CISC處理器的一個問題是,RISC基本上贏了。沒有人再從頭開始設計CISC處理器了。Intel和AMD的x86處理器今天之所以流行,主要是因為向后兼容。 如果你今天讓一個設計團隊坐下來,告訴他們從頭開始設計一個高性能處理器,那么你最終不會得到傳統的CISC設計。 然而,這并不意味著在RISC社區中,有多少設計師傾向于CISC或RISC的方向上沒有差異。現代的Arm處理器和基于RISC-V的處理器就是這種對比的有趣例子。 Arm的設計者更愿意添加復雜的指令來提高性能。請記住,不是Arm不是RISC設計。當你的晶體管預算增長,增加更復雜的指令是公平的。。 RISC-V的設計者更熱衷于將ISA的復雜性保持在最低程度,而不是增加微架構的復雜性,從而通過使用壓縮指令和宏操作融合等技巧來提高性能。我在這里討論這些設計選擇:RISC-V微處理器的天才。 Arm和RISC-V的不同選擇不是隨意的,而是受到非常不同的目標和市場的很大影響。Arm越來越多地進入高端市場。請記住,蘋果的Arm芯片正在與x86芯片展開正面競爭,不久,英偉達也會這樣做。 RISC-V的目標是成為一個更廣泛的架構,用于從鍵盤到人工智能加速器、從gGPU到專門的超級計算機的任何東西。這意味著RISC-V意味著靈活性,您添加的指令越復雜,您施加的復雜性就越小,從而減少了為特定用例定制芯片的自由。

審核編輯 :李倩

-

CISC

+關注

關注

1文章

31瀏覽量

19495 -

RISC-V

+關注

關注

44文章

2229瀏覽量

46032

原文標題:RISC和CISC,究竟有何不同?

文章出處:【微信號:strongerHuang,微信公眾號:strongerHuang】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶體管的輸出特性是什么

NMOS晶體管和PMOS晶體管的區別

CMOS晶體管和MOSFET晶體管的區別

CISC(復雜指令集)與RISC(精簡指令集)的區別

晶體管處于放大狀態的條件是什么

什么是NPN晶體管?NPN晶體管的工作原理和結構

PNP晶體管符號和結構 晶體管測試儀電路圖

如何提高晶體管的開關速度,讓晶體管快如閃電

什么是達林頓晶體管?達林頓晶體管的基本電路

晶體管Ⅴbe擴散現象是什么?

如何根據管腳電位判斷晶體管

晶體管是如何工作的?BJT和MOSFET晶體管區別

使用晶體管作為開關

RISC和CISC是不同的晶體管預算理念

RISC和CISC是不同的晶體管預算理念

評論