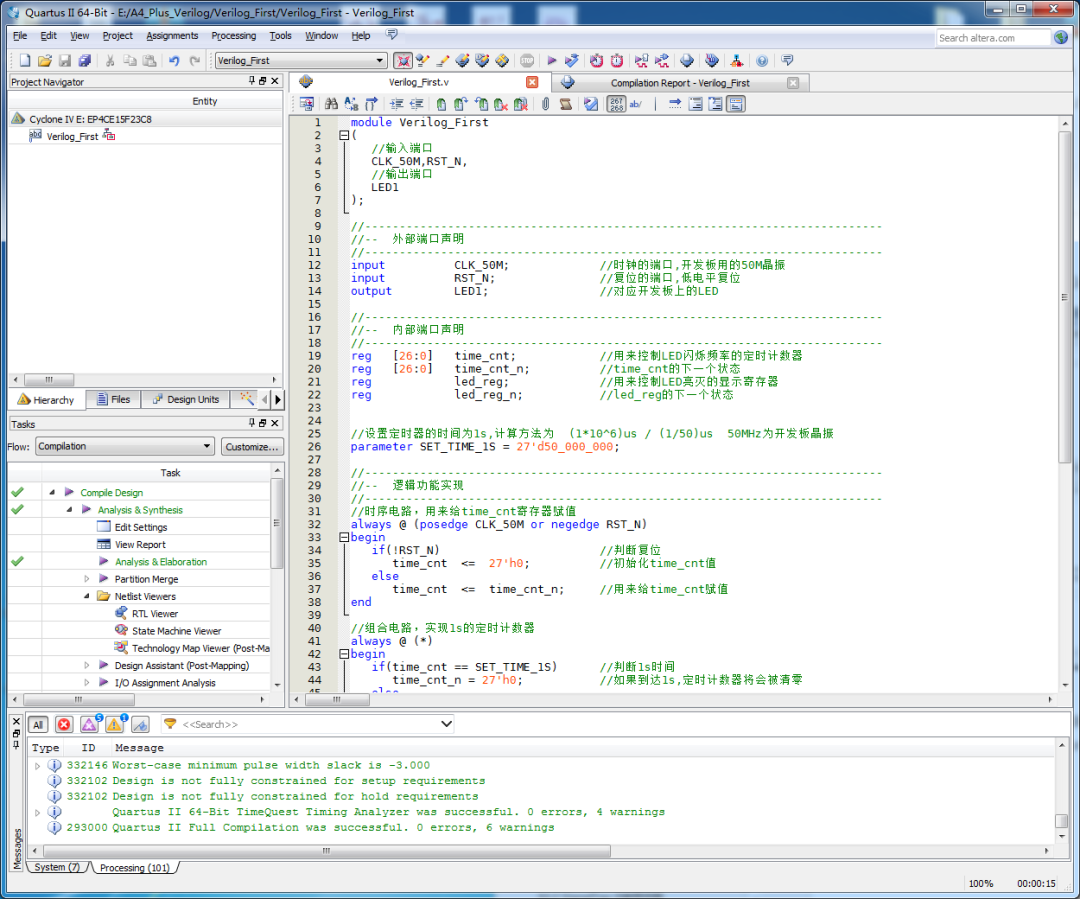

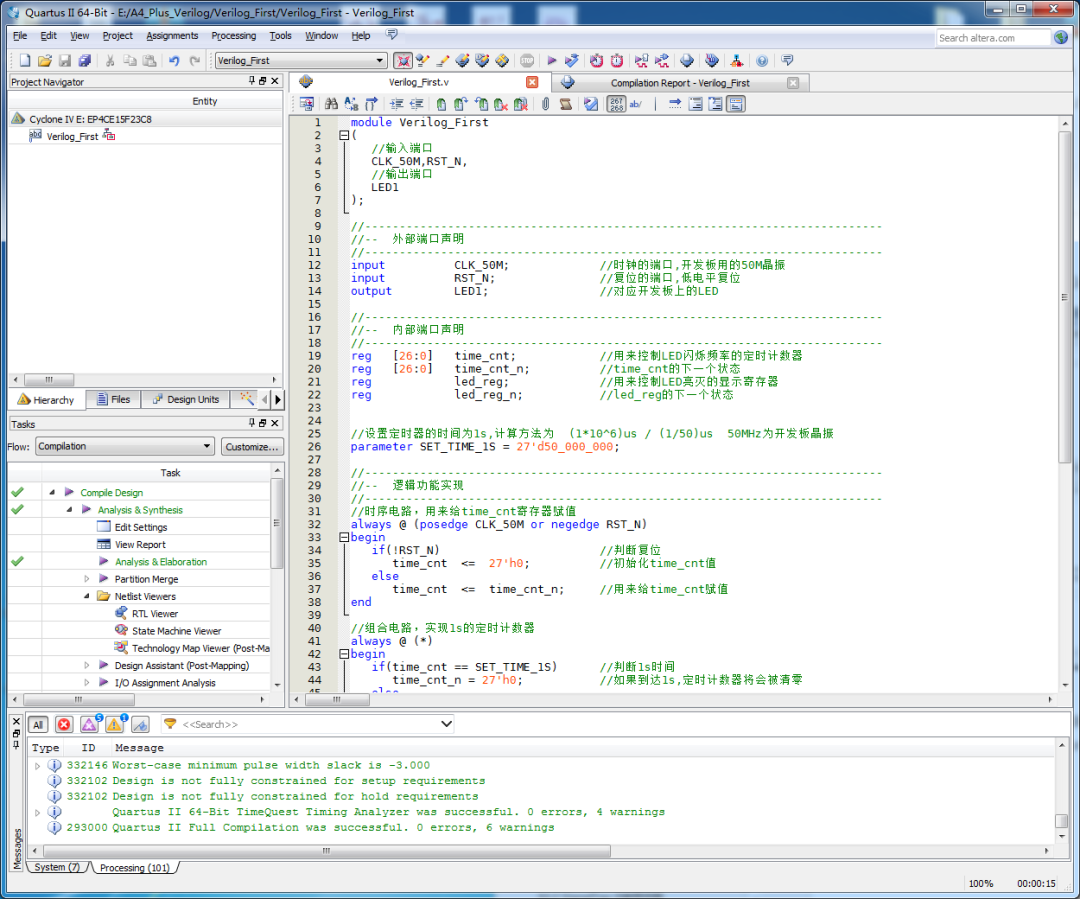

3 ModelSim工程實戰之自動仿真說完了 ModelSim 的使用流程,接下來我們將會對每個流程進行詳細的操作演示,一步步、手把手帶領大家學習使用 ModelSim 軟件。首先我們講解的 ModelSim 自動仿真,所謂自動仿真,其實是在 Quartus II 中調用 ModelSim 軟件來進行仿真,在調用過程中,Quartus II 會幫我們完成 ModelSim 中的所有操作,我們只需要分析最后的仿真結果。下面我們就以上章節中我們創建的 Quartus II 軟件工程為例,進行仿真。3.1 檢查 EDA 路徑首先我們打開之前的 Quartus II 工程,如圖 在該頁面中,我們在菜單欄中找到【Tool】→【Options】按鈕并打開,在打開的頁面左側,我們找到“EDA Tool Options”點擊,如圖

在該頁面中,我們在菜單欄中找到【Tool】→【Options】按鈕并打開,在打開的頁面左側,我們找到“EDA Tool Options”點擊,如圖

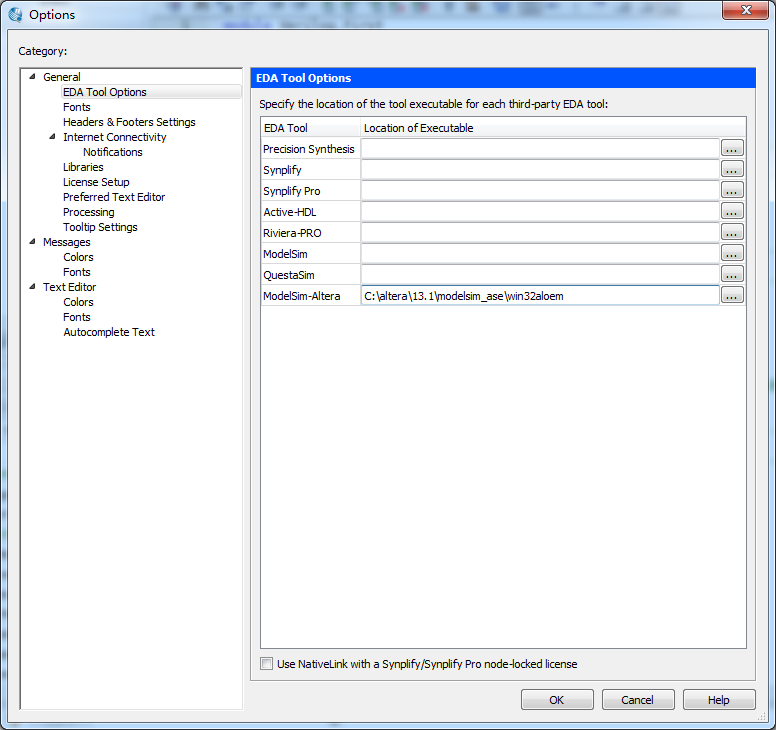

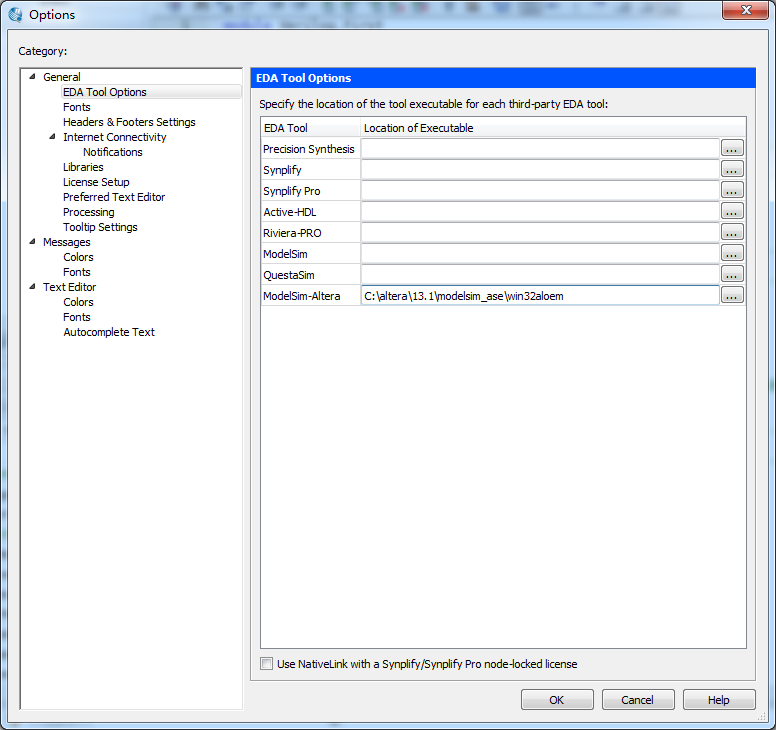

在該頁面中,如果你安裝的是 ModelSim 軟件,那么你需要在 ModelSim 路徑中進行設置,這里我們使用的 ModelSim-Altera , 所 以 我 們 將 ModelSim-Altera 路 徑 設 置 成 了C:altera13.1modelsim_asewin32aloem。這里需要大家注意的是一定要選擇 modelsim_ase文件夾中的 win32aloem,不要選擇 modelsim_ae 文件夾中的 win32aloem。還記得我們前面說的么?ae 是收費版本,我們是不能使用的,這里的 ase 免費版本也是可以滿足我們的設計的。路徑設置完成以后,我們點擊【OK】返回我們的 Quartus II 軟件界面。3.2 選擇 EDA 工具我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Assignments】→【Settings】按鈕并打開,在打開的頁面左側我們找到“EDA Tool Settings”點擊,如圖

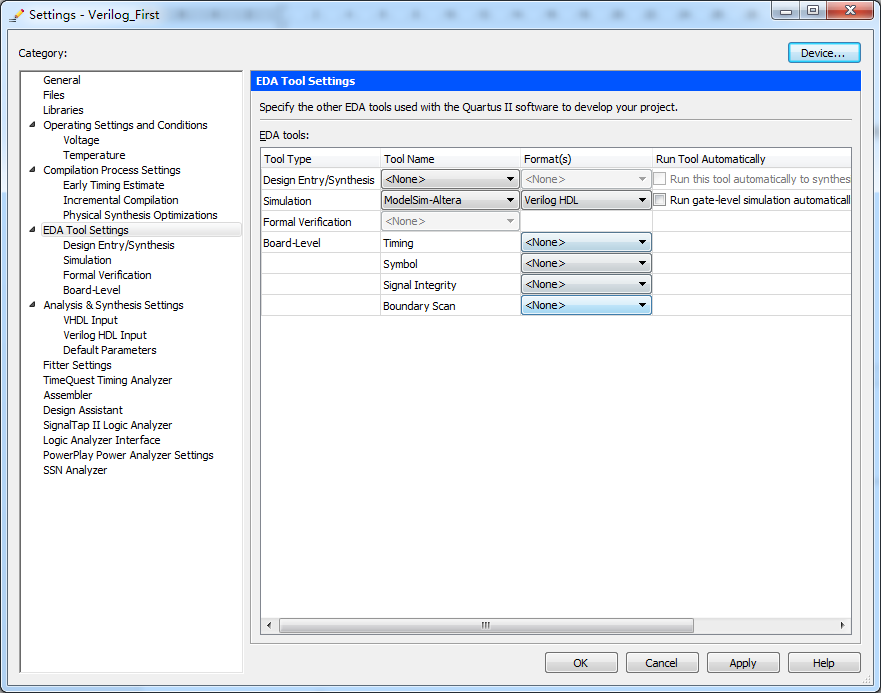

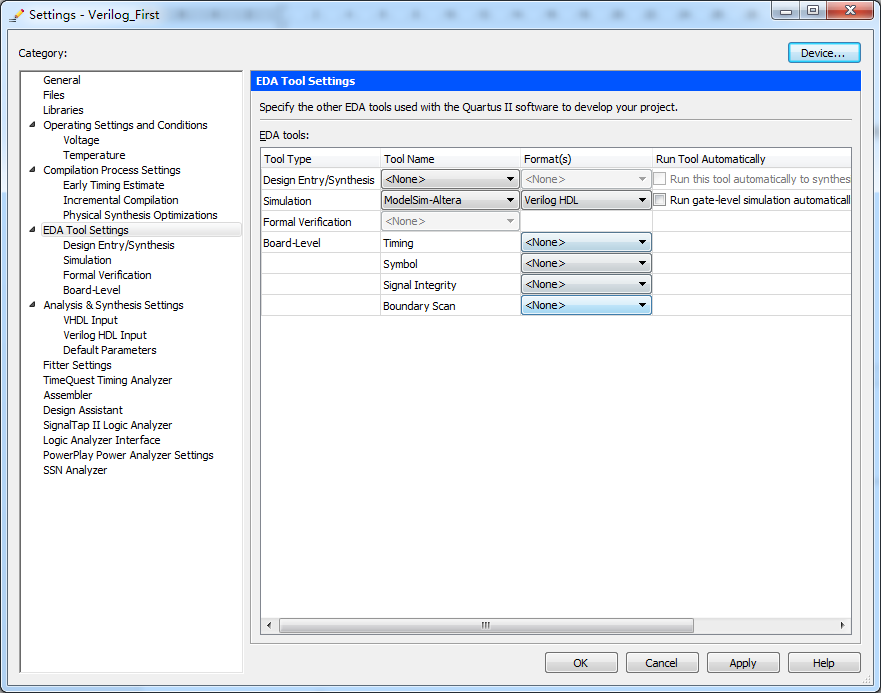

在該頁面中,如果你安裝的是 ModelSim 軟件,那么你需要在 ModelSim 路徑中進行設置,這里我們使用的 ModelSim-Altera , 所 以 我 們 將 ModelSim-Altera 路 徑 設 置 成 了C:altera13.1modelsim_asewin32aloem。這里需要大家注意的是一定要選擇 modelsim_ase文件夾中的 win32aloem,不要選擇 modelsim_ae 文件夾中的 win32aloem。還記得我們前面說的么?ae 是收費版本,我們是不能使用的,這里的 ase 免費版本也是可以滿足我們的設計的。路徑設置完成以后,我們點擊【OK】返回我們的 Quartus II 軟件界面。3.2 選擇 EDA 工具我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Assignments】→【Settings】按鈕并打開,在打開的頁面左側我們找到“EDA Tool Settings”點擊,如圖 還記得我們之前創建工程的時候,由于在 Quartus II 軟件中我們沒有用到仿真,所以我們將這里設置成了“None”,現在我們需要用到仿真工具了,我們需要在這里將 Simulation 設置成“ModelSim-Altera、Verilog HDL”。設置完成之后,我們點擊【OK】返回 Quartus II 軟件頁 面中。3.3 編寫仿真文件我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Processing】→【Start】→【Start TestBench Template Writer】按鈕并點擊,這時 Message 窗口中會顯示,如圖

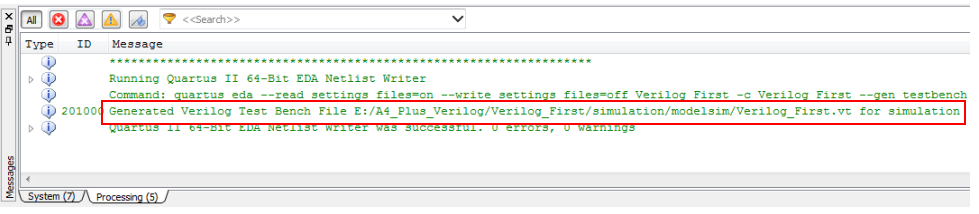

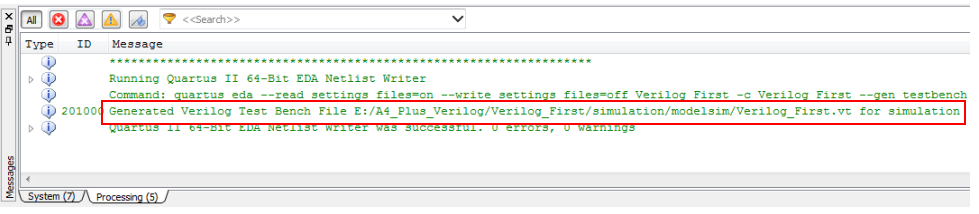

還記得我們之前創建工程的時候,由于在 Quartus II 軟件中我們沒有用到仿真,所以我們將這里設置成了“None”,現在我們需要用到仿真工具了,我們需要在這里將 Simulation 設置成“ModelSim-Altera、Verilog HDL”。設置完成之后,我們點擊【OK】返回 Quartus II 軟件頁 面中。3.3 編寫仿真文件我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Processing】→【Start】→【Start TestBench Template Writer】按鈕并點擊,這時 Message 窗口中會顯示,如圖 我們可以從這條信息中知道,Quartus II 軟件自動給我們生成了一個 TestBench 模板,我們只需要在這個模板上稍作修改就能直接使用了。我們在工程目錄下找到 Verilog_First.vt 文件,我們可以用記事本打開進行修改,也可以使用 Quartus II 軟件打開它進行修改,這里我們建議還在 Quartus II 軟件中進行修改。我們在 Quartus II 軟件的菜單欄中找到【File】→【Open】按鈕并打開,在對話框中找到我們的 Verilog 文件,如圖

我們可以從這條信息中知道,Quartus II 軟件自動給我們生成了一個 TestBench 模板,我們只需要在這個模板上稍作修改就能直接使用了。我們在工程目錄下找到 Verilog_First.vt 文件,我們可以用記事本打開進行修改,也可以使用 Quartus II 軟件打開它進行修改,這里我們建議還在 Quartus II 軟件中進行修改。我們在 Quartus II 軟件的菜單欄中找到【File】→【Open】按鈕并打開,在對話框中找到我們的 Verilog 文件,如圖

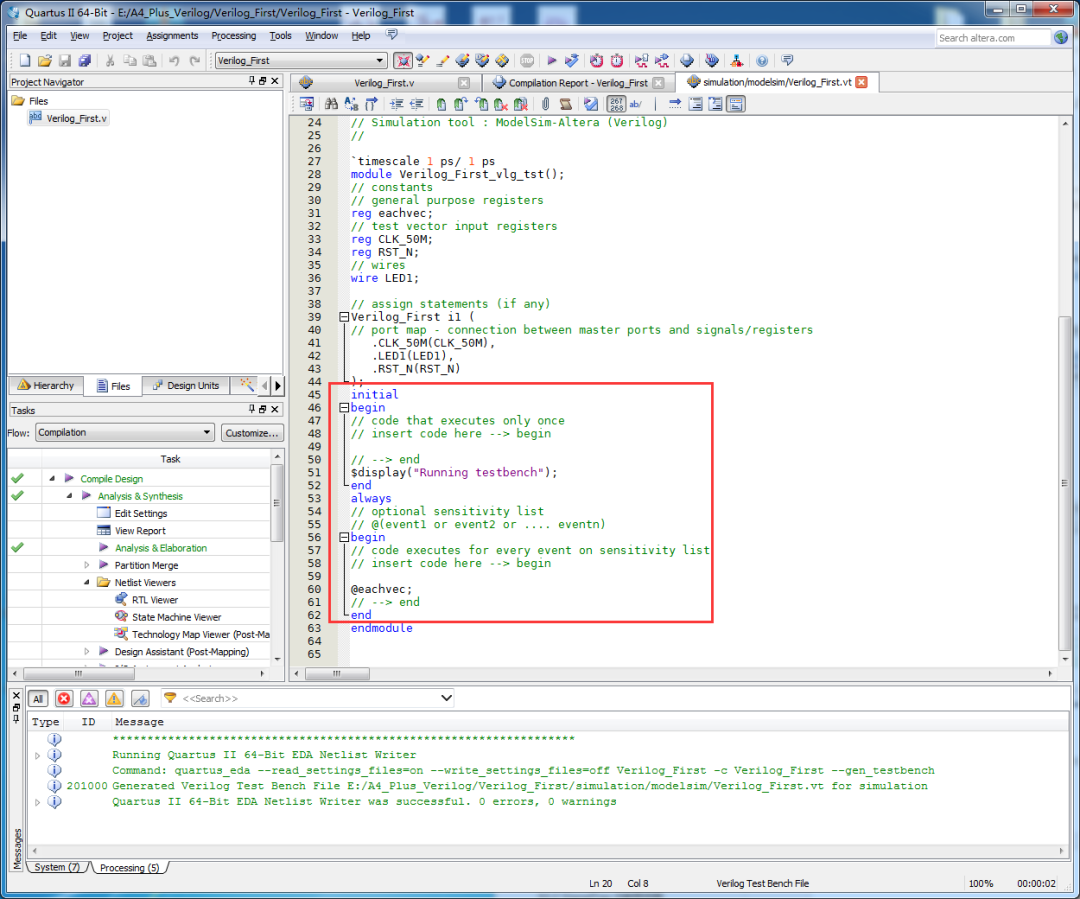

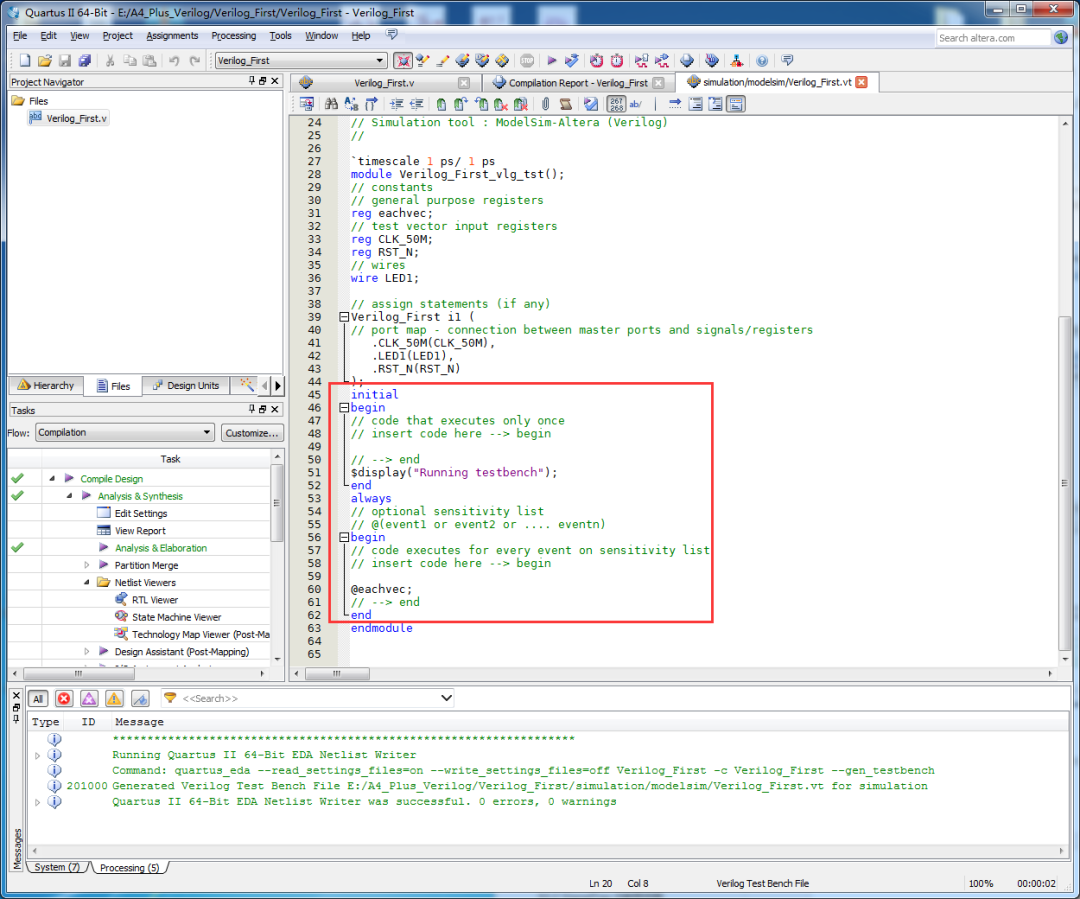

打開之后,如圖

打開之后,如圖 在該圖中我們可以看到,Quartus II 軟件已經為我們完成了一些基本工作,包括端口部分的代碼和接口變量的聲明,我們要做的就是在這個模板里添加我們需要的測試代碼(也就是我們常說的激勵)。為了讓讀者能夠更好的理解仿真,這里我們就簡單介紹一下 TestBench 源代碼:代碼的第 1 行,表示仿真的單位時間為 1ps,精度為 1ps。想要進行仿真首先要規定時間單位,我們建議大家最好在 Testbench 里面統一規定時間單位,不要在工程代碼里定義,因為不同的模塊如果時間單位不同可能會為仿真帶來一些問題,timescale 是 Verilog 語法中的不可綜合語法。代碼的第 2 行就是我們熟悉的部分了,其中第 5 行至第 10 行是我們的數據類型定義,這里我們可以看到 reg eachvec 是一個多余的信號,沒有任何作用,我們也可以將它刪除,接下來我們再來看第 13 行至第 18 行,這一部分就是一個模塊調用,它將我們的 Verilog 模塊中的信號連接到我們的 TestBench 模塊中。最后,我們再來看下第 20 行至第 32 行代碼,其中第 20 行至第 26 行是信號的初始化,第 28 行至第 31 行是時鐘信號的生成。這里我們主要來講講#10000,#10000 表示的是延遲 10000ps(即 10ns),具體的延遲單位,還是要看我們的 timescale 是如何設置的。至此,整個代碼都介紹完了。3.4 配置仿真功能編寫完了仿真文件,接下來我們需要在 Quartus II 軟件中配置仿真功能,我們在 Quartus II軟件界面的菜單欄找到【Assigement】→【Settings】按鈕并打開,在打開的頁面中,我們找到左側的 Simulation 點擊,出現如圖

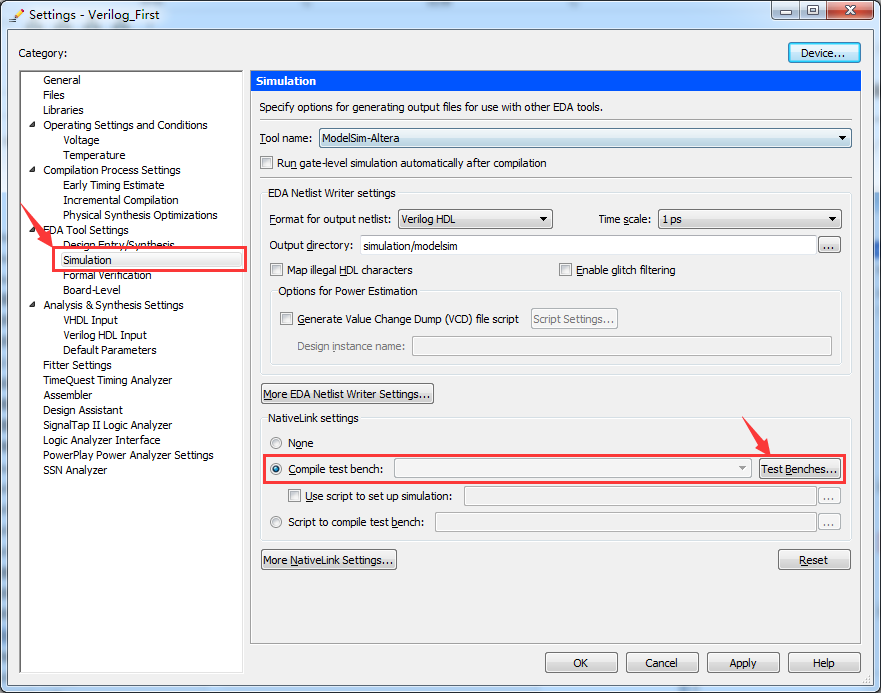

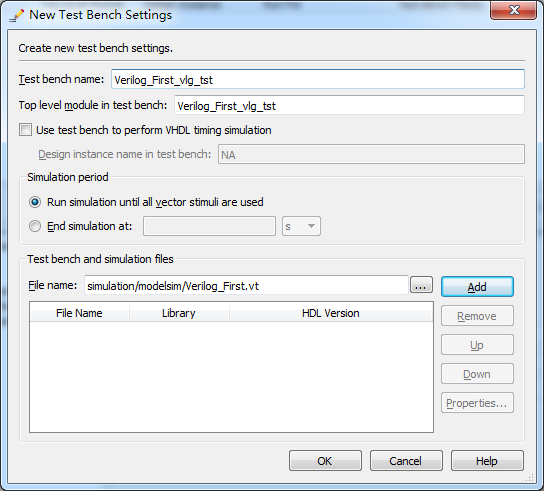

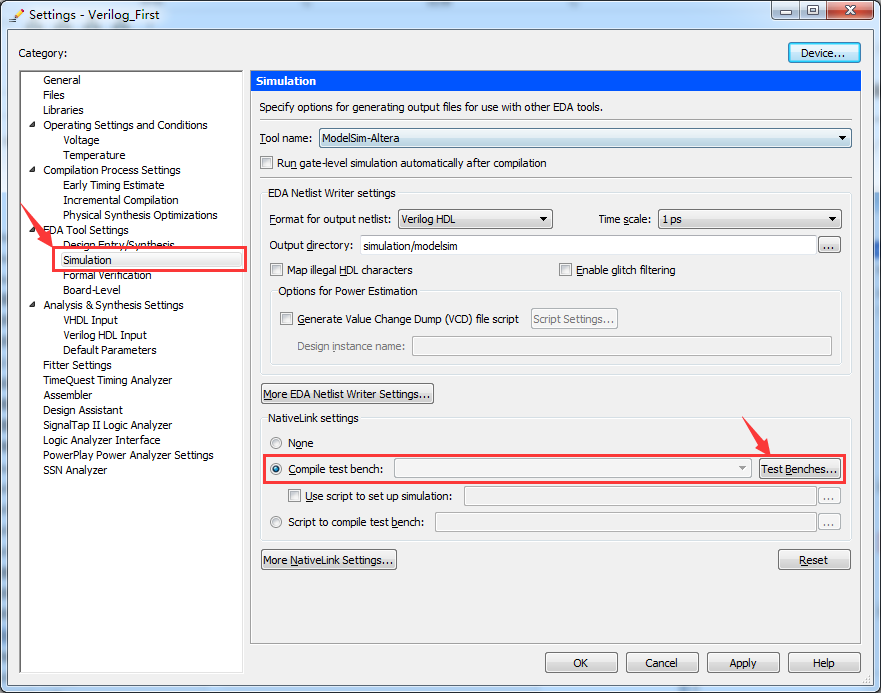

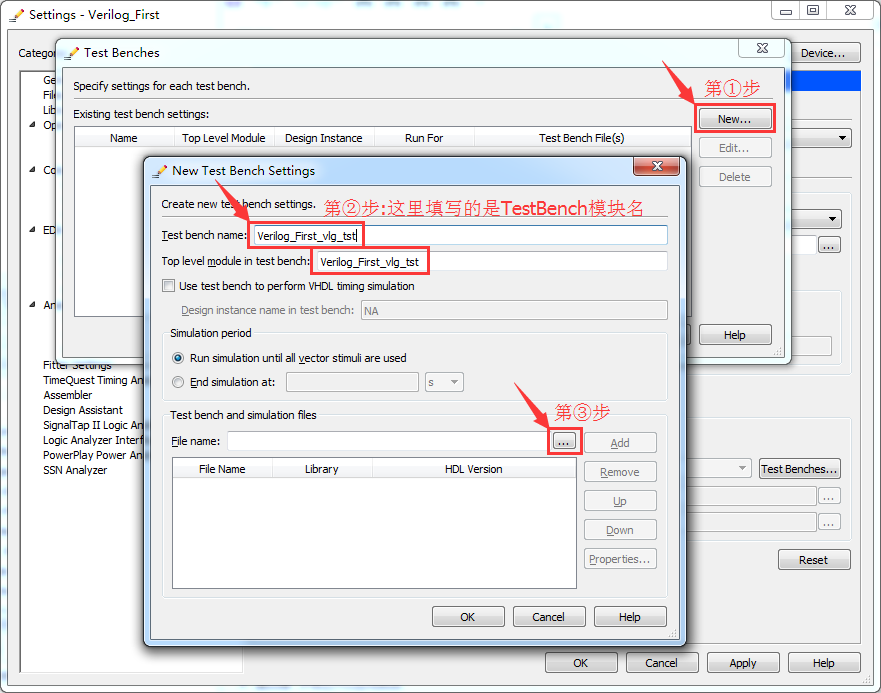

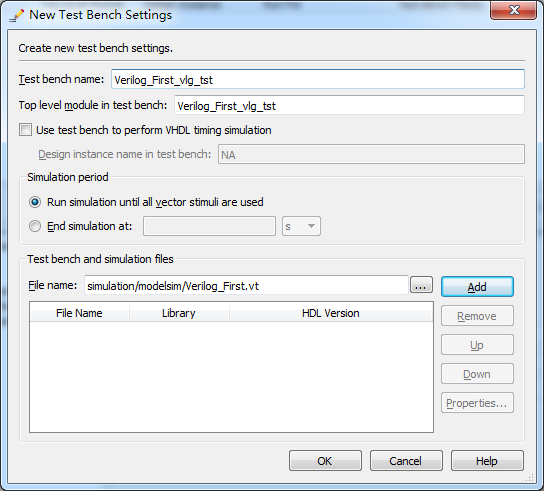

在該圖中我們可以看到,Quartus II 軟件已經為我們完成了一些基本工作,包括端口部分的代碼和接口變量的聲明,我們要做的就是在這個模板里添加我們需要的測試代碼(也就是我們常說的激勵)。為了讓讀者能夠更好的理解仿真,這里我們就簡單介紹一下 TestBench 源代碼:代碼的第 1 行,表示仿真的單位時間為 1ps,精度為 1ps。想要進行仿真首先要規定時間單位,我們建議大家最好在 Testbench 里面統一規定時間單位,不要在工程代碼里定義,因為不同的模塊如果時間單位不同可能會為仿真帶來一些問題,timescale 是 Verilog 語法中的不可綜合語法。代碼的第 2 行就是我們熟悉的部分了,其中第 5 行至第 10 行是我們的數據類型定義,這里我們可以看到 reg eachvec 是一個多余的信號,沒有任何作用,我們也可以將它刪除,接下來我們再來看第 13 行至第 18 行,這一部分就是一個模塊調用,它將我們的 Verilog 模塊中的信號連接到我們的 TestBench 模塊中。最后,我們再來看下第 20 行至第 32 行代碼,其中第 20 行至第 26 行是信號的初始化,第 28 行至第 31 行是時鐘信號的生成。這里我們主要來講講#10000,#10000 表示的是延遲 10000ps(即 10ns),具體的延遲單位,還是要看我們的 timescale 是如何設置的。至此,整個代碼都介紹完了。3.4 配置仿真功能編寫完了仿真文件,接下來我們需要在 Quartus II 軟件中配置仿真功能,我們在 Quartus II軟件界面的菜單欄找到【Assigement】→【Settings】按鈕并打開,在打開的頁面中,我們找到左側的 Simulation 點擊,出現如圖 我們選中“Compile Test bench”,然后單擊后面的【Test Benches】按鈕,則出現如圖 2.9所示的“Test Benches”窗口(也就是圖中上面的窗口),接著我們單擊【New】按鈕,則會出現如圖所示的“New Test Bench Settings”窗口(也就是圖中下面的窗口)。

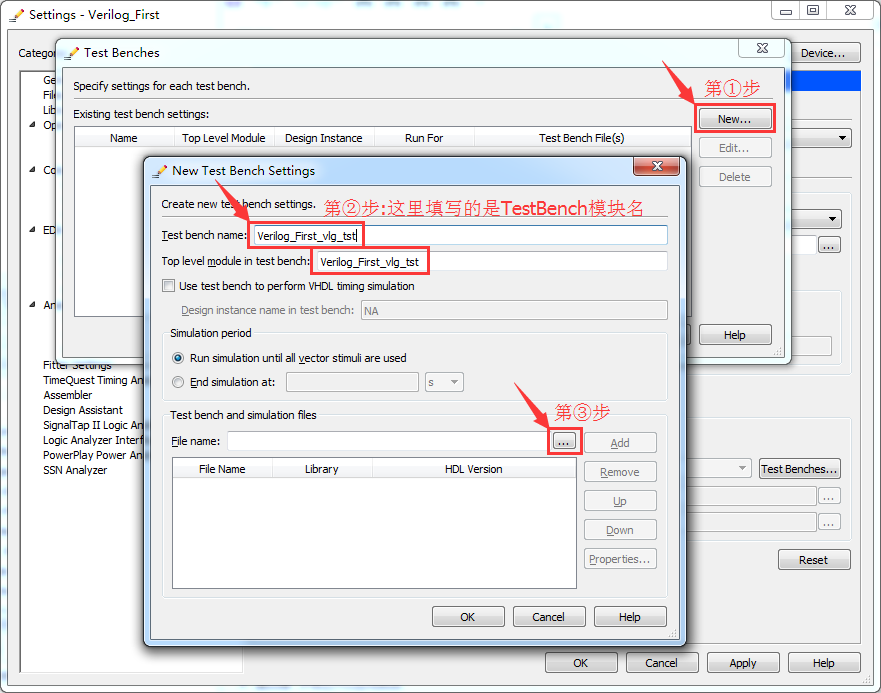

我們選中“Compile Test bench”,然后單擊后面的【Test Benches】按鈕,則出現如圖 2.9所示的“Test Benches”窗口(也就是圖中上面的窗口),接著我們單擊【New】按鈕,則會出現如圖所示的“New Test Bench Settings”窗口(也就是圖中下面的窗口)。 在該頁面中,我們將 TestBench 模塊名輸入到“Test bench name”和 “Top level module in test bench”的編輯欄中。接著我們在“Test bench and simulation files”下拉列表框中添加仿真文件,如圖 所示,點擊【Open】即可。

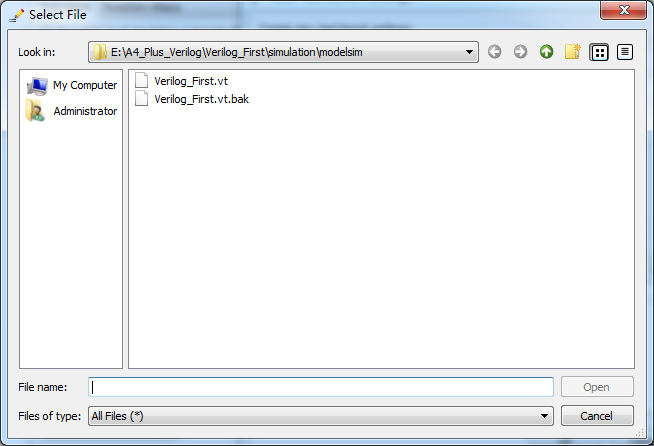

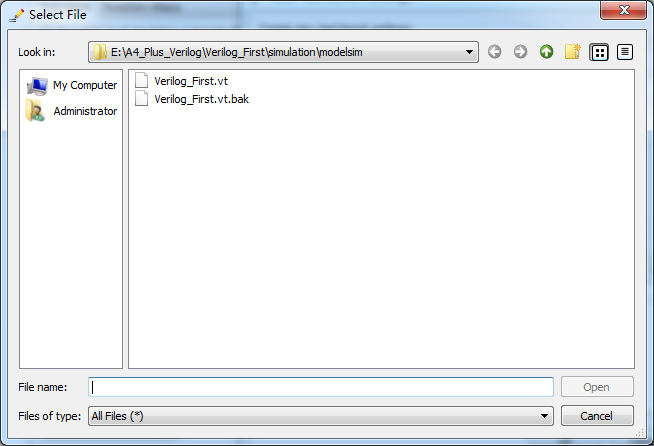

在該頁面中,我們將 TestBench 模塊名輸入到“Test bench name”和 “Top level module in test bench”的編輯欄中。接著我們在“Test bench and simulation files”下拉列表框中添加仿真文件,如圖 所示,點擊【Open】即可。 然后單擊【Add】 按鈕添加到最下面的列表中如圖

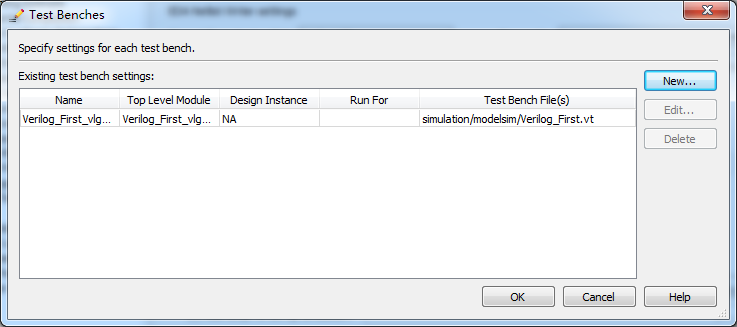

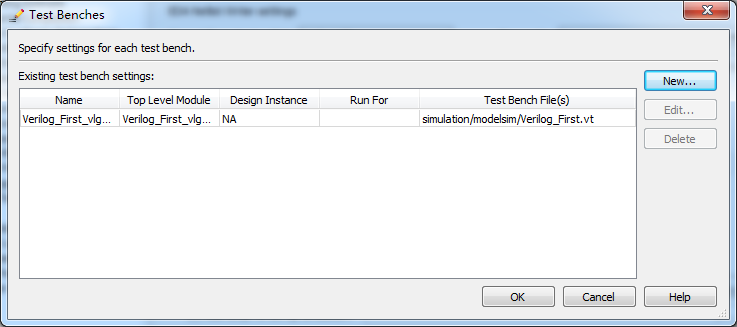

然后單擊【Add】 按鈕添加到最下面的列表中如圖 完成后我們單擊【OK】按鈕,便可看到如圖 2.12 所示的“Test benches”窗口的列表中出現了剛才添加的仿真文件相關信息,至此,我們仿真文件添加完成了,接著我們單擊【OK】按鈕,返回我們的 Quartus II 軟件界面。

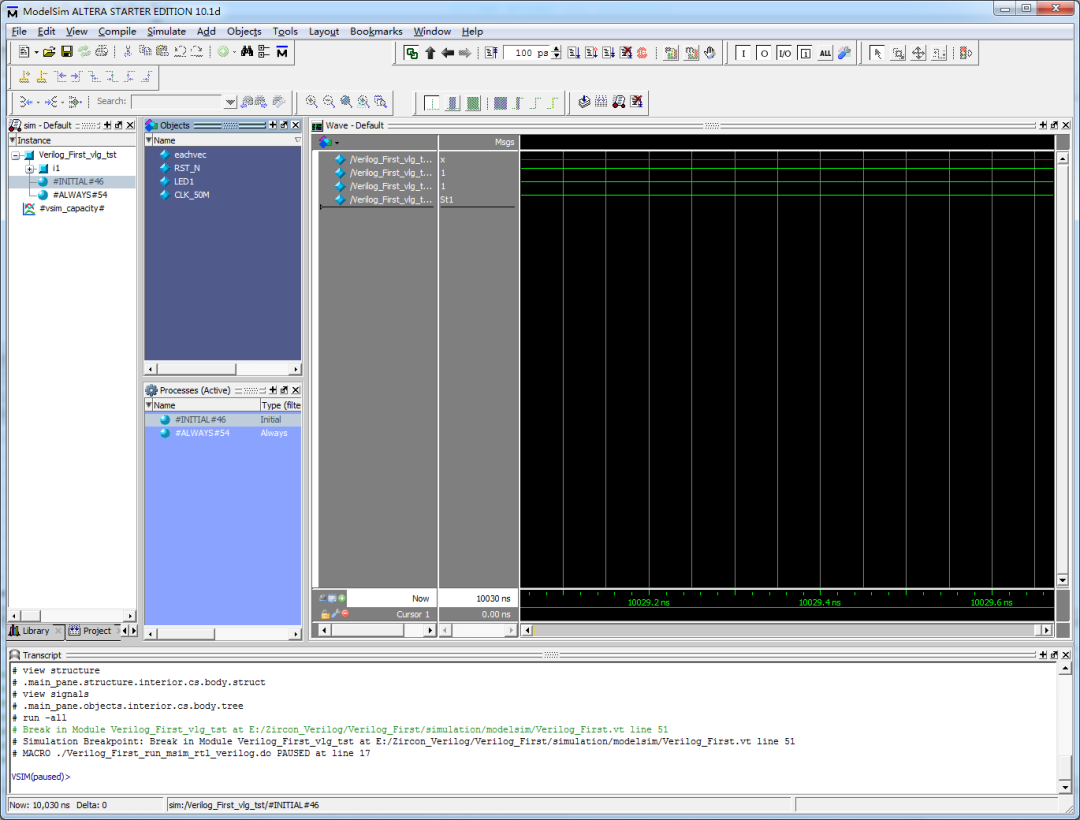

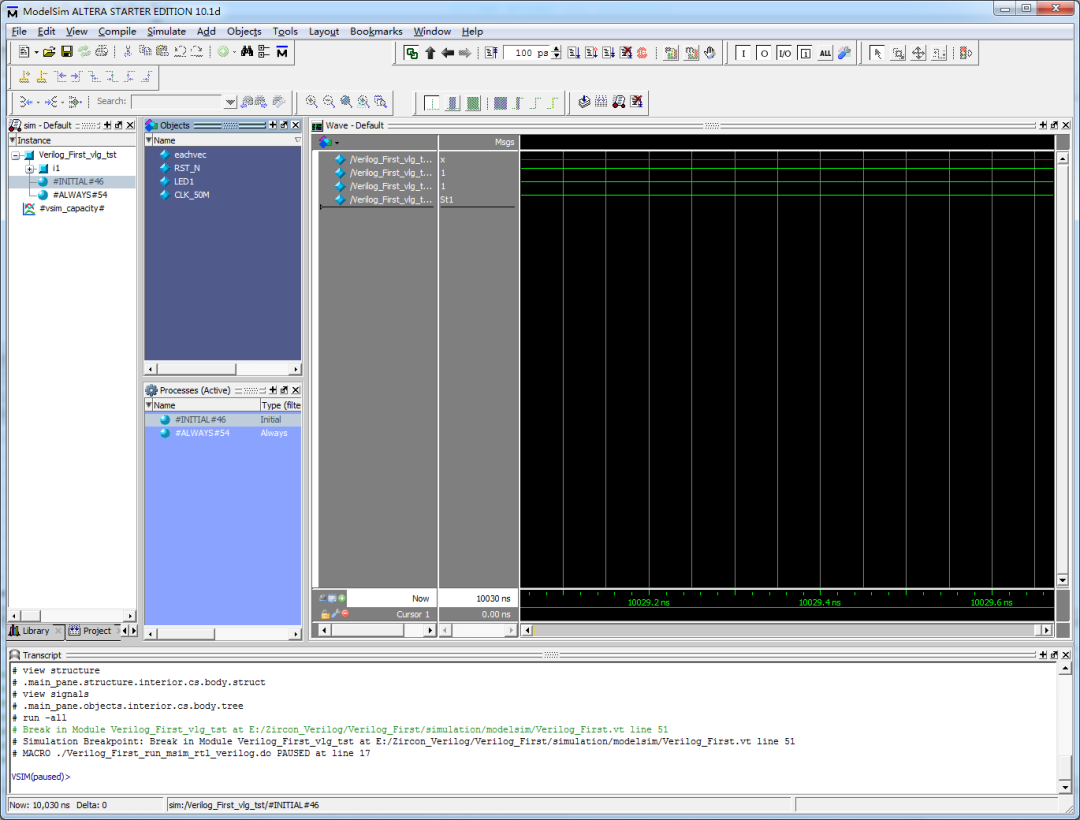

完成后我們單擊【OK】按鈕,便可看到如圖 2.12 所示的“Test benches”窗口的列表中出現了剛才添加的仿真文件相關信息,至此,我們仿真文件添加完成了,接著我們單擊【OK】按鈕,返回我們的 Quartus II 軟件界面。 3.5 開始功能仿真萬事俱備只欠東風,經過上面這么多的操作步驟,我們終于完成了所有設置,接下來我們就可以進行仿真了,在開始仿真之前,我們這里有一點要需要注意,我們在 Quartus II 軟件中實現的功能是 LED 閃爍,它的間隔時間是 1s,如果我們想要仿真這個功能,那么我們仿真軟件運行時間最低就是 1s。這 1s 鐘在我們看來是很短很短的,不過在仿真軟件看來是很長很長的,我們的仿真軟件單位可是 ps。為了便于我們仿真,這里我們需要稍微改動一下 Verilog 代碼,我們需要將 parameter SET_TIME_1S = 27'd50_000_000;修改為 parameter SET_TIME_1S = 27'd50; 也就是將我們原來的 1s 鐘修改成了 1us。修改完畢后,我們在 Quartus II 軟件界面中的菜單欄中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按鈕并點擊,則會出現如圖 2.13 所示界面。

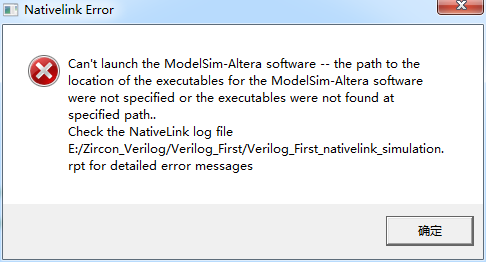

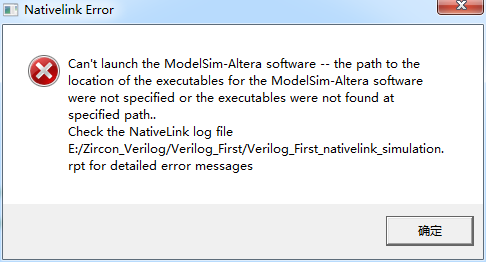

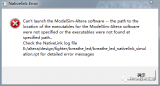

3.5 開始功能仿真萬事俱備只欠東風,經過上面這么多的操作步驟,我們終于完成了所有設置,接下來我們就可以進行仿真了,在開始仿真之前,我們這里有一點要需要注意,我們在 Quartus II 軟件中實現的功能是 LED 閃爍,它的間隔時間是 1s,如果我們想要仿真這個功能,那么我們仿真軟件運行時間最低就是 1s。這 1s 鐘在我們看來是很短很短的,不過在仿真軟件看來是很長很長的,我們的仿真軟件單位可是 ps。為了便于我們仿真,這里我們需要稍微改動一下 Verilog 代碼,我們需要將 parameter SET_TIME_1S = 27'd50_000_000;修改為 parameter SET_TIME_1S = 27'd50; 也就是將我們原來的 1s 鐘修改成了 1us。修改完畢后,我們在 Quartus II 軟件界面中的菜單欄中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按鈕并點擊,則會出現如圖 2.13 所示界面。 看到這里,也許有的朋友點擊【RTL Simulation】并沒有出現 Modelsim 仿真窗口界面,而是出現了如圖 2.14 所示界面。

看到這里,也許有的朋友點擊【RTL Simulation】并沒有出現 Modelsim 仿真窗口界面,而是出現了如圖 2.14 所示界面。 出現這種錯誤主要是因為我們前面設置的 Modelsim 路徑不對造成的,如何解決這個問題呢?我們嘗試將 ModelSim-Altera 路徑設置成了 C:altera13.1modelsim_asewin32aloem。這和我們剛剛設置不同的是,我們在路徑的最后面添加了一個反斜杠。這時,我們再點擊【RTL Simulation】按鈕就會出現 Modelsim 仿真窗口界面了,這里我們需要說明的是:有的電腦不添加反斜杠是可以運行的,有的電腦不添加反斜杠是不能運行。在 Modelsim 軟件啟動過程中,我 們不需要任何操作,它會自動完成仿真,并給出我們所需要的波形,當波形圖出現之后,我們就可以查看波形來判斷設計功能是否正常了。

出現這種錯誤主要是因為我們前面設置的 Modelsim 路徑不對造成的,如何解決這個問題呢?我們嘗試將 ModelSim-Altera 路徑設置成了 C:altera13.1modelsim_asewin32aloem。這和我們剛剛設置不同的是,我們在路徑的最后面添加了一個反斜杠。這時,我們再點擊【RTL Simulation】按鈕就會出現 Modelsim 仿真窗口界面了,這里我們需要說明的是:有的電腦不添加反斜杠是可以運行的,有的電腦不添加反斜杠是不能運行。在 Modelsim 軟件啟動過程中,我 們不需要任何操作,它會自動完成仿真,并給出我們所需要的波形,當波形圖出現之后,我們就可以查看波形來判斷設計功能是否正常了。

在該頁面中,我們在菜單欄中找到【Tool】→【Options】按鈕并打開,在打開的頁面左側,我們找到“EDA Tool Options”點擊,如圖

在該頁面中,我們在菜單欄中找到【Tool】→【Options】按鈕并打開,在打開的頁面左側,我們找到“EDA Tool Options”點擊,如圖

在該頁面中,如果你安裝的是 ModelSim 軟件,那么你需要在 ModelSim 路徑中進行設置,這里我們使用的 ModelSim-Altera , 所 以 我 們 將 ModelSim-Altera 路 徑 設 置 成 了C:altera13.1modelsim_asewin32aloem。這里需要大家注意的是一定要選擇 modelsim_ase文件夾中的 win32aloem,不要選擇 modelsim_ae 文件夾中的 win32aloem。還記得我們前面說的么?ae 是收費版本,我們是不能使用的,這里的 ase 免費版本也是可以滿足我們的設計的。路徑設置完成以后,我們點擊【OK】返回我們的 Quartus II 軟件界面。3.2 選擇 EDA 工具我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Assignments】→【Settings】按鈕并打開,在打開的頁面左側我們找到“EDA Tool Settings”點擊,如圖

在該頁面中,如果你安裝的是 ModelSim 軟件,那么你需要在 ModelSim 路徑中進行設置,這里我們使用的 ModelSim-Altera , 所 以 我 們 將 ModelSim-Altera 路 徑 設 置 成 了C:altera13.1modelsim_asewin32aloem。這里需要大家注意的是一定要選擇 modelsim_ase文件夾中的 win32aloem,不要選擇 modelsim_ae 文件夾中的 win32aloem。還記得我們前面說的么?ae 是收費版本,我們是不能使用的,這里的 ase 免費版本也是可以滿足我們的設計的。路徑設置完成以后,我們點擊【OK】返回我們的 Quartus II 軟件界面。3.2 選擇 EDA 工具我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Assignments】→【Settings】按鈕并打開,在打開的頁面左側我們找到“EDA Tool Settings”點擊,如圖 還記得我們之前創建工程的時候,由于在 Quartus II 軟件中我們沒有用到仿真,所以我們將這里設置成了“None”,現在我們需要用到仿真工具了,我們需要在這里將 Simulation 設置成“ModelSim-Altera、Verilog HDL”。設置完成之后,我們點擊【OK】返回 Quartus II 軟件頁 面中。3.3 編寫仿真文件我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Processing】→【Start】→【Start TestBench Template Writer】按鈕并點擊,這時 Message 窗口中會顯示,如圖

還記得我們之前創建工程的時候,由于在 Quartus II 軟件中我們沒有用到仿真,所以我們將這里設置成了“None”,現在我們需要用到仿真工具了,我們需要在這里將 Simulation 設置成“ModelSim-Altera、Verilog HDL”。設置完成之后,我們點擊【OK】返回 Quartus II 軟件頁 面中。3.3 編寫仿真文件我們在 Quartus II 軟件頁面的菜單欄中,我們找到【Processing】→【Start】→【Start TestBench Template Writer】按鈕并點擊,這時 Message 窗口中會顯示,如圖 我們可以從這條信息中知道,Quartus II 軟件自動給我們生成了一個 TestBench 模板,我們只需要在這個模板上稍作修改就能直接使用了。我們在工程目錄下找到 Verilog_First.vt 文件,我們可以用記事本打開進行修改,也可以使用 Quartus II 軟件打開它進行修改,這里我們建議還在 Quartus II 軟件中進行修改。我們在 Quartus II 軟件的菜單欄中找到【File】→【Open】按鈕并打開,在對話框中找到我們的 Verilog 文件,如圖

我們可以從這條信息中知道,Quartus II 軟件自動給我們生成了一個 TestBench 模板,我們只需要在這個模板上稍作修改就能直接使用了。我們在工程目錄下找到 Verilog_First.vt 文件,我們可以用記事本打開進行修改,也可以使用 Quartus II 軟件打開它進行修改,這里我們建議還在 Quartus II 軟件中進行修改。我們在 Quartus II 軟件的菜單欄中找到【File】→【Open】按鈕并打開,在對話框中找到我們的 Verilog 文件,如圖

打開之后,如圖

打開之后,如圖 在該圖中我們可以看到,Quartus II 軟件已經為我們完成了一些基本工作,包括端口部分的代碼和接口變量的聲明,我們要做的就是在這個模板里添加我們需要的測試代碼(也就是我們常說的激勵)。為了讓讀者能夠更好的理解仿真,這里我們就簡單介紹一下 TestBench 源代碼:代碼的第 1 行,表示仿真的單位時間為 1ps,精度為 1ps。想要進行仿真首先要規定時間單位,我們建議大家最好在 Testbench 里面統一規定時間單位,不要在工程代碼里定義,因為不同的模塊如果時間單位不同可能會為仿真帶來一些問題,timescale 是 Verilog 語法中的不可綜合語法。代碼的第 2 行就是我們熟悉的部分了,其中第 5 行至第 10 行是我們的數據類型定義,這里我們可以看到 reg eachvec 是一個多余的信號,沒有任何作用,我們也可以將它刪除,接下來我們再來看第 13 行至第 18 行,這一部分就是一個模塊調用,它將我們的 Verilog 模塊中的信號連接到我們的 TestBench 模塊中。最后,我們再來看下第 20 行至第 32 行代碼,其中第 20 行至第 26 行是信號的初始化,第 28 行至第 31 行是時鐘信號的生成。這里我們主要來講講#10000,#10000 表示的是延遲 10000ps(即 10ns),具體的延遲單位,還是要看我們的 timescale 是如何設置的。至此,整個代碼都介紹完了。3.4 配置仿真功能編寫完了仿真文件,接下來我們需要在 Quartus II 軟件中配置仿真功能,我們在 Quartus II軟件界面的菜單欄找到【Assigement】→【Settings】按鈕并打開,在打開的頁面中,我們找到左側的 Simulation 點擊,出現如圖

在該圖中我們可以看到,Quartus II 軟件已經為我們完成了一些基本工作,包括端口部分的代碼和接口變量的聲明,我們要做的就是在這個模板里添加我們需要的測試代碼(也就是我們常說的激勵)。為了讓讀者能夠更好的理解仿真,這里我們就簡單介紹一下 TestBench 源代碼:代碼的第 1 行,表示仿真的單位時間為 1ps,精度為 1ps。想要進行仿真首先要規定時間單位,我們建議大家最好在 Testbench 里面統一規定時間單位,不要在工程代碼里定義,因為不同的模塊如果時間單位不同可能會為仿真帶來一些問題,timescale 是 Verilog 語法中的不可綜合語法。代碼的第 2 行就是我們熟悉的部分了,其中第 5 行至第 10 行是我們的數據類型定義,這里我們可以看到 reg eachvec 是一個多余的信號,沒有任何作用,我們也可以將它刪除,接下來我們再來看第 13 行至第 18 行,這一部分就是一個模塊調用,它將我們的 Verilog 模塊中的信號連接到我們的 TestBench 模塊中。最后,我們再來看下第 20 行至第 32 行代碼,其中第 20 行至第 26 行是信號的初始化,第 28 行至第 31 行是時鐘信號的生成。這里我們主要來講講#10000,#10000 表示的是延遲 10000ps(即 10ns),具體的延遲單位,還是要看我們的 timescale 是如何設置的。至此,整個代碼都介紹完了。3.4 配置仿真功能編寫完了仿真文件,接下來我們需要在 Quartus II 軟件中配置仿真功能,我們在 Quartus II軟件界面的菜單欄找到【Assigement】→【Settings】按鈕并打開,在打開的頁面中,我們找到左側的 Simulation 點擊,出現如圖 我們選中“Compile Test bench”,然后單擊后面的【Test Benches】按鈕,則出現如圖 2.9所示的“Test Benches”窗口(也就是圖中上面的窗口),接著我們單擊【New】按鈕,則會出現如圖所示的“New Test Bench Settings”窗口(也就是圖中下面的窗口)。

我們選中“Compile Test bench”,然后單擊后面的【Test Benches】按鈕,則出現如圖 2.9所示的“Test Benches”窗口(也就是圖中上面的窗口),接著我們單擊【New】按鈕,則會出現如圖所示的“New Test Bench Settings”窗口(也就是圖中下面的窗口)。 在該頁面中,我們將 TestBench 模塊名輸入到“Test bench name”和 “Top level module in test bench”的編輯欄中。接著我們在“Test bench and simulation files”下拉列表框中添加仿真文件,如圖 所示,點擊【Open】即可。

在該頁面中,我們將 TestBench 模塊名輸入到“Test bench name”和 “Top level module in test bench”的編輯欄中。接著我們在“Test bench and simulation files”下拉列表框中添加仿真文件,如圖 所示,點擊【Open】即可。 然后單擊【Add】 按鈕添加到最下面的列表中如圖

然后單擊【Add】 按鈕添加到最下面的列表中如圖 完成后我們單擊【OK】按鈕,便可看到如圖 2.12 所示的“Test benches”窗口的列表中出現了剛才添加的仿真文件相關信息,至此,我們仿真文件添加完成了,接著我們單擊【OK】按鈕,返回我們的 Quartus II 軟件界面。

完成后我們單擊【OK】按鈕,便可看到如圖 2.12 所示的“Test benches”窗口的列表中出現了剛才添加的仿真文件相關信息,至此,我們仿真文件添加完成了,接著我們單擊【OK】按鈕,返回我們的 Quartus II 軟件界面。 3.5 開始功能仿真萬事俱備只欠東風,經過上面這么多的操作步驟,我們終于完成了所有設置,接下來我們就可以進行仿真了,在開始仿真之前,我們這里有一點要需要注意,我們在 Quartus II 軟件中實現的功能是 LED 閃爍,它的間隔時間是 1s,如果我們想要仿真這個功能,那么我們仿真軟件運行時間最低就是 1s。這 1s 鐘在我們看來是很短很短的,不過在仿真軟件看來是很長很長的,我們的仿真軟件單位可是 ps。為了便于我們仿真,這里我們需要稍微改動一下 Verilog 代碼,我們需要將 parameter SET_TIME_1S = 27'd50_000_000;修改為 parameter SET_TIME_1S = 27'd50; 也就是將我們原來的 1s 鐘修改成了 1us。修改完畢后,我們在 Quartus II 軟件界面中的菜單欄中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按鈕并點擊,則會出現如圖 2.13 所示界面。

3.5 開始功能仿真萬事俱備只欠東風,經過上面這么多的操作步驟,我們終于完成了所有設置,接下來我們就可以進行仿真了,在開始仿真之前,我們這里有一點要需要注意,我們在 Quartus II 軟件中實現的功能是 LED 閃爍,它的間隔時間是 1s,如果我們想要仿真這個功能,那么我們仿真軟件運行時間最低就是 1s。這 1s 鐘在我們看來是很短很短的,不過在仿真軟件看來是很長很長的,我們的仿真軟件單位可是 ps。為了便于我們仿真,這里我們需要稍微改動一下 Verilog 代碼,我們需要將 parameter SET_TIME_1S = 27'd50_000_000;修改為 parameter SET_TIME_1S = 27'd50; 也就是將我們原來的 1s 鐘修改成了 1us。修改完畢后,我們在 Quartus II 軟件界面中的菜單欄中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按鈕并點擊,則會出現如圖 2.13 所示界面。 看到這里,也許有的朋友點擊【RTL Simulation】并沒有出現 Modelsim 仿真窗口界面,而是出現了如圖 2.14 所示界面。

看到這里,也許有的朋友點擊【RTL Simulation】并沒有出現 Modelsim 仿真窗口界面,而是出現了如圖 2.14 所示界面。 出現這種錯誤主要是因為我們前面設置的 Modelsim 路徑不對造成的,如何解決這個問題呢?我們嘗試將 ModelSim-Altera 路徑設置成了 C:altera13.1modelsim_asewin32aloem。這和我們剛剛設置不同的是,我們在路徑的最后面添加了一個反斜杠。這時,我們再點擊【RTL Simulation】按鈕就會出現 Modelsim 仿真窗口界面了,這里我們需要說明的是:有的電腦不添加反斜杠是可以運行的,有的電腦不添加反斜杠是不能運行。在 Modelsim 軟件啟動過程中,我 們不需要任何操作,它會自動完成仿真,并給出我們所需要的波形,當波形圖出現之后,我們就可以查看波形來判斷設計功能是否正常了。

出現這種錯誤主要是因為我們前面設置的 Modelsim 路徑不對造成的,如何解決這個問題呢?我們嘗試將 ModelSim-Altera 路徑設置成了 C:altera13.1modelsim_asewin32aloem。這和我們剛剛設置不同的是,我們在路徑的最后面添加了一個反斜杠。這時,我們再點擊【RTL Simulation】按鈕就會出現 Modelsim 仿真窗口界面了,這里我們需要說明的是:有的電腦不添加反斜杠是可以運行的,有的電腦不添加反斜杠是不能運行。在 Modelsim 軟件啟動過程中,我 們不需要任何操作,它會自動完成仿真,并給出我們所需要的波形,當波形圖出現之后,我們就可以查看波形來判斷設計功能是否正常了。

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

仿真

+關注

關注

50文章

4048瀏覽量

133431 -

eda

+關注

關注

71文章

2712瀏覽量

172938 -

ModelSim

+關注

關注

5文章

174瀏覽量

47126 -

Quarus

+關注

關注

0文章

4瀏覽量

6400

原文標題:ModelSim 使用【二】聯合Quarus自動仿真

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

智駕仿真測試實戰之自動泊車HiL仿真測試

汽車進入智能化時代,自動泊車功能已成為標配。在研發測試階段,實車測試面臨測試場景覆蓋度不足、效率低下和成本高昂等挑戰。為解決這些問題,本文提出一種自動泊車HiL仿真測試系統方案,可大幅度提升測試效率

如何在ModelSim中添加Xilinx仿真庫

今天給大俠帶來在FPGA設計應用中如何在ModelSim中添加Xilinx仿真庫,話不多說,上貨。

注意:ModelSim一定要安裝在不帶空格的目錄下,即不要安裝在“Program

發表于 07-03 18:16

FPGA入門必備:Testbench仿真文件編寫實例詳解

在編寫完HDL代碼后,往往需要通過仿真軟件Modelsim或者Vivadao自帶的仿真功能對HDL代碼功能進行驗證,此時我們需要編寫Testbench文件對HDL功能進行測試驗證。

發表于 04-29 10:43

?1849次閱讀

ISE 關聯 Modelsim 詳細操作

在兩者之間即可,然后保存。

第三步,打開ISE,在菜單Edit-Preferences…,調出設置窗口。

設置好之后就到了最后一步,在新建工程時,選擇對應的modelsim即可,在看仿真時正常打開就行了。

發表于 03-22 18:55

最實用的Modelsim使用教程

Quartus II建立工程時,設置 modelsim 作為仿真軟件,或者是在Assignments——>EDA Tool Settings進行設置。

三、 Modelsim

發表于 03-19 16:40

fpga仿真文件怎么寫

首先,你需要選擇一個FPGA仿真軟件,如ModelSim、Vivado、Quartus II等。這些軟件都提供了強大的仿真功能,可以幫助你驗證FPGA設計的正確性。

最實用的Modelsim使用及仿真的基本步驟

后仿真也稱為時序仿真或者布局布線后仿真,是指電路已經映射到特定的工藝環境以后,綜合考慮電路的路徑延遲與門延遲的影響,驗證電路能否在一定時序條件下滿足設計構想的過程,是否存在時序違規。

【基于Lattice MXO2的小腳丫FPGA核心板】02ModelSim仿真

的界面點擊Finish后,會自動進入ModelSim軟件中進行模塊仿真。在仿真界面中,可以將模塊的輸入輸出添加到監視界面,便于進行模塊的程序邏輯分析。

設定

發表于 02-29 08:25

如何使用 ModelSim 進行設計仿真

ModelSim為HDL仿真工具,我們可以利用該軟件來實現對所設計的VHDL或Verilog程 序進行仿真,支持IEEE常見的各種硬件描述語言標準。可以進行兩種語言的混合仿真,但 推薦

發表于 01-14 09:47

?0次下載

modelsim安裝運行patch閃退

模擬器的安裝和運行是計算機科學中非常重要的一環。ModelSim是一種流行的數字電子設計自動化工具,用于驗證和仿真硬件設計。然而,有時安裝和運行Patch可能會導致閃退問題。本文將詳細解釋如何安裝

低功耗仿真實戰

將MVSIM_NATIVE_DEMO文件夾拷貝出來,如下所示,LP、LP_DVE、LP_LPA文件夾分別存放的是仿真環境,REF文件夾是不帶UPF的參考對比仿真環境,RTL和UPF文件夾分別用來存放設計代碼和UPF文件。

ModelSim工程實戰之自動仿真

ModelSim工程實戰之自動仿真

評論