Cadence Integrity 3D-IC 平臺是業界首個全面的整體 3D-IC 設計規劃、實現和分析平臺,以全系統的視角,對芯片的性能、功耗和面積 (PPA) 進行系統驅動的優化,并對 3D-IC 應用的中介層、封裝和印刷電路板進行協同設計。

近幾年,隨著摩爾定律的失效,集成電路的設計發展逐漸從傳統的二維平面轉向立體,人們獲得了三維帶來的諸多優勢,比如:更短的引線、更低的功耗、更高的性能和帶寬、更小的封裝尺寸、以及更好的良率,但同時三維設計也帶來了新的挑戰:例如設計的聚合與管理、額外的系統級驗證等。

過去行業中的解決方案多借助于點工具搭建的流程,裸片和裸片、裸片和封裝之間的設計缺少聯系,無法進行早期的探索和獲得反饋。為了使集成后的系統仍能滿足設計要求,必須過度設計以留下余量,造成性能受限并且成本高昂。

Cadence 在 2021 年推出的 Integrity? 3D-IC 平臺,正是為了應對這些挑戰而設計。

Cadence Integrity? 3D-IC 平臺集成了 3D 設計規劃與物理實現,能夠支持系統級的早期和簽核分析,全面完整地助力設計者實現由系統來驅動的 PPA 目標。

3D-IC的流程包括從系統級規劃,到單個芯片物理實現,再到系統級分析和驗證。

今天我們主要介紹:

Cadence Integrity? 3D-IC 系統級規劃

1.系統級規劃和優化

2.系統連接性檢查

3.Integrity 3D-IC 與系統分析工具的融合

1. 系統級規劃和優化

芯片的堆疊

Feedthrough 的插入

Bump 的規劃與優化

3D 圖形界面

在傳統的 3D-IC 設計當中,系統級規劃通常是通過人工規劃來實現的。這使得系統級的更新需要比較長的迭代周期。Integrity 3D-IC 系統級規劃工具可自動高效地實現芯片的堆疊、feedthrough 的插入、Bump 的規劃和優化等功能。工具可以實時顯示每個操作的結果,讓用戶對于設計的結果一目了然。

與此同時,TCL 命令的引入讓用戶可以像使用數字后端工具一樣,通過腳本來進行系統設計和定制自動化流程。這也是 Integrity 3D-IC 平臺最為突出的特點之一。

芯片的堆疊:

在 Integrity 3D-IC 當中,用戶可以在圖形界面上或者 TCL 命令輕松地更改芯片的擺布和堆疊。Integrity 3D-IC 支持所有的堆疊方式,包括 Face-to-Face, Face-to-Back, Back-to-Back 和 Back-to-Face。堆疊方式更新的結果也能夠實時顯示在圖形界面上。

Feedthrough 的插入:

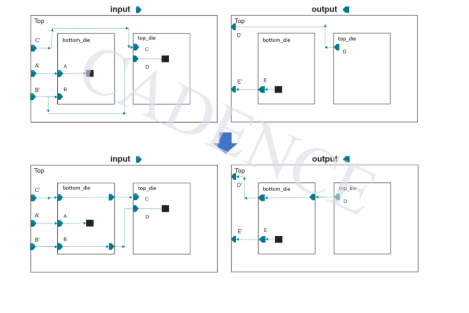

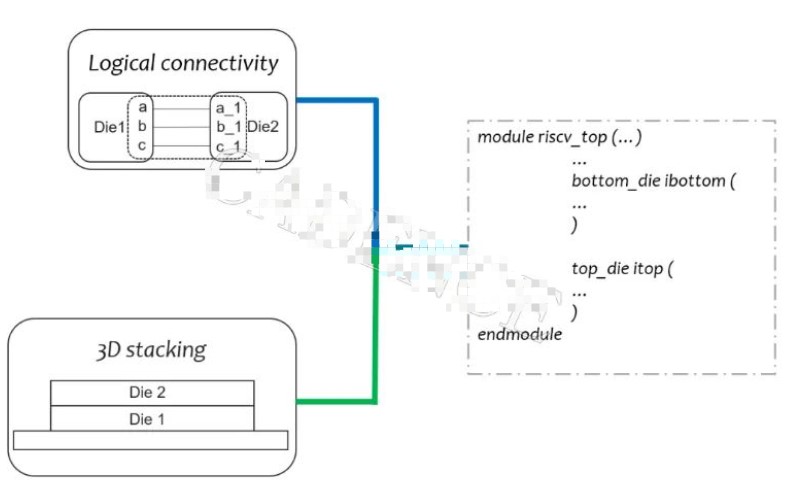

系統的輸入輸出通常存在于封裝上,上層芯片輸入輸出信號有時候需要穿過下層芯片,而并不與下層芯片發生數據交換,這樣的路徑我們稱為 feedthrough。比如在下圖所示的系統中,bottom_die 當中的路徑A起到了連接 top_die 和封裝 PKG 的作用。這樣的路徑就是 feedthrough :

然而,feedthrough 路徑可能并沒有被插入到下層芯片的邏輯網表當中。比如上圖所示路徑A,就可能直接由 PKG 的端口連接到 top_die 的端口。Integrity 3D-IC 提供了自動插入 feedthrough 的功能。

在下圖當中,我們列出了一些比較常見的 feedthrough 的插入:

Bump 的規劃與優化:

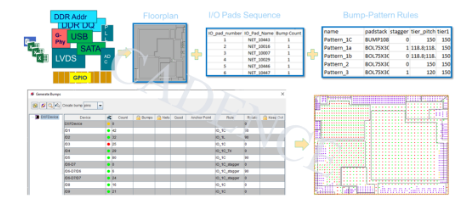

Bump 的規劃和芯片當中的功能模塊密切相關。如果 Bump 距離功能模塊的輸入輸出太遠,會對時序產生不好的影響。Integrity 3D-IC 可以快速地完成基于芯片功能模塊的 Bump 規劃。用戶可以分區域指定 Bump pattern(包括Bump cell,Bump pitch,stagger等),從而可以對不同的 power domain 或 IP block 區域創建不同的 Bump,如下圖所示:

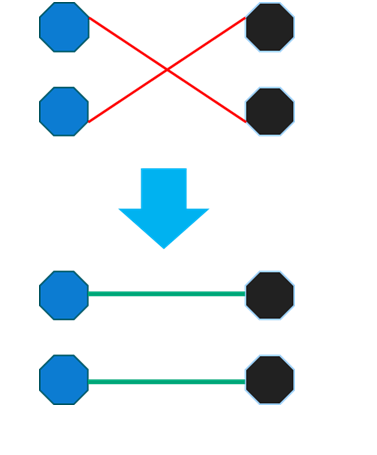

Bump 規劃完成之后,需要檢查 Bump 之間的連接關系有沒有交叉的部分。如果發生交叉,對后續的 Bump 繞線有比較大的影響。我們最好能夠在系統級規劃的階段解決交叉的問題,避免繞線完成之后再進行迭代。

Integrity 3D-IC 提供了一種自動解決連接交叉的方案:

將比較關鍵的 Bump 端固定,對另一端進行自動優化。經過優化,達到 Bump 連接交叉比較少的狀態,從而讓后續 Bump 繞線變得更加容易。

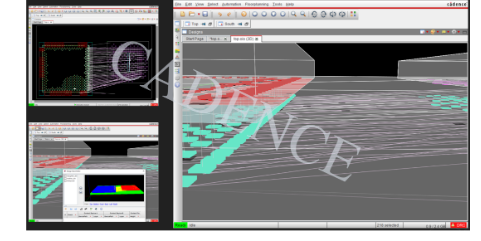

3D圖形界面:

芯片設計進入三維之后,連接關系也從平面走向立體。Integrity 3D-IC 推出了三維圖形界面,讓 3D-IC 設計更加直觀具體。

2. 系統連接性檢查

芯片間接口連接性實時自動檢查

系統連接關系圖

在 3D-IC 設計中,芯片間接口連接性是非常關鍵的,會直接影響最后的 LVS 核簽。Integrity 3D-IC 提供了自動檢查和手動檢查兩種方式。

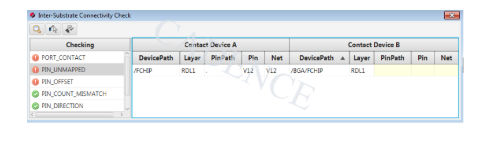

芯片間接口連接性實時自動檢查:

Integrity 3D-IC 提供了實時自動檢查的功能,用來檢查做完 Bump 規劃和優化之后,Bump 的物理連接關系是不是和邏輯連接關系一致。這個檢查是實時的,不需要通過LVS簽核工具來進行迭代。

如果有懸空的 Bump、Bump offset、不正確的 Bump 物理連接等問題都會被報出來。用戶可以在早期解決這些問題,從而避免在物理實現做完之后才通過 LVS 核簽工具發現這些問題,增加迭代的周期。這個檢查有一點類似于 Innovus 當中的 connectivity check。

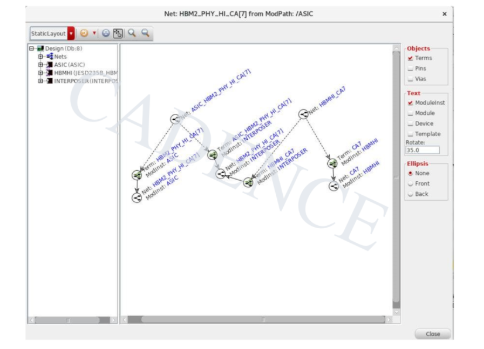

系統連接關系圖:

在系統連接性檢查當中,用戶如果想對某一條路徑的連接性進行 debug,可以使用 Integrity 3D-IC 的系統連接關系圖。這個圖可以將特定路徑的全部系統連接關系顯示出來。用戶可以基于結果進行調試。

3.

Integrity 3D-IC

與系統分析工具的融合

在做完系統級規劃之后,我們希望能夠直接進入物理實現工具做芯片物理實現,或者進入分析和驗證工具做早期系統分析驗證。

Integrity 3D-IC 和 Cadence 的數字后端工具 Innovus、模擬版圖工具 Virtuoso、封裝設計工具 Allegro 工具等都實現了不同程度的集成。不同工具之間可以實現數據的無損交換和設計環境的自由切換。

Integrity 3D-IC 也提供了和部分常用 Cadence 分析工具的接口,包括熱分析工具 Celsius、功耗分析工具 Voltus、靜態時序分析工具 Tempus、物理驗證工具 Pegasus。工具提供了 Flow Manager 的圖形界面,來方便用戶方便地使用各種分析驗證工具,而不受制于分析驗證工具使用經驗這部分內容我們后續會做具體詳細的介紹,這里就不再贅述。

至此,我們簡單地介紹了 Integrity 3D-IC 系統級規劃平臺的特點,包括系統級規劃和優化、系統連接性檢查、Integrity 3D-IC 與其他工具的融合。希望 Integrity 3D-IC 能夠方便越來越多工程師的系統設計,加速優秀的芯片產品落地,推動后摩爾時代的發展。

-

芯片

+關注

關注

450文章

49650瀏覽量

417269 -

接口

+關注

關注

33文章

8265瀏覽量

149985 -

Cadence

+關注

關注

64文章

905瀏覽量

141478 -

三維圖形

+關注

關注

0文章

8瀏覽量

8019

發布評論請先 登錄

相關推薦

Cadence分析 3D IC設計如何實現高效的系統級規劃

Cadence 憑借突破性的 Integrity 3D-IC 平臺加速系統創新

Cadence發布突破性新產品 Integrity 3D-IC平臺,加速系統創新

Cadence Integrity 3D-IC平臺?支持TSMC 3DFabric技術,推進多Chiplet設計

Cadence Integrity 3D-IC平臺進行工藝認證

Cadence Integrity 3D-IC自動布線解決方案

Cadence擴大與Samsung Foundry的合作,共同推進3D-IC設計

Cadence Integrity 3D-IC Platform榮膺“年度EDA/IP/軟件產品”

3D-IC未來已來

聯華電子和Cadence共同合作開發3D-IC混合鍵合(hybrid-bonding)參考流程

Cadence發布基于Integrity 3D-IC平臺的新設計流程,以支持TSMC 3Dblox?標準

產品資訊 | 3D-IC 設計之自底向上實現流程與高效數據管理

Cadence 擴大了與 Samsung Foundry 的合作,依托 Integrity 3D-IC平臺提供獨具優勢的參考流程

3D-IC 以及傳熱模型的重要性

Integrity?3D-IC平臺助力設計者實現驅動PPA目標

Integrity?3D-IC平臺助力設計者實現驅動PPA目標

評論