Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數硬連線到器件邏輯互連結構和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應用加速開發流程中實現硬件內核,并使用 C/C++ 語言代碼在 Vivado Design Suite 中為賽靈思器件設計開發 RTL IP。

Vitis 高層次綜合用戶指南(UG1399)包括Vitis HLS 入門、Vitis HLS 硬件設計方法論、Vitis HLS C 語言驅動程序參考資料、Vitis HLS 命令參考資料、Vitis HLS 庫參考資料,以及Vitis HLS 移植指南。由于本指南較長,下文僅摘錄部分內容。如果您希望查閱完整版,請至文末鏈接點擊下載。

Vitis HLS 簡介

在 Vitis 應用加速流程中,在可編程邏輯中實現和最優化 C/C++ 語言代碼以及實現低時延和高吞吐量所需的大部分代碼修改操作均可通過 Vitis HLS 工具來自動執行。在應用加速流程中,Vitis HLS 的基本作用是通過推斷所需的編譯指示來為函數實參生成正確的接口,并對代碼內的循環和函數執行流水打拍。Vitis HLS 還支持自定義代碼以實現不同接口標準或者實現特定最優化以達成設計目標。

Vitis HLS 設計流程如下所述:

查看報告以分析和最優化設計。

將 C 語言算法綜合到 RTL 設計中。

使用 RTL 協同仿真來驗證 RTL 實現。

將 RTL 實現封裝到已編譯的對象文件(.xo) 擴展中,或者導出到 RTL IP。

高層次綜合基礎

賽靈思 Vitis HLS 工具可將 C 語言或 C++ 語言函數綜合到 RTL 代碼中,用于在可編程邏輯內進行加速。Vitis HLS 與Vitis 核開發套件和應用加速設計流程緊密集成。

使用高層次綜合(HLS) 設計方法論的優勢包括但不限于:

編譯、仿真和調試 C/C++ 語言算法。

查看報告以分析和最優化設計。

將 C 語言算法綜合到 RTL 設計中。

使用 RTL 協同仿真來驗證 RTL 實現。

將 RTL 實現封裝到已編譯的對象文件(.xo) 擴展中,或者導出到 RTL IP。

HLS 包含以下階段:

1調度可根據下列條件判定每個時鐘周期內發生的運算:

運算的依賴關系何時已得到滿足或者變為可用。

時鐘周期長度或時鐘頻率。

運算完成所需時間(由目標器件來定義)。

可用資源分配。

整合任意用戶指定的最優化指令。

2綁定會分配硬件資源用于實現調度的每項運算,并將運算符(例如,加法、乘法和移位)映射到特定 RTL 實現。例如,mult 運算可在 RTL 內作為組合乘法器或流水打拍乘法器來實現。

3控制邏輯抽取可創建有限狀態機(FSM),根據定義的調度按順序執行 RTL 設計中的運算。

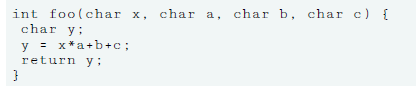

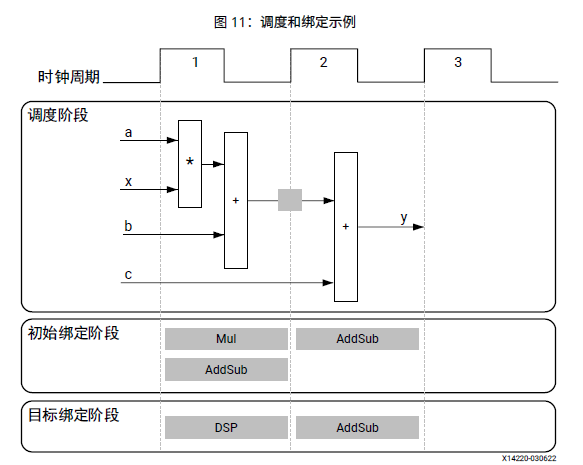

以調度和綁定為例,下圖顯示了此代碼示例的調度和綁定階段的示例:

在此示例的調度階段,根據高層次綜合的調度,在每個時鐘周期內將執行以下操作:

第一個時鐘周期:乘法和第一次加法

第二個時鐘周期:如果在第二個時鐘周期內第一次加法的結果可用,則執行第二次加法并輸出生成。

在最終的硬件實現中,高層次綜合將頂層函數的實參實現為輸入和輸出 (I/O) 端口。在此示例中,實參是簡單數據端口。因為每個輸入變量都是 char 類型,所以輸入數據端口位寬均為 8 位。return 函數為 32 位 int 數據類型,而輸出數據端口位寬為 32 位。

在此示例的初始綁定階段,高層次綜合使用組合乘法器(Mul)實現乘法運算,并使用組合加法器/減法器(AddSub)實現兩次加法運算。

在目標綁定階段,高層次綜合使用 DSP 模塊資源實現乘法器和其中一項加法運算。部分應用使用大量二進制乘法器和累加器,這些乘法器和累加器最好在專用 DSP 資源內實現。DSP 模塊是 FPGA 架構中可用的計算塊,可在高性能和高效實現之間達成理想的平衡。

Vitis HLS 進程概述

Vitis HLS 基于工程,可包含多個變體(稱為“解決方案”)以驅動綜合與仿真。每個解決方案均可將 Vivado IP 流程或Vitis 內核流程設定為目標。基于目標流程,每個解決方案都將指定不同的約束和最優化指令,如 啟用 Vivado IP 流程和啟用 Vitis 內核流程中所述。

以下提供了典型設計流程中的綜合、分析與最優化步驟:

1創建新的 Vitis HLS 工程。

2利用 C 語言仿真來驗證源代碼。

3運行高層次綜合以生成 RTL 文件。

4分析結果,包括檢驗時延、啟動時間間隔 (II)、吞吐量和資源使用情況。

5執行最優化,并按需重復此步驟。

6使用 C/RTL 協同仿真驗證結果。

Vitis HLS 基于目標流程、默認工具配置、設計約束和您指定的任意最優化編譯指示或指令來實現解決方案。您可使用最優化指令來修改和控制內部邏輯和 I/O 端口的實現,以覆蓋工具的默認行為。

C/C++ 代碼綜合方式如下:

1頂層函數實參由 Vitis HLS 自動綜合到 RTL I/O 端口接口內。如 定義接口 中所述,該工具創建的默認接口取決于目標流程、函數實參的數據類型和方向、默認接口模式以及用戶指定的任何 INTERFACE 編譯指示或指令(用于手動定義接口)。

2頂層 C/C++ 函數的子函數綜合到 RTL 設計的層級內的各塊中。

最終 RTL 設計包含與原始頂層 C 語言函數層級相對應的模塊或實體層級。

Vitis HLS 會將子函數根據需要自動內聯到更高層次的函數中或者內聯到頂層函數中,以提升性能。

您可通過在解決方案中向子函數指定 INLINE 編譯指示,或者使用 set_directive_inline 并將其設置為OFF 來禁用自動內聯。

默認情況下,C 語言子函數的每次調用使用的 RTL 模塊的實例是相同的。但您可以通過在解決方案中指定ALLOCATION 編譯指示或者使用 set_directive_allocation 來實現多個 RTL 模塊實例以提升性能。

3控制邏輯抽取可創建有限狀態機(FSM),根據定義的調度按順序執行 RTL 設計中的運算。

Vitis HLS 工具將不會展開循環,除非這樣能夠提升解決方案性能,如展開嵌套的循環以對頂層函數進行流水打拍。收起循環時,綜合會為循環的單次迭代創建邏輯,RTL 設計會為序列中循環的每次迭代都執行此邏輯。展開循環允許循環的部分或全部迭代并行發生,但也會耗用更多器件資源。

您可以使用 UNROLL 編譯指示或 set_directive_unroll 命令來手動展開循環。

循環還可通過如下任一方法進行流水打拍:通過有限狀態機高精度實現(循環流水打拍)或者采用基于較低精度的握手的實現(數據流)。

4代碼中的陣列將綜合到最終 FPGA 設計中的塊 RAM (BRAM)、LUT RAM 或 UltraRAM 中。

如果陣列位于頂層函數接口上,那么高層次綜合可將此陣列作為端口來實現,以便訪問設計外部的塊 RAM。

您可使用 ARRAY_PARTITION 或 ARRAY_RESHAPE 編譯指示或者關聯的 set_directive_array 命令更改。

綜合后,您可以對先前生成的各項報告中的結果進行分析,以確定結果質量。分析結果后,您可以為工程創建其它解決方案,指定不同的約束和最優化指令,并對這些結果進行綜合與分析。您可對不同解決方案的結果進行比較,查看哪些有效,哪些無效。您可重復此過程,直至設計達成所期望的性能特性為止。您可使用多種解決方案持續進行開發,同時仍可保留先前的解決方案。

原文標題:Vitis 高層次綜合用戶指南

文章出處:【微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

-

賽靈思

+關注

關注

32文章

1794瀏覽量

130954 -

C語言

+關注

關注

180文章

7575瀏覽量

133974 -

Vitis

+關注

關注

0文章

145瀏覽量

7310

原文標題:Vitis 高層次綜合用戶指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA高層次綜合HLS之Vitis HLS知識庫簡析

使用Vitis HLS創建屬于自己的IP相關資料分享

Vivado HLS和Vitis HLS 兩者之間有什么區別

利用Vitis HLS tcl shell一鍵跑通視覺加速例程

基于Vitis HLS的加速圖像處理

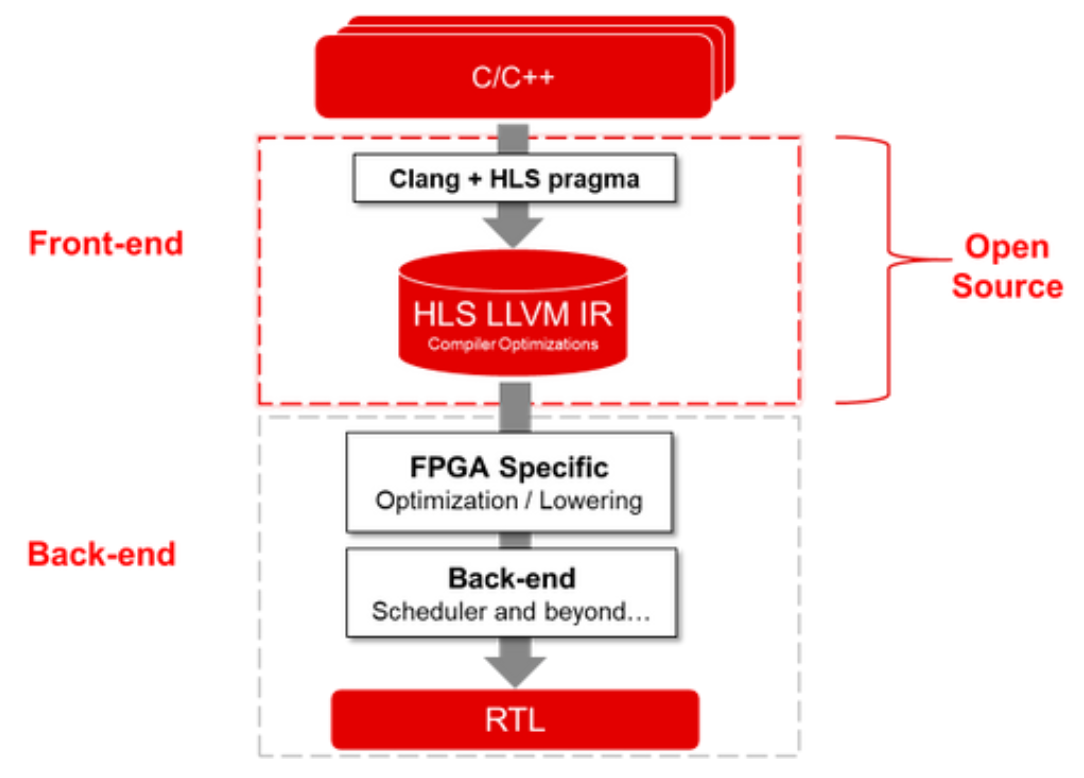

開啟無限可能的世界:Vitis HLS 前端現已全面開源

Vitis HLS前端現已全面開源

Vitis HLS知識庫總結

理解Vitis HLS默認行為

HLS最全知識庫

如何在Vitis HLS GUI中使用庫函數?

Vitis HLS工具簡介及設計流程

Vitis HLS工具簡介及設計流程

評論