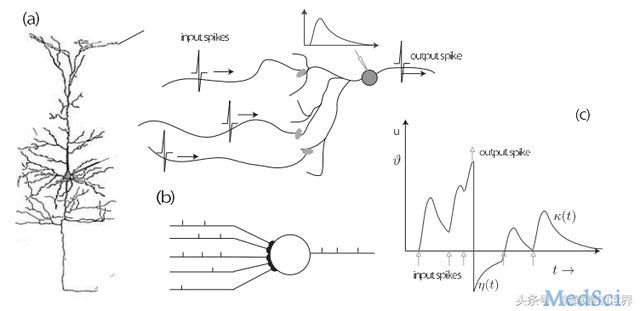

脈沖神經(jīng)網(wǎng)絡(luò)( Spiking neural network-SNN ) 是更接近自然神經(jīng)網(wǎng)絡(luò)的人工神經(jīng)網(wǎng)絡(luò)。除了神經(jīng)元和突觸狀態(tài)之外,SNN 還將時(shí)間概念納入其操作模型。這個(gè)想法是, SNN 中的神經(jīng)元不會(huì)在每個(gè)傳播周期傳輸信息(就像典型的多層感知器網(wǎng)絡(luò)一樣),而是僅在膜電位發(fā)生時(shí)才傳輸信息 - 與膜電荷相關(guān)的神經(jīng)元的內(nèi)在質(zhì)量 - 達(dá)到特定值,稱為閾值。當(dāng)膜電位達(dá)到閾值時(shí),神經(jīng)元會(huì)放電,并產(chǎn)生一個(gè)信號(hào),該信號(hào)傳播到其他神經(jīng)元,這些神經(jīng)元又會(huì)根據(jù)該信號(hào)增加或降低它們的電位。在閾值交叉時(shí)觸發(fā)的神經(jīng)元模型也稱為脈沖神經(jīng)元模型。

SNN 原則上可以應(yīng)用于與傳統(tǒng) ANN 相同的應(yīng)用。此外,SNN 可以模擬生物有機(jī)體的中樞神經(jīng)系統(tǒng),例如在事先不了解環(huán)境的情況下尋找食物的昆蟲。由于它們的相對(duì)真實(shí)性,它們可用于研究生物神經(jīng)回路的運(yùn)作。從關(guān)于生物神經(jīng)元電路的拓?fù)浣Y(jié)構(gòu)及其功能的假設(shè)開始,可以將該電路的記錄與相應(yīng) SNN 的輸出進(jìn)行比較,從而評(píng)估該假設(shè)的合理性。然而,SNN 缺乏有效的訓(xùn)練機(jī)制,這可能會(huì)抑制某些應(yīng)用,包括計(jì)算機(jī)視覺任務(wù)。

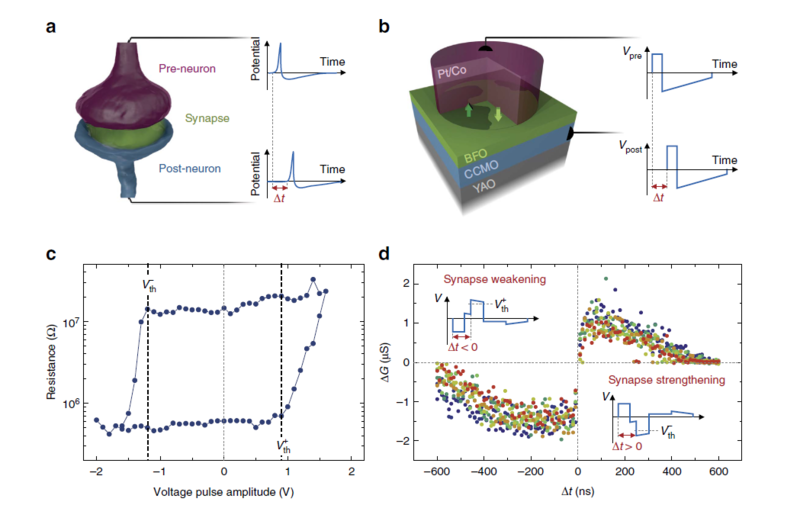

基于 FTJ 的人工突觸

下面介紹幾個(gè)SNN的開源項(xiàng)目。

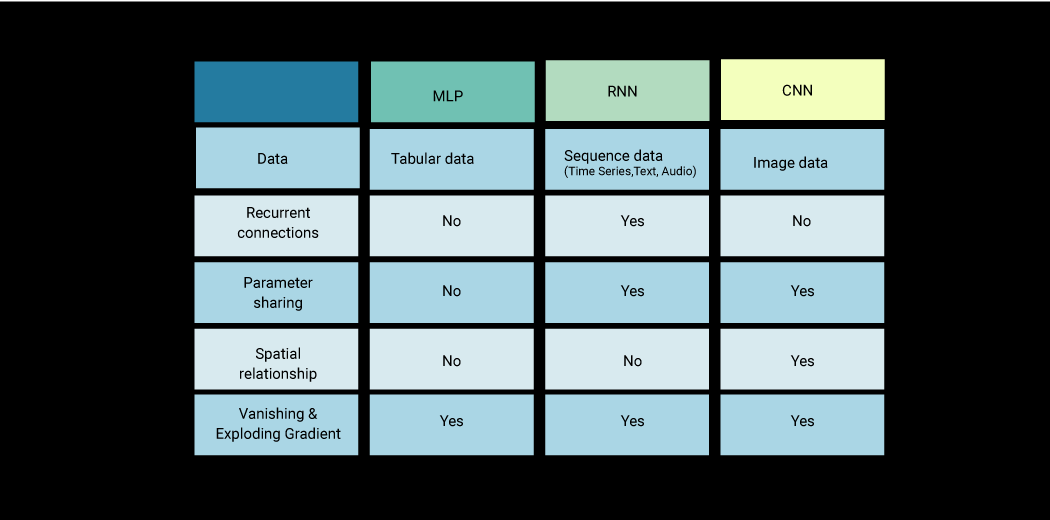

關(guān)于CNN vs. RNN vs. ANN區(qū)別,請(qǐng)看下文:

https://www.analyticsvidhya.com/blog/2020/02/cnn-vs-rnn-vs-mlp-analyzing-3-types-of-neural-networks-in-deep-learning/

https://zhuanlan.zhihu.com/p/107993566

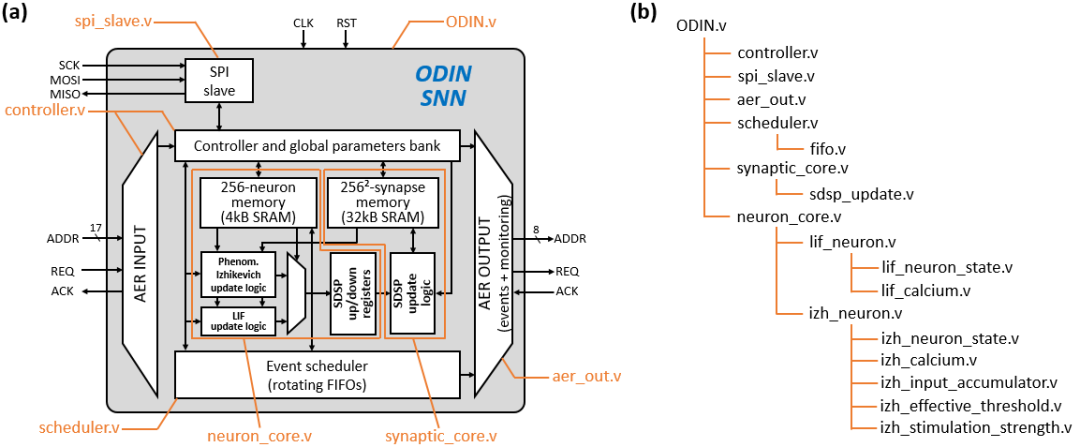

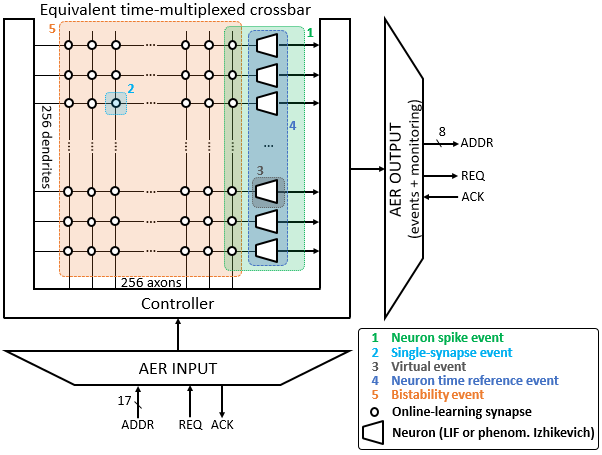

ODIN Spiking Neural Network (SNN) Processor

https://github.com/ChFrenkel/ODIN

項(xiàng)目介紹

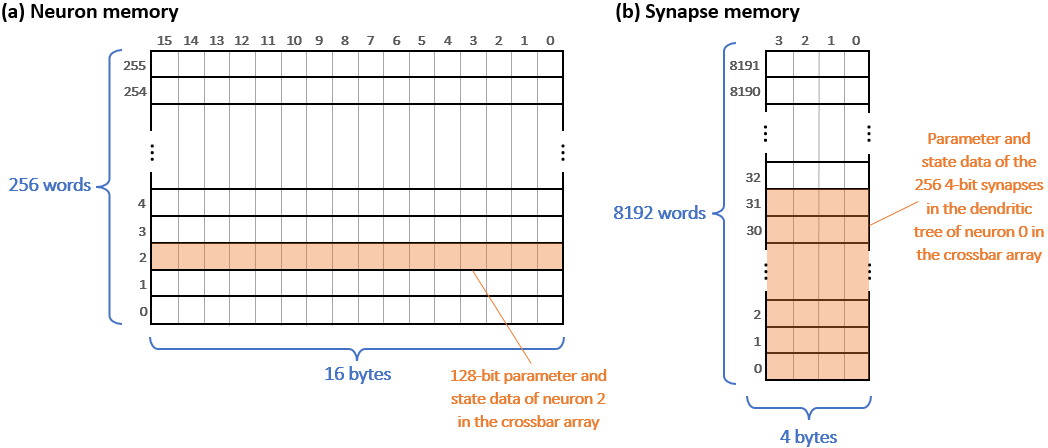

ODIN 是一種在線學(xué)習(xí)數(shù)字脈沖神經(jīng)處理器,在 2019 年發(fā)表在IEEE Transactions on Biomedical Circuits and Systems期刊上,在魯汶天主教大學(xué) ( UCLouvain ) 采用 28 納米 FDSOI CMOS 設(shè)計(jì)和原型制作。ODIN 基于單個(gè) 256 神經(jīng)元 64k 突觸橫桿神經(jīng)突觸核心,具有以下關(guān)鍵特性:

基于脈沖依賴的突觸可塑性 (SDSP) 在線學(xué)習(xí),

神經(jīng)元可以再現(xiàn) 20 種 Izhikevich 行為。

因此,ODIN 是一個(gè)用于邊緣學(xué)習(xí)的多功能實(shí)驗(yàn)平臺(tái),同時(shí)與所有先前提出的尖峰神經(jīng)網(wǎng)絡(luò) (SNN) 相比,記錄神經(jīng)元和突觸密度更高。

使用源代碼時(shí),請(qǐng)引用相關(guān)論文:

https://arxiv.org/pdf/1804.07858.pdf

同時(shí)該項(xiàng)目也有詳細(xì)的設(shè)計(jì)文檔:

https://github.com/ChFrenkel/ODIN/tree/master/doc

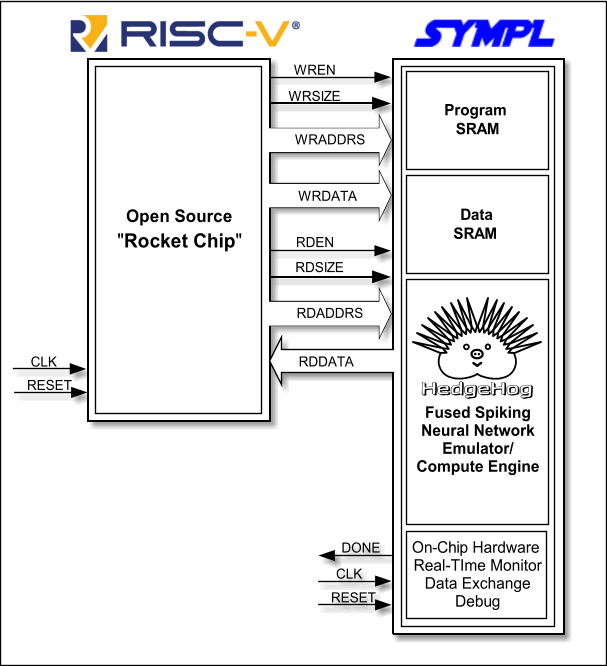

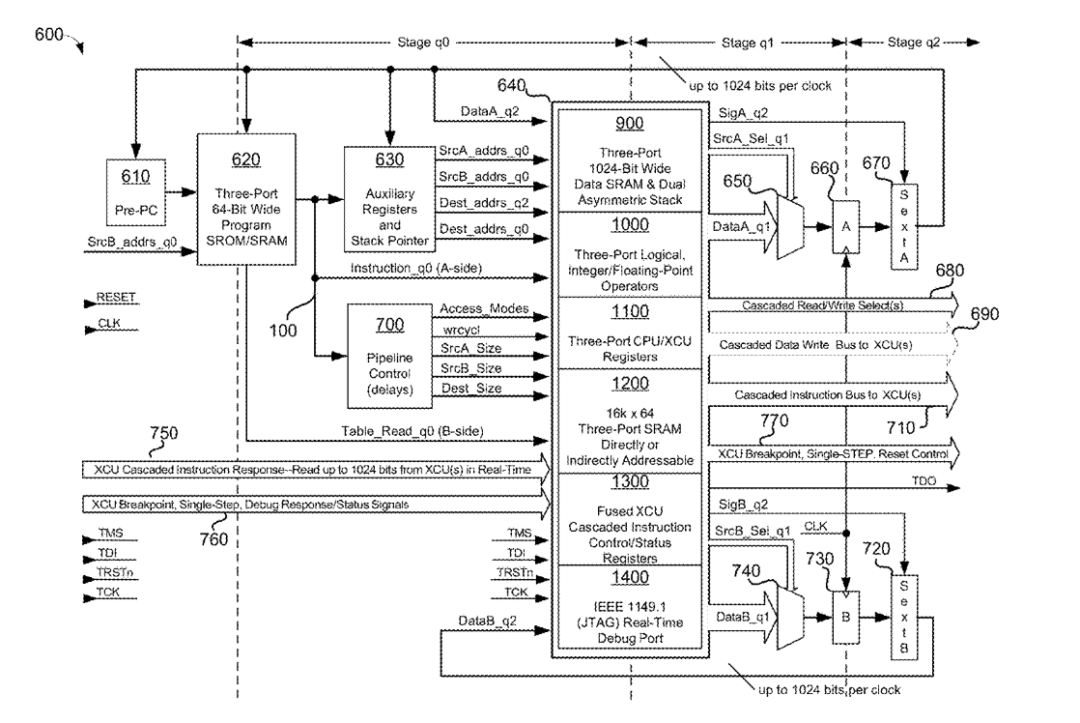

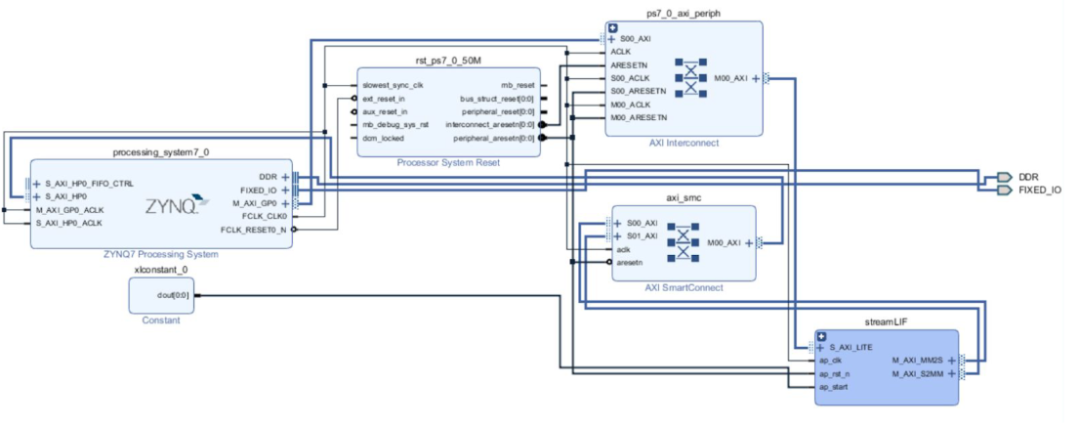

HedgeHog-Fused-Spiking-Neural-Network-Emulator-Compute-Engine

https://github.com/jerry-D/HedgeHog-Fused-Spiking-Neural-Network-Emulator-Compute-Engine

用于 RISC-V 的 HedgeHog 融合脈沖神經(jīng)網(wǎng)絡(luò)仿真器/計(jì)算引擎(有FPGA驗(yàn)證)

介紹

在 Xilinx Kintex Ultra Plus 中運(yùn)行時(shí)鐘頻率約為 100MHz,它可以執(zhí)行大約 312qty。每個(gè)時(shí)鐘周期的浮點(diǎn)運(yùn)算約每秒 310 億次浮點(diǎn)運(yùn)算。指令集中的累積和激活位可以連接8個(gè)神經(jīng)元膜。如果你正在探索或試驗(yàn)使用 RISC-V 作為主機(jī) CPU 的 FPGA 嵌入式 AI 應(yīng)用程序的脈沖神經(jīng)網(wǎng)絡(luò),那么 SYMPL HedgeHog 非常適合你。

這是有關(guān) HedgeHog FSNN 模擬器/計(jì)算引擎的 .pdf 信息表:

https://github.com/jerry-D/HedgeHog-Fused-Spiking-Neural-Network-Emulator-Compute-Engine/blob/master/HedgeHog.pdf

在 Xilinx Vivado IDE 中進(jìn)行仿真

Vivado需要的所有 Verilog RTL 源文件都位于此存儲(chǔ)庫(kù)的“RTL”、“ASM”、“test bench”和“sim”文件夾中。頂級(jí)模塊是“HedgeHog.v”。建議第一次在 Vivado 中創(chuàng)建項(xiàng)目時(shí),選擇 Xilinx Kintex Ultra+ xcku5p-ffvd-900-3-e 作為目標(biāo)器件。在 Vivado 中創(chuàng)建項(xiàng)目后,需要設(shè)置“HedgeHog.v”為項(xiàng)目“Top”文件。

下一步是將“SpiNNe_tb.v”測(cè)試文件拉入 Vivado 作為激勵(lì)。然后向下滑動(dòng)到“Simulation Sources”>“sim_1”,對(duì)測(cè)試文件“SpiNNe_tb.v”執(zhí)行與“HedgeHog”相同的操作,在仿真源中將其設(shè)置為“top”。

完成后,單擊“運(yùn)行仿真”。之后,會(huì)注意到仿真失敗。這是因?yàn)榉抡嫘枰皊pikeDemo.HEX”程序來執(zhí)行 HedgeHog。為了解決這個(gè)問題,將“spikeDemo.HEX”文件粘貼到仿真工作目錄中:“C:projectNameprojectName.simsim_1ehavxsimspikeDemo.HEX”,在“ASM”文件夾中可以找到匯編語(yǔ)言源代碼和對(duì)象列表。

接下來,演示仿真,它只是將一系列脈沖推入 HedgeHog,需要“spike_trains.txt”尖峰輸入文件和位于“sim”文件夾中的“weights.txt”文件,因此將這兩個(gè)文件粘貼到與放置“spikeDemo .HEX”文件的工作目錄相同。

完成后,再次單擊“運(yùn)行仿真”按鈕以啟動(dòng)仿真即可看到仿真結(jié)果。

該項(xiàng)目還有很多詳細(xì)的設(shè)計(jì)文檔,就不一一說明了。

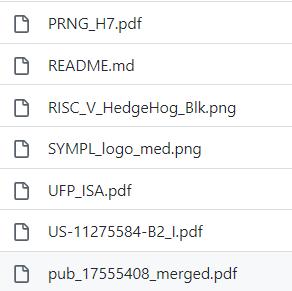

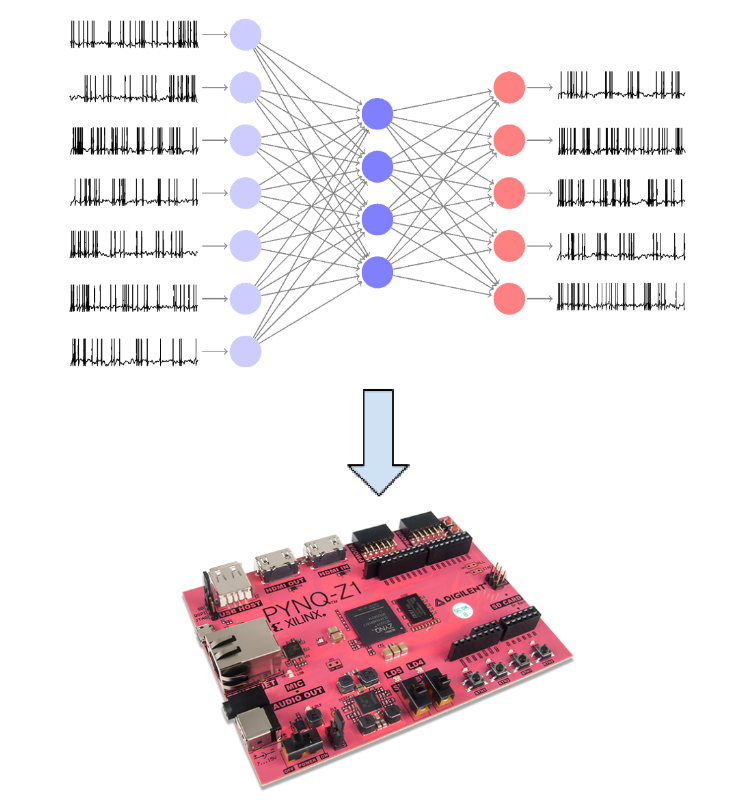

CSE237D-PYNQ-SNN-Accelerator

https://github.com/snagiri/CSE237D-PYNQ-SNN-Accelerator

脈沖神經(jīng)網(wǎng)絡(luò)在 PYNQ-Z1 板上的硬件實(shí)現(xiàn)

S2NN-HLS

https://github.com/eejlny/S2NN-HLS

該項(xiàng)目提出了一種用于脈沖神經(jīng)網(wǎng)絡(luò)的高性能架構(gòu),可優(yōu)化在主存儲(chǔ)器中的配置數(shù)據(jù)的數(shù)據(jù)精度和流式傳輸。神經(jīng)網(wǎng)絡(luò)基于 Izhikevich 模型,并使用HLS映射到 CPU-FPGA 混合設(shè)備。實(shí)驗(yàn)表明,將電壓和頻率縮放應(yīng)用于 DDR 存儲(chǔ)器和可編程邏輯可以分別將其能量需求降低高達(dá) 77% 和 76%。

詳細(xì)設(shè)計(jì)論文:

http: //dx.doi.org/10.1016 /j.micpro.2017.06.018。

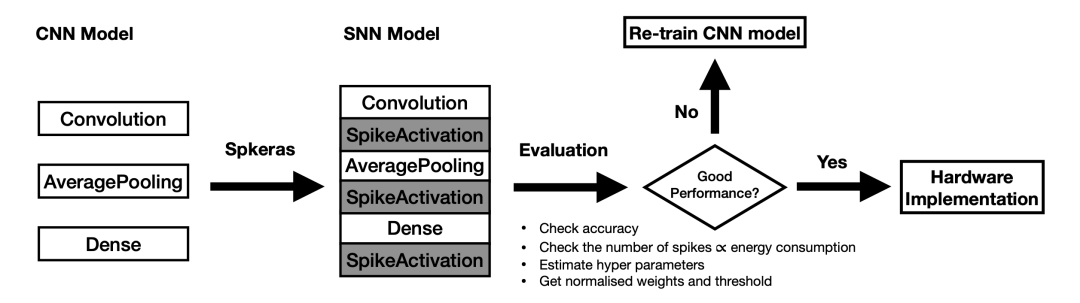

Conversion from CNNs to SNNs

https://github.com/Dengyu-Wu/spkeras

SpKeras 可以通過以下步驟獲取和評(píng)估基于速率的脈沖神經(jīng)網(wǎng)絡(luò) (SNN):

使用 Tensorflow-keras 預(yù)訓(xùn)練卷積神經(jīng)網(wǎng)絡(luò) (CNN)

使用 SpKeras 將 CNN 轉(zhuǎn)換為 SNN

評(píng)估 SNN 并獲取參數(shù),例如權(quán)重、偏差和閾值

其他

https://github.com/oshears/SNN-FPGA-Implementation

https://github.com/jasha64/SNN-FPGA

https://github.com/Minz9/SNN-on-FPGA

https://github.com/oshears/fpga_snn_models

總結(jié)

今天介紹了主要3個(gè)SNN的項(xiàng)目,主要是SNN復(fù)雜度較TPU或者CNN或者DNN又高了幾個(gè)臺(tái)階,所以用它來直接對(duì)FPGA進(jìn)行移植難度很大,建議對(duì)第一個(gè)前三個(gè)項(xiàng)目進(jìn)行研究,其他都不怎么推薦(想研究也沒有文檔)。

關(guān)于DNN或者CNN或者SNN也介紹了幾十個(gè)項(xiàng)目了,后面可能就不會(huì)出神經(jīng)網(wǎng)絡(luò)的項(xiàng)目了,感覺大家也看膩了,后續(xù)會(huì)出一些視頻處理或者圖像處理的項(xiàng)目。

最后還是強(qiáng)推一波官方神經(jīng)網(wǎng)絡(luò)加速的項(xiàng)目:

官方提供的各種案例也是基本覆蓋了常規(guī)應(yīng)用。

最后,還是感謝各個(gè)大佬開源的項(xiàng)目,讓我們受益匪淺。后面有什么感興趣方面的項(xiàng)目,大家可以在后臺(tái)留言或者加微信留言,今天就到這,我是爆肝的碎碎思,期待下期文章與你相見。

審核編輯 :李倩

-

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4764瀏覽量

100541 -

神經(jīng)元

+關(guān)注

關(guān)注

1文章

363瀏覽量

18438

原文標(biāo)題:優(yōu)秀的 Verilog/FPGA開源項(xiàng)目介紹(二十四)- 脈沖神經(jīng)網(wǎng)絡(luò) (SNN)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

LSTM神經(jīng)網(wǎng)絡(luò)的結(jié)構(gòu)與工作機(jī)制

分享幾個(gè)用FPGA實(shí)現(xiàn)的小型神經(jīng)網(wǎng)絡(luò)

介紹幾個(gè)脈沖神經(jīng)網(wǎng)絡(luò)的開源項(xiàng)目

介紹幾個(gè)脈沖神經(jīng)網(wǎng)絡(luò)的開源項(xiàng)目

評(píng)論