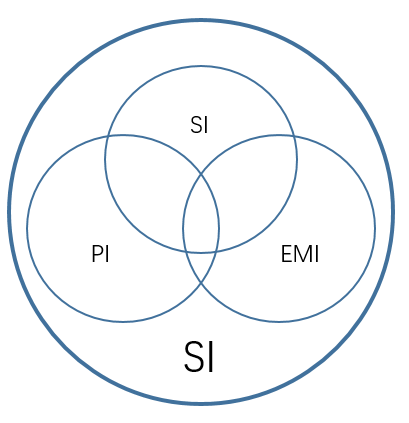

先說一下,信號完整性為什么寫電源完整性?SI 只是針對高速信號的部分,這樣的理解沒有問題。如果提高認知,將SI 以大類來看,SI&PI&EMI 三者的關系:

所以,基礎知識系列里還是得講講電源完整性。話不多說,直接上圖:

01

區別

記得剛接觸信號完整性的時候,對電源完整性(PI)和電源工程師之間的關系是分不清的。后來才漸漸了解這里面的千差萬別。簡單來說,電源的產生與轉化,比如Buck電路,LDO,DC-DC等,源端部分這些是電源工程師來確定的。

電源工程師也會進行相關的電源可靠性設計與測試,比如耐壓余量,耐電流余量,保護設計(過壓、過溫、過流等)。這些工作是電源工程師的專業范疇。電源這一塊很復雜,光各種拓撲結構就已經讓人云里霧里了,絕對是可以深究的一份職業。

02

PDN

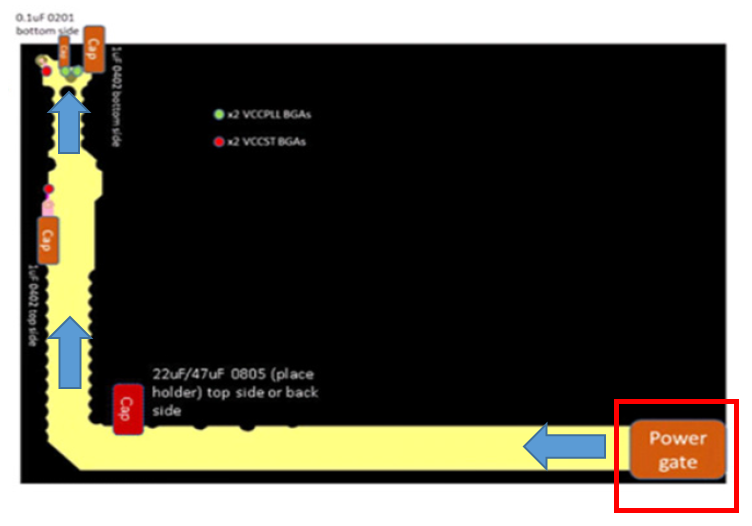

電源完整性(PI)更關注于電源路徑及終端,也就是電源分配網絡(PDN)。從源端穩壓模塊(VRM)經過路徑(單層直達或過孔轉換的幾個層面),到達終端,最終流向使用芯片或經過線纜到使用設備。

電源路徑與信號路徑是有區別的,電源分配網絡中一個電源路徑可以在一個節點分成多個路徑,或者說轉換成多個電源,終端掛多個元器件,可以理解為一對多。而信號路徑只能一對一。

既然電源分配網絡是為終端設備提供所需電源,那就是有要求,就需要對電源分配網絡管控。如信號路徑,除了保證返回電流,還要盡量保證返回路徑的低阻抗。由于是一對多的情況,這樣的管控,才能保證返回電流不相互重疊,不會發生地彈,即盡量避免開關噪聲(SSN)。

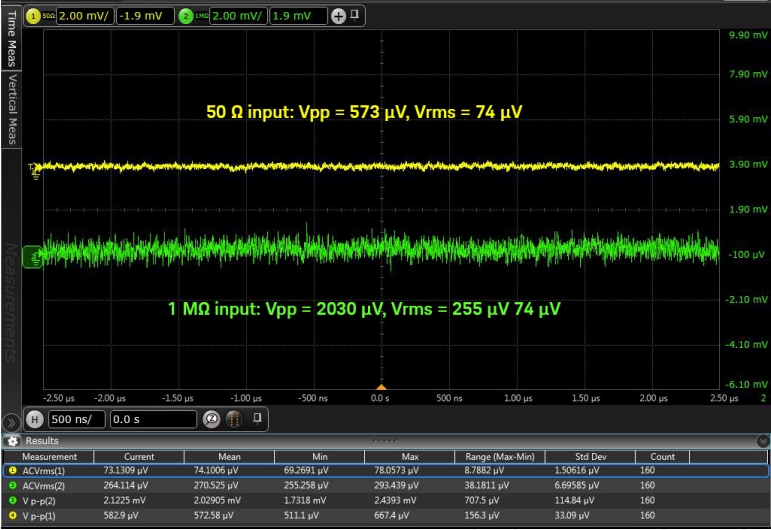

基本要求是,保證供電電壓穩定,至少能夠維持在一個很小的容差范圍內,通常在+/-5%以內。電源的測試中有紋波測試,這個紋波測試標準就是+/-5%。

講到返回電流,這里就要分為直流部分和交流部分。

直流部分:

終端設備需要穩定的電壓輸出,電源分配網絡互連之間串聯電阻的存在,直流部分通過,就會產生壓降,通常稱為IR 壓降。當電流發生波動時,壓降也會隨之波動,從而影響終端設備的識別。之前的USB設備好像最低電壓值4.75 V。

交流部分:

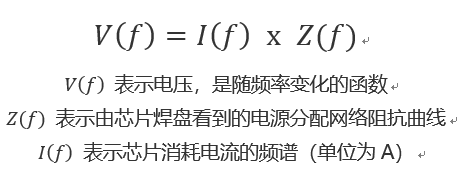

當交流電流通過電源路徑時,電源分配網絡上也將產生電壓降,這個壓降會隨著頻率發生變化:

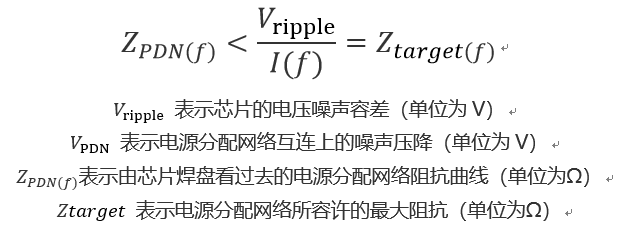

電源路徑的不同(層數&Shape寬度等),造成的壓降變化是不同的,輸出穩定電壓到終端的難度很大,我們所要做的只是保證電壓的變化在一定的范圍之內,也就是所謂的噪聲容差。上式就可能轉換為目標阻抗:

既然保證不了路徑上電壓的穩定,那么電源分配網絡的電流在波動的情況下,就需要保持電源分配網絡阻抗低于目標阻抗。

需要注意的是,即使同一個電源芯片或模塊,針對不同的產品,也會給出不同的標準。即使相同的標準,因為不同的電源路徑,不同的版圖走線,也會有千差萬別。所以,電源分配網絡目標阻抗才是最基本的要求。

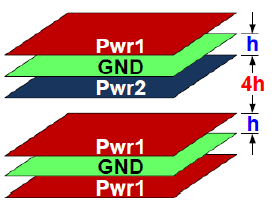

目標阻抗的管控說到底就是路徑管控。兩個因素:電源和地平面之間介質盡量薄,盡量短而寬的走線。

03

電源樹(Power tree)

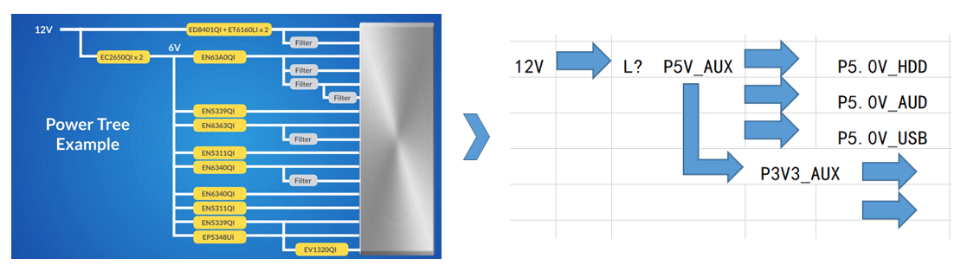

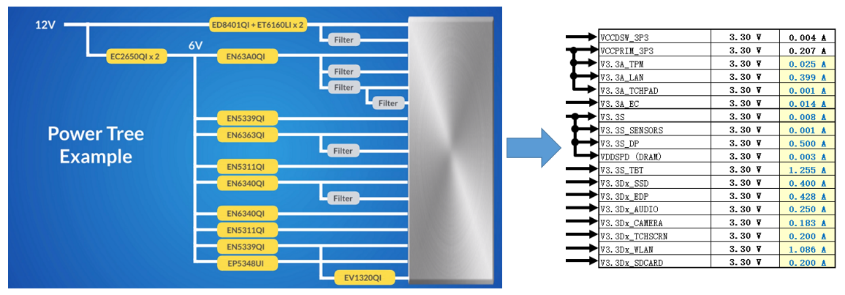

先期評估,確認各個電所需層面和路徑的時候,我們會預先根據相關規范或標準,制定一個電源樹(Power tree)。個人覺得電源樹的概念提的特別好。一個主干道有很多分支,分支上再有分叉,一直到末端。

電源分配網絡可以有很多分支,也就是說路徑上可以掛很多設備,比如5V電源下掛HDD,USB設備等。

電源的分類

比如12 V的電轉出5V,5V總電分出分支,給到各種設備。5V經過LDO轉換電路出3.3V電,,3.3V總電分出分支,再往下繼續……

同時列出各個分支所需電流的多少,為后面路徑規劃(所需電源Shape大小給出標準),同時給出對應的層面及評估。

在做電源路徑規劃,建議先做電源樹Power Tree,對所做設計的終端設備所需電壓路徑及所需電流大小一一評估,產品的不同,有的產品可能會使用幾十種電壓值。檢查的時候,建議從終端往前反推,這樣保證沒有遺漏。

04

頻段管控

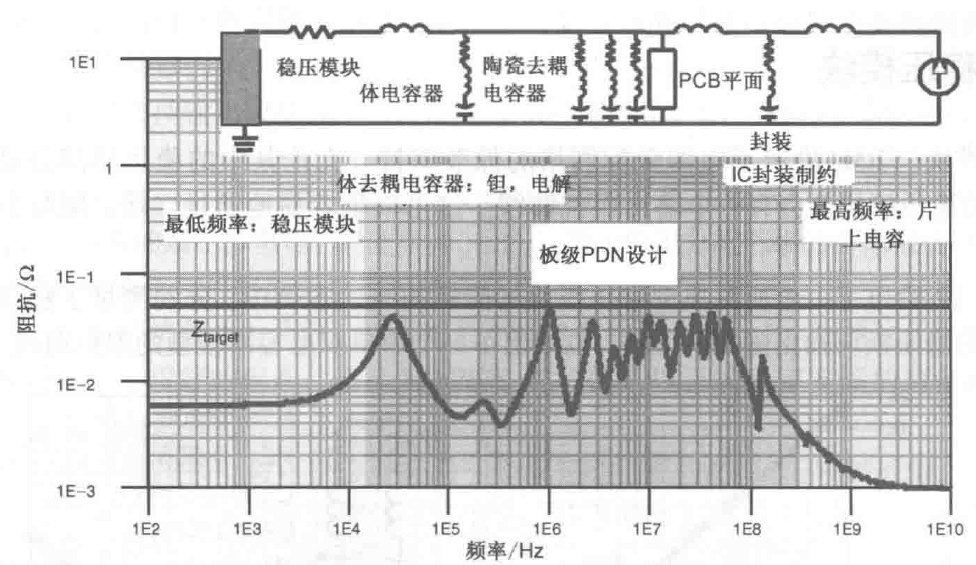

上面提到一款產品,有幾十種電壓,每個電壓的目標阻抗隨著頻率是改變的,這個時候就需要對路徑進行頻段分類:

片選電容

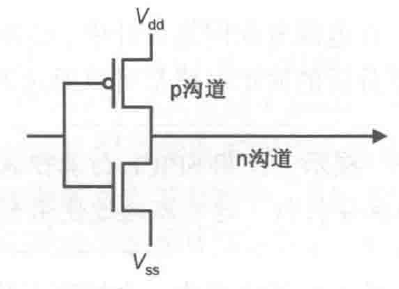

芯片是由晶體管組成,不管是P溝道還是n溝道導通,都會形成柵極電容,隨著制程工藝的提升,溝道長度變短,單位面積電容增大。所以,高頻時,片上電容為電源分配網絡提供了低阻抗。

穩壓模塊

穩壓模塊( VRM)決定了電源分配網絡的低頻阻抗。穩壓模塊是為了保證輸出阻抗低頻的阻抗曲線。

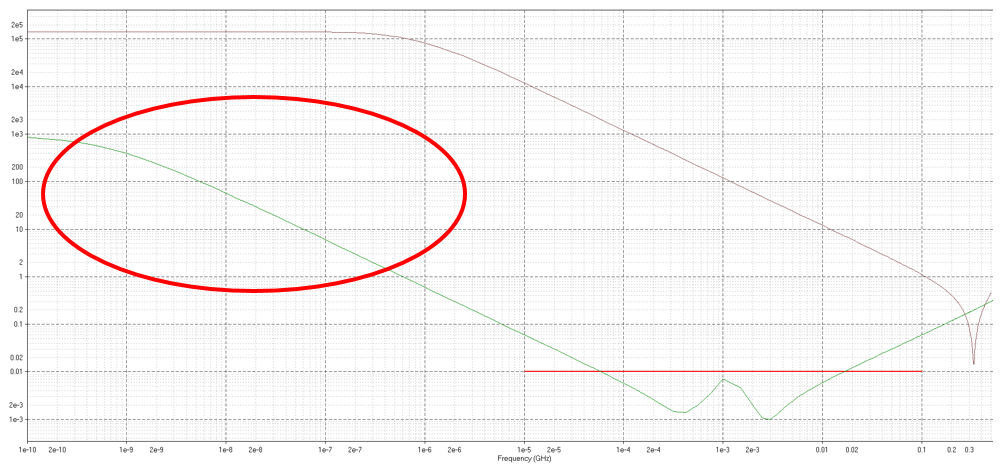

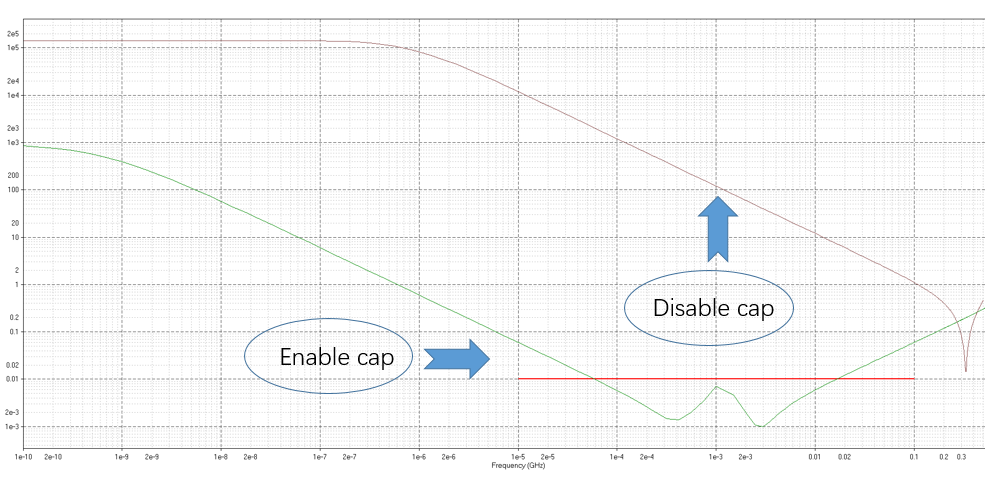

實際中VRM沒有相關模型,所以我們仿真的曲線見下圖。所以在低頻(10K以下)阻抗反而很高。

PCB板級

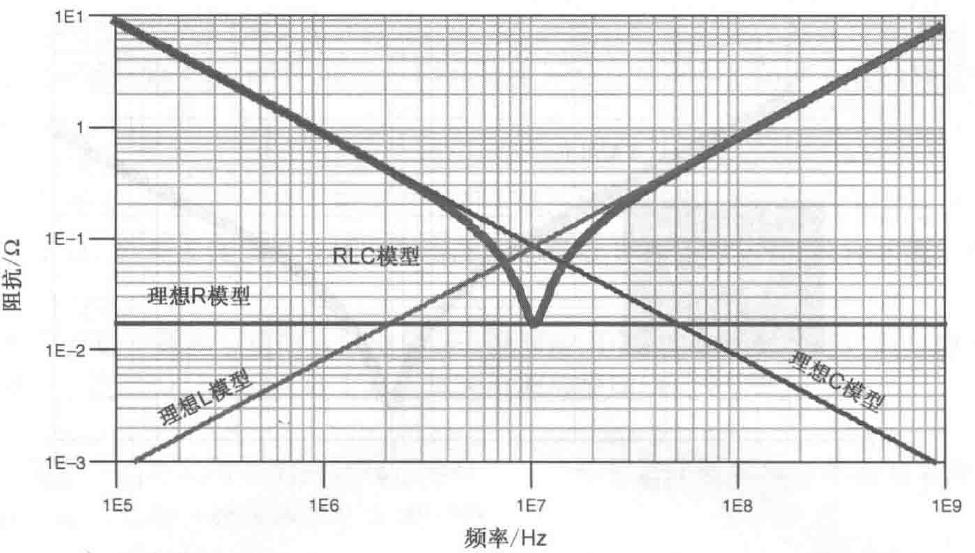

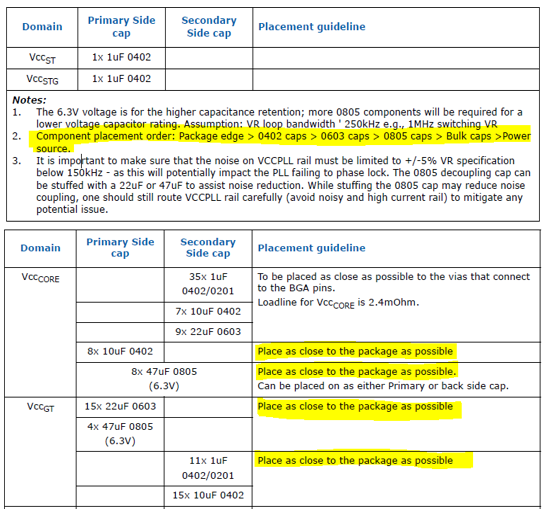

為了確定板級電源分配網絡的設計目標阻抗,可以先找出上限頻率,即找出PCB板的阻抗開始超過目標阻抗時的頻率點。如果要整個單獨分析,會比較麻煩。在低頻時,RLC 電路的阻抗取決于理想電容,在高頻時則取決于理想電感。而理想電阻則決定了 RLC 的最低阻抗。

簡單點,分為電感和電容的兩個部分。相關公式為:

注意其和截止頻率公式區分。

電感方面考慮封裝引腳、過孔和擴散電感等共同作用。

封裝引腳是串聯在芯片焊盤到電路板焊盤之間,可能有數百個電源/地平面對,開關數量的不同,封裝引腳電感是變化的,一般不超過1 nH。還有過孔及電源/地平面上運送電流過程中的擴散電感,共同決定了回路電感。

當然,這里面過孔與過孔之間,平面之間,表層傳輸線之間等,這些情況的回路電感,這里就不做展開。

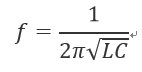

電容方面從擺放位置、電容容值&個數、反諧振三個方面來說。不同的容值,不同封裝,耦合半徑的不同,所以擺放的位置需要考慮。還有,電容器的相關組合,擺放位置都是盡量靠近封裝,那是因為電流重疊,擴散電感增加,電容器擺放可以減小增加量。

所以,電容器組合對電源分配網絡阻抗曲線的影響,在很大程度上取決于擺放在PCB板上位置。

電容除了擺放位置還要分為容值相同和容值不同的兩種情況。在通常的板級應用中,使用較少個數的不同容值的電容器(而不是使用相同容值的電容器)往往能使阻抗最低的原因。為了使電容器的個數最少 ,一般選擇不同的容值。

選擇不同容值的電容器,還有一個原因:反諧振。容值的不同,自諧振頻率也不同,電容之間的并聯,讓其之間有一個新的特性,即阻抗的峰值,稱為并聯諧振峰值,它發生在并聯諧振頻率( Parallel Resonant Frequency, PRF)處。這時候就需要添加一個其自諧振頻率介于它們之間的電容器加以降低。

需要注意的是,當需要采用多個電容并聯來滿足容值要求時,最好采用同類型的電容進行并聯。這里的同類型是指封裝。

板級電源分配網絡設計的頻率范圍約從 100 kHz 到 100 MHz。這正是電路板平面和多層陶瓷貼片電容器( MLCC) 發揮作用的頻率范圍 。這也是仿真時,重點關注的頻率范圍。

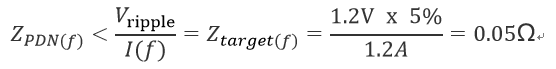

本例以1.2V的CPU用電為例,來舉例說明PDN阻抗仿真。紋波百分比5%,最大電流為1.2A,根據公式

上圖說明,是否使能電容對PDN阻抗的影響很大。

05

總結

在電源樹里,我們給出的都是產品規格或者設計規范里給出的峰值電流,實際的應用中,這種情況出現的機率很小。所以,消費類產品,在成本的管控之下,會給出不同配置的產品。低配版本,這時候,會減小MLCC的使用種類和數量,OptimizePI是一項很重要的工作,這個后面有機會再講。通過優化,來降低產品成本,這也是電源完整性的關鍵所在。

審核編輯 :李倩

-

電源

+關注

關注

184文章

17586瀏覽量

249500 -

阻抗

+關注

關注

17文章

940瀏覽量

45821 -

信號完整性

+關注

關注

68文章

1397瀏覽量

95385

原文標題:電源完整性基礎知識

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

信號完整性為什么寫電源完整性?

信號完整性為什么寫電源完整性?

評論