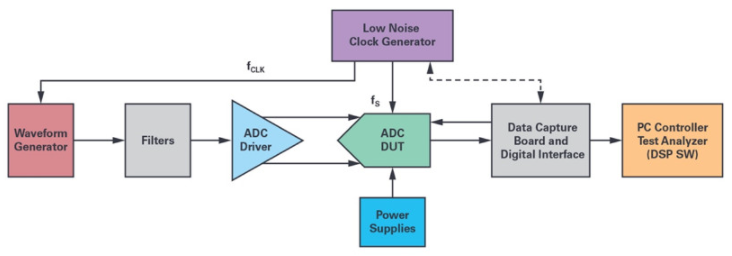

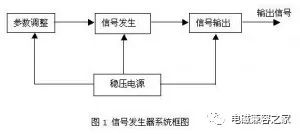

分辨率優于 16 位的高精度快速模數轉換器 (ADC) 的交流性能測試和驗證需要一個近乎完美的正弦波發生器,至少能夠覆蓋 0 kHz 至 20 kHz 音頻帶寬。通常,使用昂貴的實驗室儀器來執行這些評估和表征,例如 Audio Precision 的音頻分析儀 AP27xx 或 APx5xx 系列。大多數時候,具有 24 位或更多位的現代高速 SAR 和寬帶 Σ-Δ (Σ-Δ) ADC 具有單電源和全差分輸入,因此要求用于 DUT 的信號源為直流和交流準確,同時提供全差分輸出(180°異相)。同樣,這個交流發生器的噪聲和失真水平應該比這些 ADC 的規格要好得多,根據大多數供應商的規范,在 1 kHz 或 2 kHz 和高達 20 kHz 的輸入音調頻率下,本底噪聲電平遠低于 –140 dBc,失真低于 –120 dBc。圖 1 顯示了適用于高分辨率寬帶 ADC 的典型臺架測試設置的典型配置。最關鍵的組件是正弦波發生器(單音或多音),此處基于軟件的直接數字合成器 (DDS) 可以提供非常靈活的頻率分辨率和與數據采集系統的時鐘同步,以執行相干采樣以避免泄漏和 FFT 窗口濾波。

只需音頻精密分析儀的一小部分成本,就可以設計一個非常精確的正弦波發生器處理器。一個相當快的浮點 DSP 將滿足實時預期并滿足所有算術和處理條件,以達到最先進的 SAR ADC 設置的失真和噪聲性能水平。利用 32 位或 64 位定點格式的全字數據長度架構的 NCO 相位累加和擴展的精密浮點 DSP 功能來執行正弦逼近函數和用于整形的數字濾波器頻譜,

直接數字頻率合成

Joseph A. Webb1 于 1970 年 4 月提交的數字信號發生器合成器專利描述了可以被視為 DDS 機制的基礎,只需使用幾個數字邏輯模塊即可生成各種類型的模擬波形,包括正弦波。然后,在 1971 年初,Tierney 等人 2 的經常引用的參考論文發表了關于通過深化正交生成的 DDS 操作來直接生成數字頻率及其對采樣系統理論的限制(字截斷和頻率規劃)。實際實現開始出現,主要依賴于分立的標準邏輯 IC,例如 TTL 74xx 或 ECL 10K 系列。不到 10 年后,斯坦福電信、高通、Plessey、和 ADI 公司的 AD9950 和 AD9955。邏輯 IC 架構旨在實現最佳速度、功率和成本折衷,基于查找表 (LUT),以確保相位、頻率和幅度分辨率有限的相位到正弦幅度轉換。如今,DDS 獨立集成電路很容易獲得,而數控振蕩器 (NCO) 往往大量集成在 RF DAC 中,例如AD9164或AD9174。盡管它們在多個 GHz 帶寬上的噪聲和線性度性能令人印象深刻,但這些器件都不適合測試LTC2378-20、AD4020或AD7768等中等速度、高分辨率 ADC 。

圖 1. 基于 IEEE 1241 標準的典型 ADC (ac) 測試設置的處理鏈。DDFS 使整個測量系統完全數字化,具有很多優點,包括完全的靈活性和連貫的采樣采集。

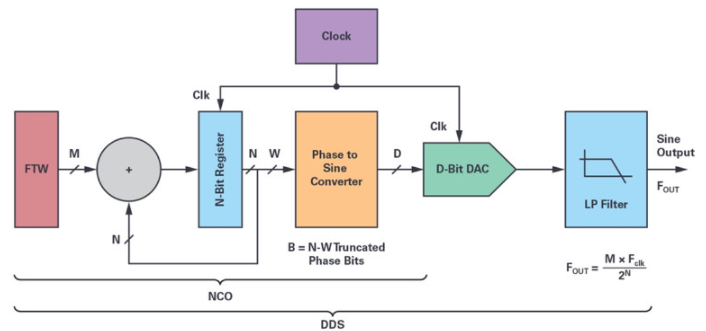

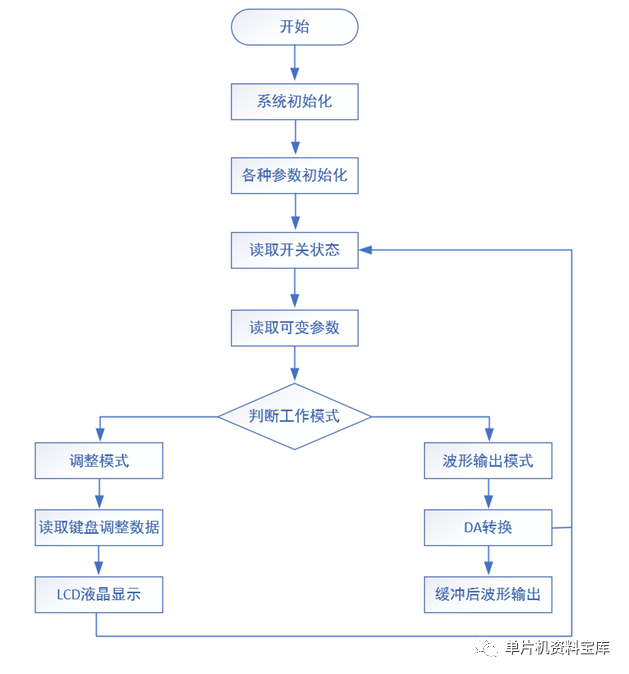

與傳統的基于 PLL 的合成器相比,NCO 和 DDS 以其非常精細的頻率分辨率、快速的靈活性和易于生成完美正交的正弦/余弦而聞名。它們還因其寬帶寬覆蓋和直流精度而備受贊譽。它們的工作原理由數字信號處理和采樣系統理論支配,它們的數字特性允許對輸出信號的相位、頻率和幅度進行完全數字化和獨立控制。圖 2 的框圖描述了傳統 DDS 的架構,它由三個主要功能組成:

N位相位累加器;

一種相位到正弦幅度轉換器,其特征在于 W 位截斷相位輸入字;

一個 D 位 DAC 及其相關的重構濾波器。

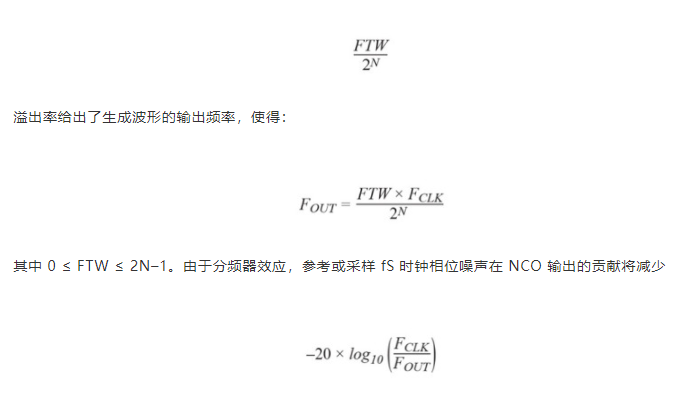

相位累加器圍繞一個簡單的 N 位加法器和一個寄存器構建,該寄存器的內容以采樣時鐘 FCLK 的速率更新,輸入相位增量為 Δθ,通常也稱為頻率調諧字 (FTW)。累加器可以周期性溢出并像采樣或參考時鐘 FCLK 和 DDS 輸出頻率 FOUT 之間的小數分頻器一樣運行,或者像齒輪箱一樣分頻比等于:

相位累加器寄存器的輸出代表生成波形的當前相位。由于相位到正弦或相位到余弦映射器引擎,每個離散累加器輸出相位值隨后被轉換為幅度正弦或余弦數據或樣本。此功能通常通過存儲在 LUT (ROM) 中的三角函數值來實現,有時通過執行正弦逼近算法或兩者的組合來實現。相位到正弦幅度轉換器的輸出饋送到 DAC,DAC 在濾波之前產生量化和采樣的正弦波,以平滑信號并避免頻譜混疊。DAC 有限分辨率施加的這種幅度量化對本底噪聲和合成器的最終信噪比 (SNR) 設置了理論限制。此外,作為混合信號設備,

基于圖 2 架構的實際正弦波形發生器實現的主要區別在于相位幅度轉換器模塊,由于數字無線電應用的市場導向,該模塊通常針對速度和功耗而不是高精度進行優化。實現相位到正弦幅度轉換器的最簡單方法是使用 ROM 來存儲具有一對一映射的正弦值。不幸的是,LUT 的長度隨著相位累加器的寬度 N 和波表數據字精度 W 呈指數增長 (2N)。不幸的是,在減小累加器大小或截斷其輸出方面進行權衡會導致頻率分辨率的損失和 SFDR 的嚴重退化。結果表明,由相位或幅度量化引起的雜散遵循 –6 dB/bit 的關系。由于通常需要大的 N 來實現精細的頻率調諧,因此已經推廣了幾種技術來限制 ROM 大小,同時保持足夠的雜散性能。簡單的壓縮方法通常通過利用正弦或余弦函數的四分之一波對稱性來將相位參數范圍縮小 4。為了進一步縮小范圍,相位累加器輸出的粗略截斷是事實上的方法,盡管它確實引入了雜散諧波。盡管如此,由于精細的頻率分辨率要求、內存大小和成本折衷,這種方法總是被采用。已經提出了各種角度分解方法來降低基于 LUT 的方法的內存要求。結合使用各種類型的分段、線性或多項式插值的幅度壓縮,其想法是在 I/Q 合成的情況下準確逼近正弦函數的第一象限或 [0, π/4] 區間需要正弦和余弦函數。類似地,無需 ROM LUT 的復雜信號生成由基于角度旋轉的算法有效支持,只需在逐次逼近方案中調用移位和相加操作。以流行的 CORDIC 為代表的這種方法通常比其他方法更快,當硬件乘法器不可用時,或者出于速度或成本考慮,實現功能所需的門數應最小化(在 FPGA 或 ASIC 中)。反過來,

圖 2. NCO 的主要功能部分以及與完整直接數字合成器的區別,包括重建 DAC 及其相關的 AAF。NCO 部分可用于測試或激勵 DAC。

在本系列的第 2 部分中,我們將詳細介紹如何在軟件中實現高精度 NCO。

關于作者

Patrick Butler 是 ADI 公司南歐銷售部門的一名現場應用工程師,負責為法國全球市場和一些 ADEF 客戶提供支持。自 1984 年以來,他一直在 ADI 工作,支持 DSP 構建模塊 IC 以及高速轉換器。此前,他曾在法國圣艾蒂安的斯倫貝謝公司 ATE 部門擔任設計工程師五年,然后在南特的 Matra-MHS、AMD 和 Harris SC-Intersil 擔任多個應用工程師和 FAE 職位。如今,他的主要愛好是在兩個兒子的幫助下收集老式聲音組件來構建有源、高效的號角揚聲器系統。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19178瀏覽量

229202 -

寄存器

+關注

關注

31文章

5325瀏覽量

120054 -

adc

+關注

關注

98文章

6452瀏覽量

544149 -

DDS

+關注

關注

21文章

632瀏覽量

152556

發布評論請先 登錄

相關推薦

阻尼正弦波模擬器的校準方法

Spectrum儀器推出能夠進行快速切換的多音DDS信號發生器

用tina-ti仿真文氏正弦波發生器沒有成功是哪里出了問題?

數字信號發生器能夠提供哪些波形信號

信號發生器是干什么用的 信號發生器可以輸出電流嗎

信號發生器的使用方法 信號發生器的幅值是有效值嗎

Spectrum儀器高速任意波形發生器DDS功能可生成20個正弦波

使用TC275的載波發生器,載波發生器輸出的正弦波會發生相位移動的原因?

Verilog實現DDS正弦波發生器

信號發生器如何發出雙脈沖?

基于STM32的波形發生器設計

DDS正弦波音調發生器的設計

DDS正弦波音調發生器的設計

評論