專用集成電路(ASIC)的設計規模不斷擴大、復雜度不斷攀升,這對芯片開發者的能力和所使用的工具都提出了更高的要求。

在之前的文章中,我們探討過數十億門級ASIC所面臨的跨時鐘域(CDC)和跨復位域(RDC)挑戰,今天我們將共同探討第三大挑戰──靜態代碼校驗。

高效的代碼校驗

讓芯片開發周期左移

代碼校驗,即對源代碼進行自動檢查以排查錯誤,是硬件開發生命周期中非常重要的一環。如果能在RTL開發的早期階段就開始代碼校驗工作,評估代碼質量以及一旦代碼錯誤會對設計流程的后續環節造成哪些影響,這對開發者來說將會大大提升開發效率,并最終實現開發周期的左移。

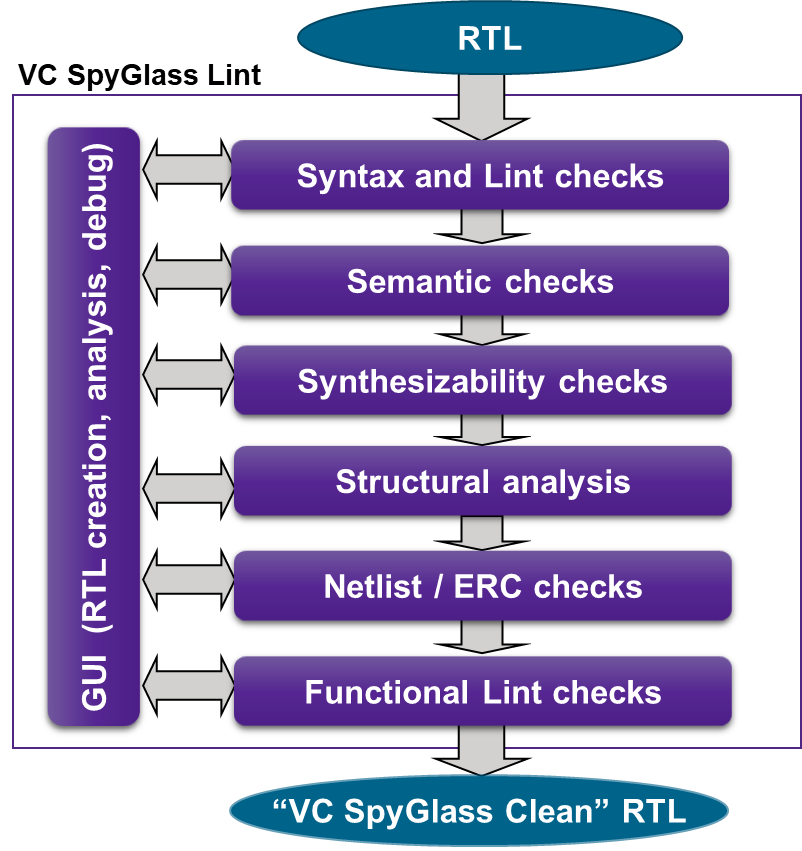

現在的代碼校驗已經遠遠超出了RTL語義規則檢查的范疇,擴展到了綜合能力檢查、結構分析以及網表/電氣規則檢查。為實現左移,芯片開發者希望能夠在開發流程早期階段就完成許多復雜的任務,比如在 RTL 內執行更復雜的檢查,以及確保 RTL 與下游合成引擎更加一致等等。開發者還希望 RTL 對各種仿真器“友好”并可進行互操作,同時兼容等價性檢查器。這些要求都不簡單,而這其中真正的挑戰就在于如何從源代碼中尋找并修復漏洞。

如果把這些挑戰放大到數十億門級ASIC的設計中,可以想想代碼校驗會有多復雜,因此為了在設計規模和復雜度不斷攀升的情況下,依舊實現將開發周期左移,就需要更強大的代碼校驗工具來幫助芯片開發者們高效完成代碼的預先排查工作。

管理規則集

代碼校驗工具需要使用規則集運行,開發者需要創建、管理和編策這些規則集。這些都是非常專業的技能,其中涉及的專業知識通常是小公司不具備的或者想要引入的,所以對小公司而言,入門級的做法就是購買現成的軟件包。而大型公司一般有自己的內部代碼校驗規則集,這些內部規則集對公司來說都是重要的投資。

第三方或行業標準規則集可以降低準入門檻,幫助小規模的設計團隊加速代碼校驗工作流程。新思科技的GuideWare方法學文檔和規則集正是為了這一目的而開發的,旨在幫助開發者快速開始采用此技術,并根據需要進一步制定規則。

GuideWare的目標是能夠在至少80%的用例中實現RTL移交,從而更大限度地減少創建、管理和編策相關規則所需的專業知識。對小型設計團隊而言,GuideWare絕對是一個福音,他們的設計可以實現質的飛躍,生產力也會大幅提升。

新思科技會對GuideWare定期進行更新,以確保規則集的復雜性始終處于行業領先地位。新思科技的IP均已通過代碼校驗認證,開發者們可以選擇新思科技的IP以及GuideWare中的設計復用合規性檢查功能,做出符合行業標準的設計。

如何處理無用代碼?

無用代碼或無法訪問的代碼在開發階段通常都會存在,有些甚至會保留到流片階段。為什么會這樣呢?

設計的復雜性在開發過程中也會不斷演進,開發者會隨時進行漏洞修復、增加功能、集成可復用的模塊等等,有時還會為了實現功耗和性能目標做全面的代碼優化,這樣就會導致最初寫的一些代碼變為無用代碼。但是由于產品交付時間并沒有因為設計變復雜而延后,迫于時間壓力,很多時候開發者沒有時間去清理這些無用代碼。雖然保留這些代碼并不會影響下個代碼的正常運行,但是如果追求精簡設計,這些代碼就必須要處理。

使用代碼校驗工具來清理無用代碼是非常有必要的,有些開發者對工具是否好用持懷疑態度,他們可能會為了以防萬一就保留相關代碼,但大多數都會秉持“零違例”準則,即“要么修復,要么放棄”。因此,代碼校驗工具能夠準確識別無用代碼并知道如何處理它們是非常重要的。

新思科技的靜態代碼校驗工具VC SpyGlass Lint采用形式引擎,在識別無用代碼上效率非常出眾。但開發者通常會有以下幾種操作選項:

更新RTL代碼從而移除無用代碼:這應該是能把無用代碼清理的最干凈的解決方案,還能夠有效移除覆蓋率分析中的覆蓋率空洞。但這一方法需要重新構思代碼,并進行功能驗證,所以比較花時間。

把無用代碼注釋掉并為了以后參考附上相關信息的注釋:雖然這種方法也還需要進行功能驗證,但它也能提供一個干凈的代碼并移除覆蓋率空洞。

棄用代碼校驗 waiver 文件中的無用代碼:僅確認無用代碼的安全性,不對其進行清理,RTL代碼庫保持不變。覆蓋空洞將仍然存在。

了解設計復雜性

越復雜的設計所包含的漏洞也就越復雜。但開發者在設計中通常都會追求精簡、直觀、一看就懂且易于維護的代碼結構。不過隨著時間的推移,在開發者不斷debug修正代碼的過程中,代碼的整體質量與最初相比會有所下降,他們可能還會突然發現RTL代碼怎么好像越改越復雜了,邏輯也越來越難理解了。

衡量并可視化呈現代碼的復雜性可以幫助開發者“看見”代碼中變得復雜的部分,他們可以利用這一信息對積攢的復雜代碼進行評估和推演。針對復雜性風險過高的代碼區,開發者會在性能和功能之間做一些權衡,并對部分代碼進行重構。

通過同行評議保證魯棒性很有用,且是一項所有設計團隊都應采用的最佳實踐,但新思科技的VC SpyGlass Lint有一個獨特的優勢是其他工具無法比擬的,就是可以衡量代碼的復雜性,為開發者提供非常有用的建議。VC SpyGlass Lint利用形式引擎提供功能分析及代碼復雜性分析,并通過儀表板呈現結果。

永遠存在的誤報問題

在CDC和RDC的文章中,我們討論過誤報問題,這一問題在代碼校驗過程中同樣存在。在數十億門級的設計中,勢必會產生大量違例,數量過大就會有遺漏風險。開發者們希望的是,工具可以幫助他們直觀地看到有意義的信息、準確評估信息、正確標記違例、對違例進行分類等等,從而提高處理違例的效率和準確性。

VC SpyGlass Lint利用形式引擎來有效解決誤報問題。開發者們無需知道形式驗證,也無需具備這方面的專業知識,所有形式驗證都將在后臺完成。這一工具內置了5000多項檢查,而且新思科技仍在不斷地對檢查項目進行添加和完善。

功能校驗,加快簽核

借助一鍵式形式驗證的功能校驗,開發者們可以在驗證平臺可用前就對功能和覆蓋率問題進行測試,從而節省時間并實現左移。功能校驗在檢查以下控制問題時非常有用:

FSM死鎖

無法訪問狀態的檢查

覆蓋率問題(如常值信號)

無用代碼檢查

數組邊界違例

總結來說,如果開發者們能夠盡早知道復雜的RTL代碼是否能夠實現預期的設計結果,他們就可以在設計開發后續流程中節省很多時間和精力,不僅實現開發周期的左移,還可節約成本。新思科技的VC SpyGlass Lint等工具可以完美解決這一問題,它利用形式引擎實現功能分析,可有效幫助開發者們盡早判斷他們的RTL代碼質量是否滿足設計需求,最終加速簽核。

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

-

芯片

+關注

關注

454文章

50452瀏覽量

421947 -

集成電路

+關注

關注

5382文章

11396瀏覽量

360931 -

asic

+關注

關注

34文章

1195瀏覽量

120346 -

新思科技

+關注

關注

5文章

789瀏覽量

50309

發布評論請先 登錄

相關推薦

讓單片機代碼性能起飛的七大技巧

單片機芯片開發-單片機方案開發的關鍵技巧和流程步驟!

如何通過I2C加載TPS2388x SRAM和奇偶校驗代碼

nxps32k144安全啟動校驗bootloader完整性

鴻蒙開發組件:DataAbility的生命周期

怎樣利用數字示波器測量信號的周期和振幅

Hex文件格式CRC校驗,怎么編寫計算校驗的程序?

華為云 Astro 全場景低代碼開發,讓業務專家秒變“技術大拿”

Arm推出汽車增強處理器及虛擬平臺,縮短人工智能汽車開發周期

?PLC左移指令和右移指令

高效的代碼校驗讓芯片開發周期左移

高效的代碼校驗讓芯片開發周期左移

評論