Zynq UltraScale+ RFSoC 是業界首款單芯片自適應無線電平臺,在一款芯片內集成射頻直采數據轉換器、單芯片軟決策前向糾錯核(SD-FEC)、FPGA邏輯、完整的ARM處理器子系統和高速收發器等。

第三代RFSoC器件與前幾代產品相比,射頻輸入輸出頻率響應已擴展至全面支持6GHz以下頻段,可幫助用戶開發尖端RF設計,例如大規模MIMO無線電、5G基帶、固定無線接入、測試測量與相控陣雷達等等。第三代器件14bit分辨率ADC最大采樣速率增加到5.0GSPS,14bit分辨率DAC最大采樣速率增加到10.0GSPS。用戶可以參考XMP105詳細了解Zynq RFSoC系列產品具體參數及選型指南。

本次將分上下篇介紹基于Xilinx Zynq UltraScale+ RFSoC ZCU216評估套件的詳細內容:

1. 第三代RFSoC 器件時鐘轉發特性。

2. ZCU216時鐘結構及可行的時鐘設計方案。

3. 在Vivado中創建基于IP集成器(IP Integrator)的設計。

4. 在Vitis中創建基于ARM的BareMetal程序設計。

5. 代碼簡要分析。

6. 硬件環境及測試結果。

本文用于示例的軟件工具、驅動版本、硬件版本及文檔版本如下:

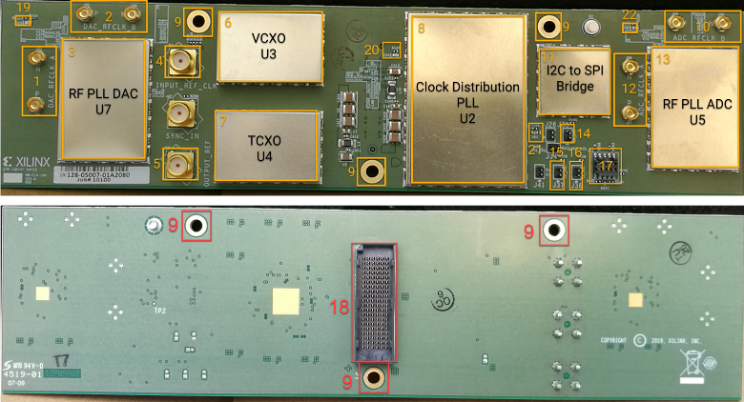

1. ZCU216 Rev-A02(Engineer Sample)

2. CLK104

3. Vivado 2021.2 + Vitis 2021.2

4. PG269 V2.6 October 27, 2021

5. Software Driver: rfdc v11.0

1. 第三代RFSoC 器件時鐘轉發特性:

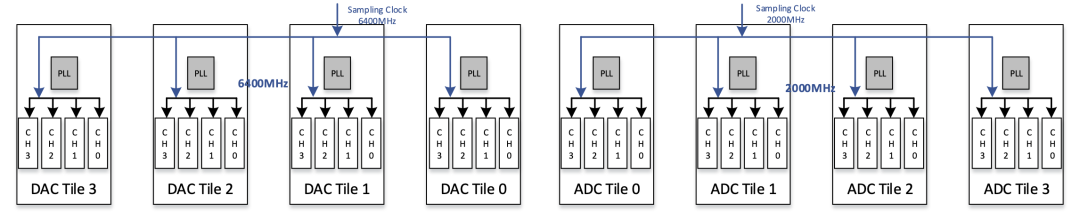

RFSoC在芯片內集成了數據轉換器,第三代RFSoC系列器件均包含4個ADC Tile和4個DAC Tile,每個ADC和DAC Tile內可能包含1個(ZU43DR)或2個(ZU47DR/48DR)或者4個(ZU49DR)Channel,這取決于芯片型號。以ZCU216開發板上的芯片為例,ZU49DR的每個ADC Tile內包含4路ADC,每個DAC Tile內包含4路DAC。

每個Tile都可以獨立配置,工作在不同的采樣時鐘頻率上,采樣時鐘可以來自于外部高頻時鐘輸入,可以來自于每個Tile內部PLL倍頻后的時鐘,也可以來自于其他Tile分發的參考時鐘。

第三代RFSoC器件相比之前幾代產品引入了時鐘轉發特性,不再需要為每個Tile都提供獨立的采樣時鐘,節省了引腳數量,降低了外圍電路的復雜度。

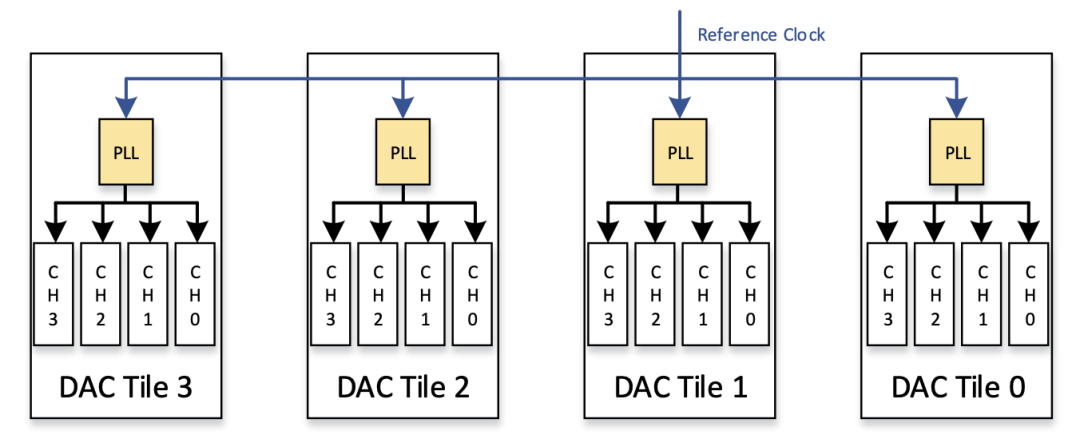

時鐘轉發的方式共分為兩種,一種是參考時鐘轉發,一種是采樣時鐘轉發。

所謂參考時鐘轉發,是指外部時鐘芯片提供低噪聲低頻時鐘到一個ADC/DAC Tile的專用時鐘管腳,該時鐘將在Tile間轉發,通過每個Tile內的PLL倍頻出所需的采樣時鐘;

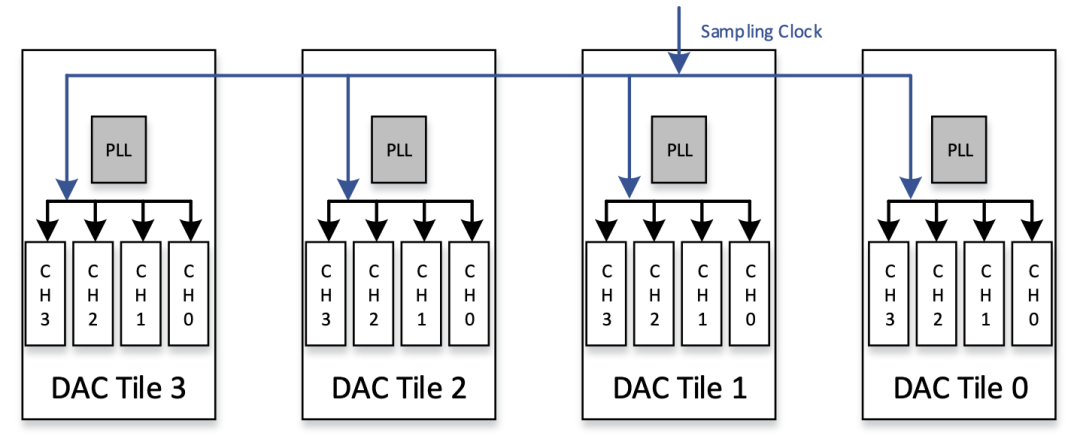

而采樣時鐘轉發有兩種途徑,一是從外部時鐘芯片直接提供低噪聲高頻的采樣時鐘到一個ADC/DAC Tile的專用時鐘管腳,采樣時鐘將在Tile間分發,無需通過內部PLL倍頻,直接提供給ADC/DAC Channel作為采樣時鐘;

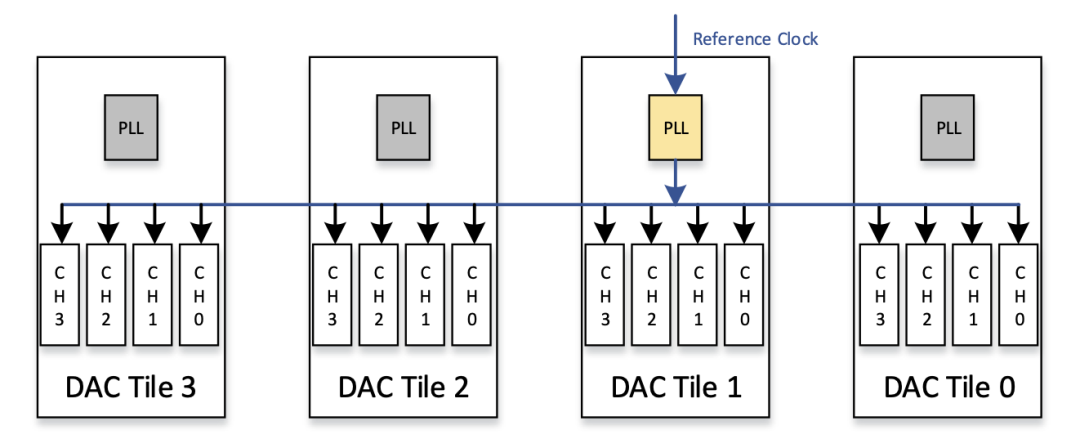

時鐘芯片提供低噪聲低頻時鐘到一個ADC/DAC Tile的專用時鐘管腳,該時鐘在此Tile內通過PLL倍頻到采樣頻率,隨后將此采樣時鐘在Tile間分發。

以上僅為時鐘分發方式的簡化解釋,會有一些使用的限制和建議,建議用戶參考PG269 Chapter 4 Clocking-On-chip Clock Distribution章節閱讀。

用戶也可以打開Vivado,選擇器件型號后在RF Data Converter IP內根據原理圖和目標設計進行配置,如果時鐘設計存在問題,工具會給予一定的報警和提示。

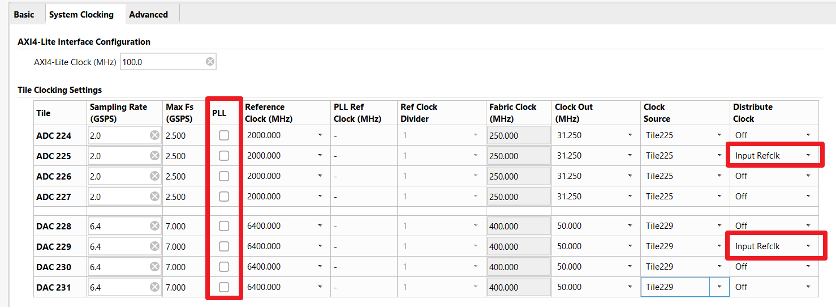

值得注意的是,RF Data Converter IP內的選項和上述的兩種分發方式不是完全匹配的。當使用采樣時鐘分發方式時,在IP內需要勾選的是Input Refclk。ADC Tile 1(Tile 225)和DAC Tile 1(Tile 229)作為采樣時鐘輸入源,其他的ADC和DAC Tile選擇Tile 1作為時鐘源。

2. ZCU216時鐘結構及可行的時鐘設計方案:

本節僅覆蓋ZCU216開發板與RF數據轉換器相關的時鐘部分,這部分時鐘均由擴展子卡CLK104提供。

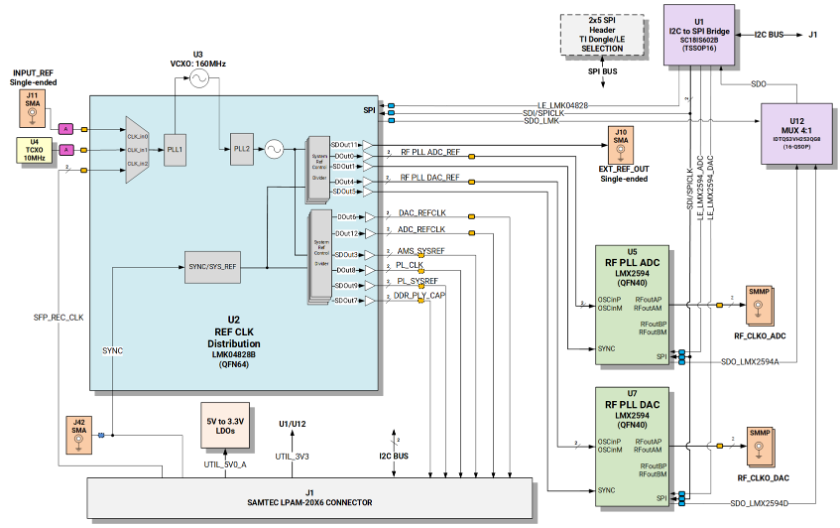

如下所示為CLK104板上的功能示意圖:

通過一個時鐘芯片為DAC提供接近10GSPS的低噪聲采樣時鐘是很難實現的,CLK104板采用兩級PLL方案。

第一級LMK04828B是一個雙環路抖動清除器和時鐘發生器,一級回路的參考輸入可為板上的10MHz TCXO、外部參考時鐘(比如從SMA100B輸出低噪聲時鐘),或SFP恢復時鐘。二級回路的參考輸入為板上的160MHz VCXO,可輸出低相噪的時鐘、同步信號。其中DAC_REFCLK和ADC_REFCLK可作為ADC/DAC低頻參考時鐘輸入;PL_CLK,AMS_SYSREF和PL_SYSREF均用作MTS(Multi-Tile Synchronization)應用,我們將在未來博客中詳細描述MTS相關應用;

第二級LMX2594接收第一級輸出時鐘,將其倍頻到采樣頻率,直接輸出到ADC/DAC Tile。

這三顆時鐘芯片均由SPI接口控制,板上有一顆IIC to SPI橋接芯片,FPGA通過IIC接口對此轉換芯片進行控制,進而控制三顆時鐘芯片。除此以外還有一種更為簡單的方式,ZCU216板上帶有一顆TI的MSP430 MCU,其IIC接口通過IIC Switch也可以連接到這幾顆時鐘IC上,用戶可以參考XTP580,使用BoardUI實現對時鐘的配置。

ZCU216上的芯片型號為ZU49DR,其4個ADC Tile和4個DAC Tile都有專用的模擬時鐘輸入管腳,但只有兩個ADC Tile(Bank 225/226)和兩個DAC Tile(Bank 229/230)的時鐘管腳被引出。如下表所示為詳細連接關系:

本文后續將會展示以下的時鐘方案配置:

使用LMX2594輸出高頻采樣時鐘分發方式,從ADC Tile1和DAC Tile1輸入。設定ADC 采樣頻率為2000MHz,DAC采樣頻率為6400MHz。

3. 在Vivado中創建基于IP集成器(IP Integrator)的設計

本節需要讀者對基于Vivado的IPI設計比較熟悉,將不會對較簡單的操作步驟進行詳述。如何使用此Blog提供的TCL文件重建Vivado工程請參考附錄。

? 打開Vivado 2021.2,新建工程,名為rfsoc_zcu216_clocking。

?選擇板卡ZCU216 EVB或ZCU216 ES EVB,根據板卡型號決定,二者bitstream不兼容。

? 在工程界面內創建Block Design,默認名為design_1。

?添加Zynq UltraScale+ MPSoC IP,Run Block automation,使用板卡默認配置。

? 修改Zynq配置,PS-PL Configuration界面下將AXI HPM0/1 FPD接口關閉,勾選AXI HPM0 LPD,其他保持默認。

? 添加Zynq UltraScale+ RF Data Converter IP。

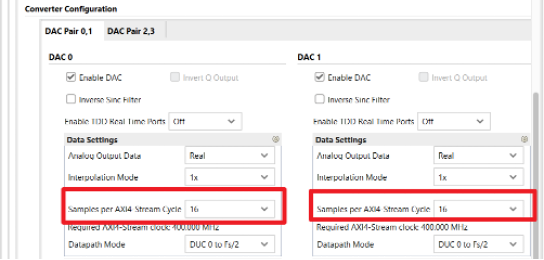

? 修改RF Data Converter配置。

1. 切換Converter Setup為Advanced模式。

2. 使能全部ADC和DAC的每個Channel,其他所有配置大多數都是可以通過API修改的,保持默認即可,后續將會介紹如何通過API修改。

3. 修改全部ADC的Samples per AXI4-Stream Cycle為8,DAC為16,這是為了避免AXI-Stream接口時鐘頻率超出器件頻率上限。

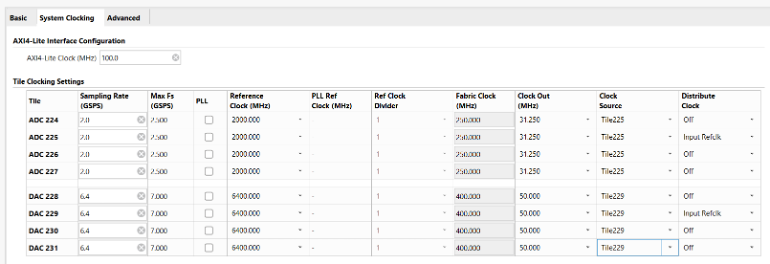

4.在System Clocking界面按下圖配置,如上一節所示,我們將先按ADC 2GSPS,DAC 6.4GSPS進行配置,使用采樣時鐘分發方式。IP的輸出時鐘可以用于倍頻產生AXI4-Stream數據接口的時鐘,因此我們先保持和Fabric clock 頻率8分頻的關系進行配置。

5. Advanced界面保持默認,無需勾選。

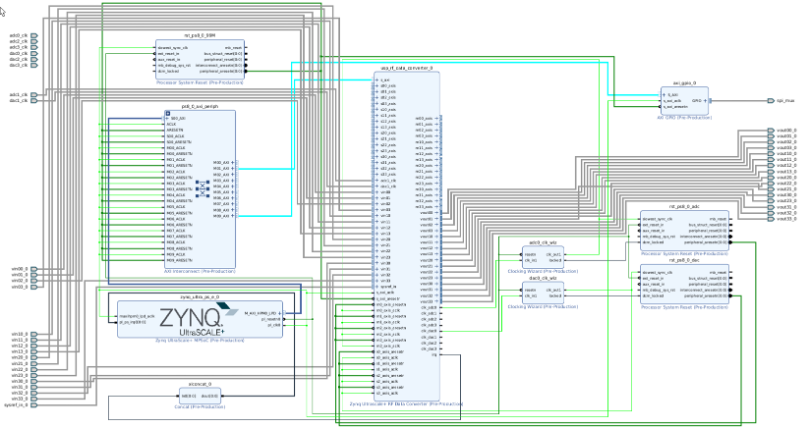

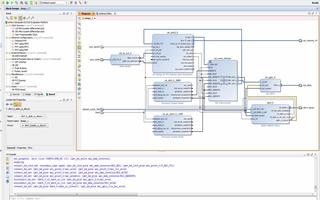

? Run Block Automation,將RFDC IP AXI-Lite接口通過Interconnect連接到Zynq LPD接口實現地址映射。

? 為AXI4-Stream接口提供合適的時鐘和復位。

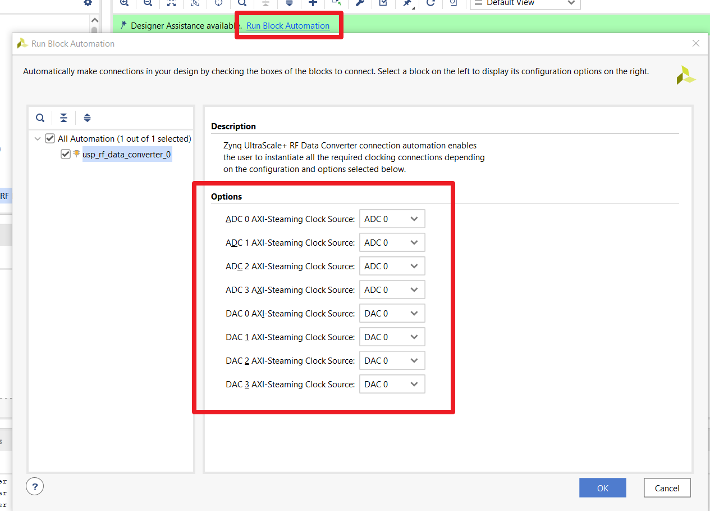

1. 點擊BD界面上方Run Block Automation。

2. 由于所有ADC/DAC采樣率是一致的,可以使用一個MMCM產生ADC/DAC所需的數字時鐘。在彈出界面中勾選ADC 0-3的時鐘源為ADC0,DAC0-3的時鐘源為DAC0。

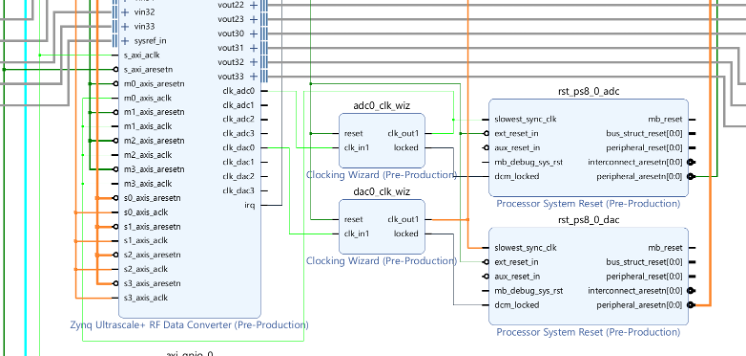

3. 工具將會自動例化兩個Clocking Wizard IP,adc0_clk_wiz使用IP輸出的31.25MHz的時鐘作為輸入,倍頻輸出200MHz時鐘供給Master接口。Dac0_clk_wiz使用IP輸出的50MHz時鐘作為輸入,倍頻輸出400MHz時鐘供給給Slave接口。

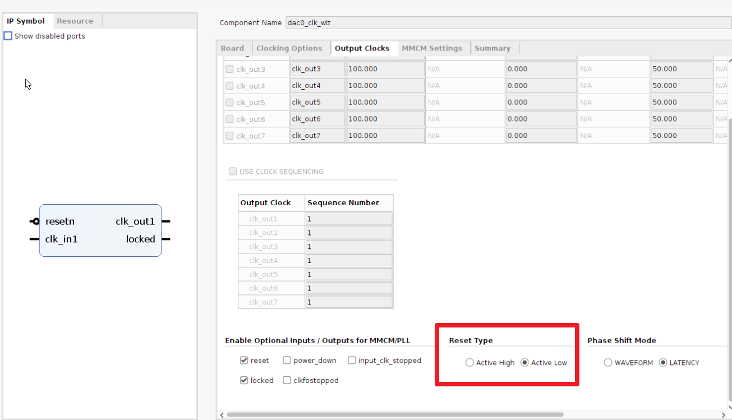

4. 修改clocking wizard復位極性為低電平有效。

5.例化兩個Processor System Reset IP,并連接peripheral_aresetn到RFDC IP的s/m_axis_aresetn管腳上。其中Slave AXI-Stream接口是DAC的數字接口,Master AXI-Stream是ADC的數字接口。

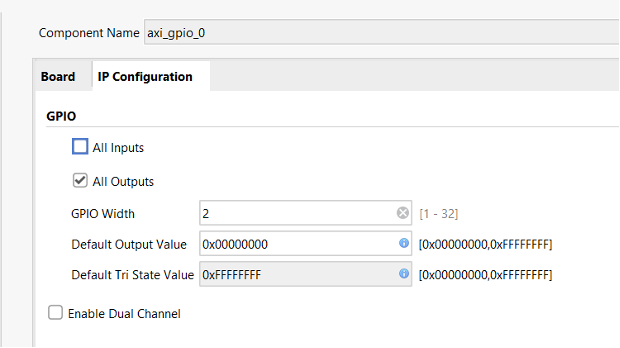

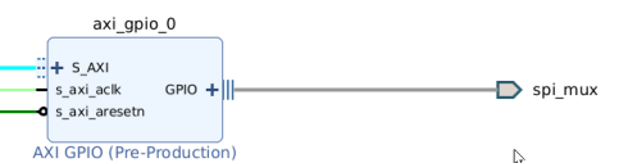

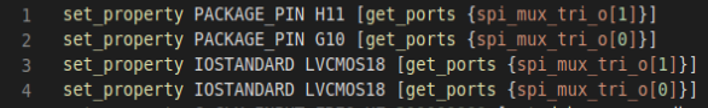

6. 例化一個AXI GPIO IP,用于控制時鐘板CLK104上的SPI SDO選通。設定為輸出,位寬為2,初始值設定為0x0。

7. 引出AXI GPIO IP,命名為spi_mux。

? 完整的Block Design大致如下:

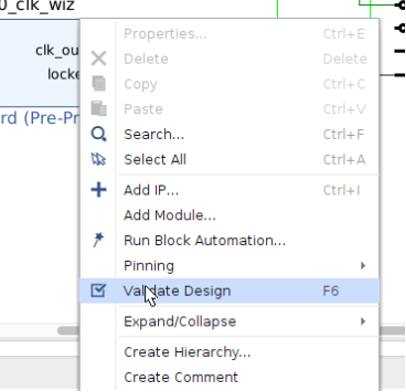

? 在BD中右鍵Validate design,確保沒有報錯。

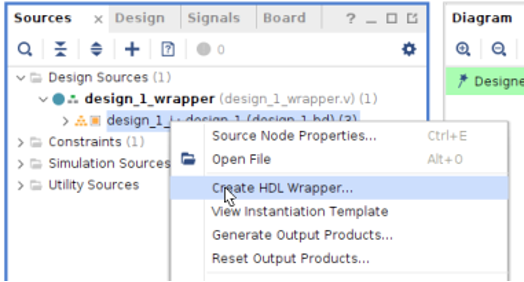

? 創建頂層文件,右鍵BD,Create HDL Wrapper,選擇Let Vivado manage wrapper and auto-update。

? 添加管腳約束,RFDC相關管腳為專有管腳,IP內包含管腳約束,用戶無需為此添加。

? 生成bitstream,檢查工程是否有時序違例。

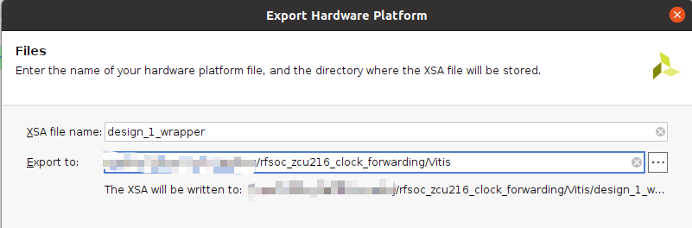

? 導出工程XSA文件,File-Export-Export Hardware,勾選Include Bitstream,選擇導出目錄。

原文標題:開發者分享|第三代Zynq RFSoC器件射頻數據轉換器應用: 時鐘設計-上

文章出處:【微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

-

Xilinx

+關注

關注

71文章

2163瀏覽量

121005 -

Vivado

+關注

關注

19文章

808瀏覽量

66324 -

IP集成器

+關注

關注

0文章

4瀏覽量

5796 -

RFSoC

+關注

關注

0文章

28瀏覽量

2722

原文標題:開發者分享|第三代Zynq RFSoC器件射頻數據轉換器應用: 時鐘設計-上

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

創建AXI Sniffer IP以在Vivado IP Integrator中使用教程

Vivado 2013.1和Zynq需要及早訪問Vivado IP集成商是什么意思?

Vivado環境下如何在IP Integrator中正確使用HLS IP

Northwest Logic支持Xilinx IP集成器工具流

在IP集成器中調試AXI接口有哪些優勢?

賽靈思Vivado設計套件推出2013.1版本,提供IP 集成器和高層次綜合功能

如何讓Vivado IP Integrator和Amazon F1開發套件進行協同使用

如何使用Vivado Design Suite IP Integrator的調試AXI接口

如何使用Vivado IP Integrator組裝具有多個時鐘域的設計

如何使用IP Integrator創建硬件設計

在Vivado中創建基于IP集成器(IP Integrator)的設計

在Vivado中創建基于IP集成器(IP Integrator)的設計

評論