詳細流程:

? 打開Vitis,選擇一個Vitis工作目錄。

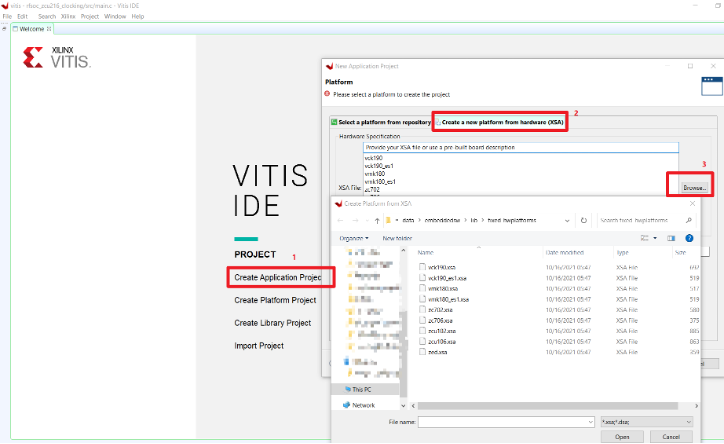

? Create Application,選擇一個新的XSA文件,導入從Vivado獲得的XSA文件。

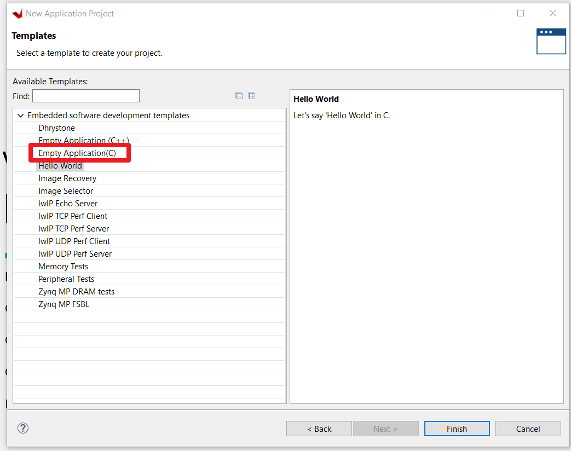

?為工程取一個名,以Empty Application(C)為模板新建工程。

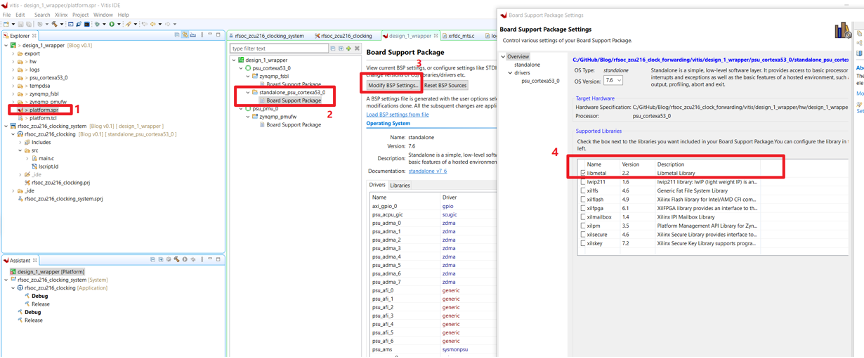

?勾選BSP中的庫,雙擊platform.spr,選中standalone_psu_cortexa53_0下的Board Support Package,選擇Modify BSP Settings,勾選libmetal庫,保存。

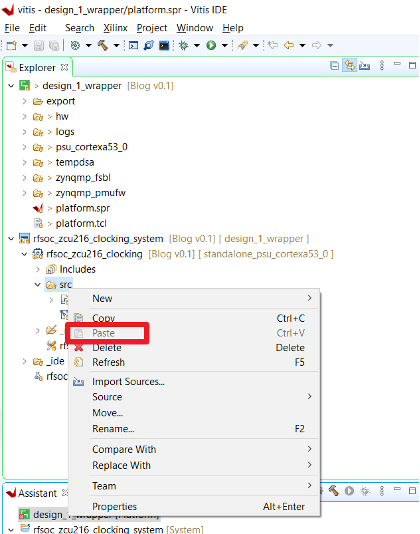

? 導入源碼,從附件中找到main.c,可以直接拷貝到工程src目錄下,或者右鍵src目錄選擇Import sources。

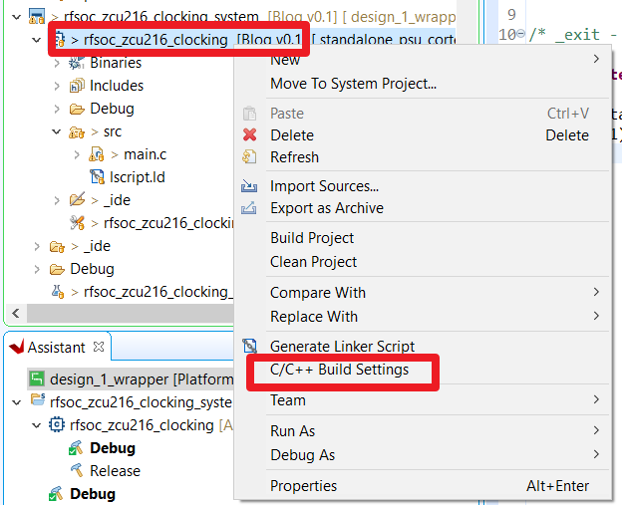

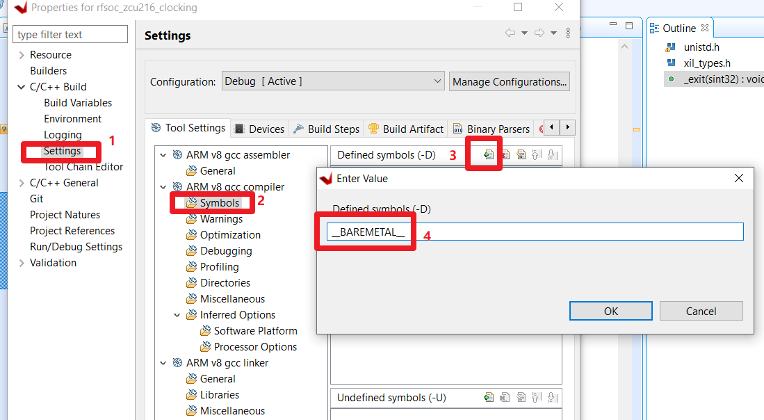

? 添加工程Symbol。右鍵工程選擇C/C++ build settings,在Symbols中添加__BAREMETAL__。

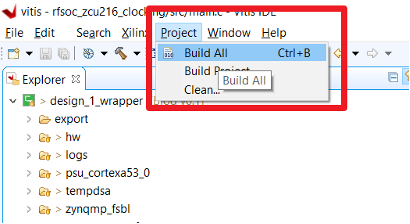

? 編譯工程,如果有宏定義相關報錯,應該是底層IP命名問題,可以在xparameters.h中找到實際的宏定義。

如何添加metal log:

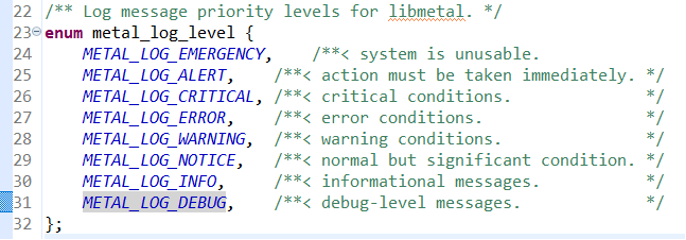

Libmetal庫提供了metal_log API以便于用戶調試,用戶可以參考AR#71068使能打印功能:

https://support.xilinx.com/s/article/71068

Metal_log提供了8個等級的打印信息,用戶可以根據項目所處的不同階段決定開啟哪一個等級的調試信息。

代碼簡要分析:

整體流程大致如下:

1. Libmetal初始化。

3. IIC/GPIO/SPI Mux初始化。

4. CLK104時鐘IC復位。

5. CLK104時鐘配置。

6. 設置RFDC Clock Distribution。

7. 查看RFDC IP狀態。

這里主要強調一下三個部分,一是時鐘配置,二是Clock Distribution,三是狀態檢查。

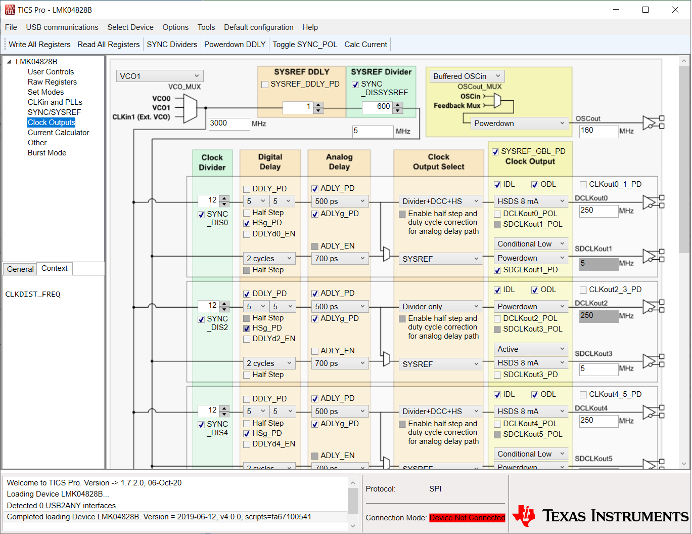

如前面章節所說,FPGA通過IIC接口與IIC to SPI橋接芯片進行交互,橋接芯片通過SPI接口控制時鐘IC。配置數據在本案例中是記錄在數組中的,數據來源于TI的TICS Pro軟件。用戶需要根據實際的需求,在軟件中選擇時鐘IC的輸入輸出頻率和管腳復用,由軟件導出一組針對此時鐘IC的寄存器數值。

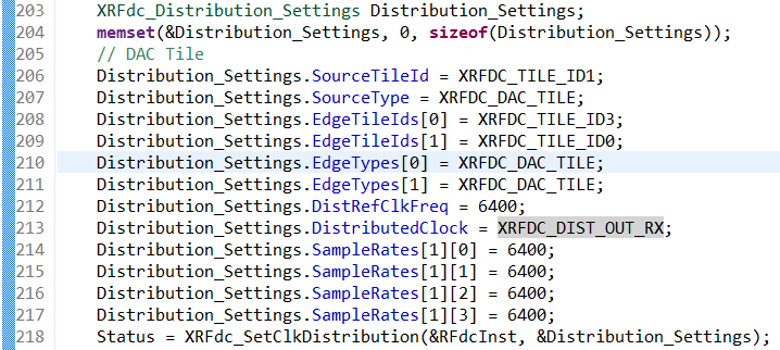

Clock Dsitribution部分,IP驅動提供了相關的結構體和API,具體組成部分可以參考PG269文檔相關部分。以下是DAC Tile的時鐘分發網絡配置代碼:

在我們目前的設計中,使用LMX2594產生的高頻參考時鐘輸入到DAC Tile1,因此結構體中指定source tile為XRFDC_TILE_ID1;此時鐘分發組內最北的是DAC Tile3,最南的是DAC Tile0;分發類型是參考鐘分發,因此選擇XRFDC_DIST_OUT_RX;參考鐘頻率為6400,采樣率為6400;將此結構體傳入到XRFdc_SetClkDistribution函數中,函數內部會檢查當前配置是否有效,并在配置結束以后啟動tile。

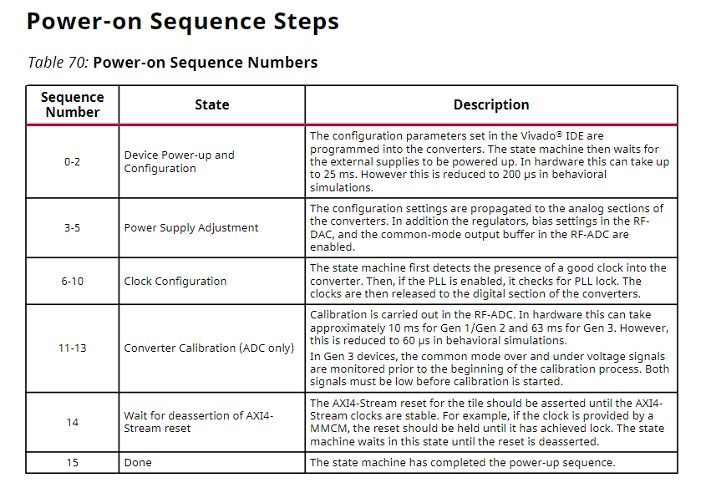

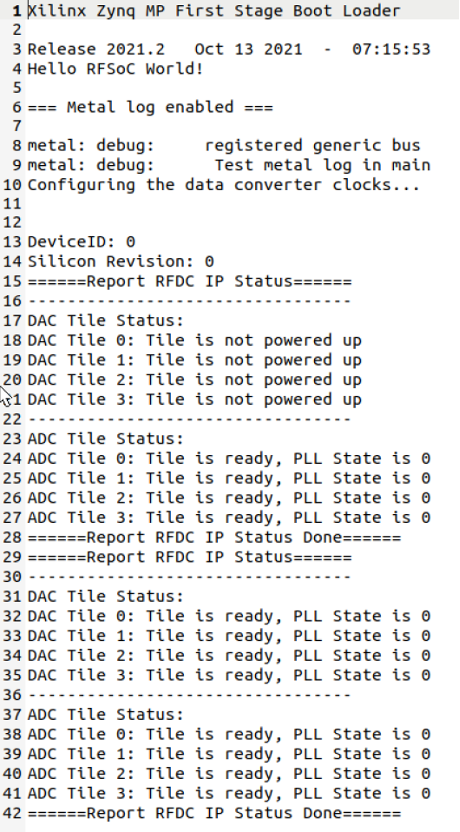

檢查IP狀態是最后一步,IP啟動過程共有15個階段,只有當Tile狀態達到0xf的時候說明此Tile正常啟動,接下來可以正常工作,如果發現Tile狀態停在某一步,可以對照PG269 Power-on Sequence Steps章節查找原因。

硬件環境及測試結果:

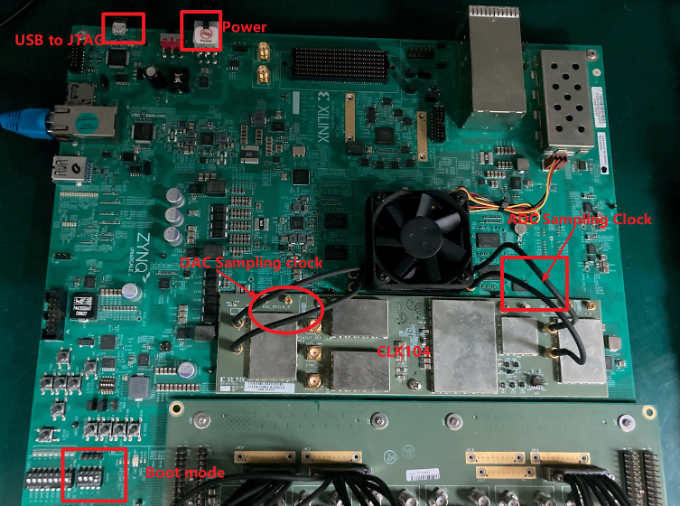

建議按照XTP587完成板子硬件環境setup:

2. 安裝CLK104時鐘板。

3. 使用出廠自帶的CARLISLE連接線,將CLK104 ADC/DAC參考鐘接到板上。

4. 設置啟動模式為JTAG。

測試結果:

由打印的IP status對比可見,時鐘成功配置,所有DAC和ADC Tile均進入到狀態0xf。

附錄:

此文章提供重建工程TCL腳本,用戶可以下載附件,按照如下步驟重建Vivado工程:

1. 打開Vivado 2021.2。

-對Windows系統,雙擊桌面Vivado圖標或到此目錄尋找執行文件C:XilinxVivado2021.2invivado.bat。

- 對Linux系統,source/settings64.sh。

2. 在Vivado console中,將當前目錄更換到下載的附件目錄。Cd。

3. Source ./vivado_project.tcl。

Vitis工程需要用戶自行創建,本文會提供測試源代碼。

原文標題:開發者分享|第三代Zynq RFSoC器件射頻數據轉換器應用: 時鐘設計-下

文章出處:【微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

-

ARM

+關注

關注

134文章

9046瀏覽量

366817 -

程序設計

+關注

關注

3文章

261瀏覽量

30367 -

Vitis

+關注

關注

0文章

145瀏覽量

7405

原文標題:開發者分享|第三代Zynq RFSoC器件射頻數據轉換器應用: 時鐘設計-下

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用Vitis HLS創建屬于自己的IP相關資料分享

基于ARM的BSP程序設計方案

ARM的位置無關程序設計在Bootloader中的應用

ARM處理器的位置無關程序設計

Xilinx Vitis能創建的模板軟件工程

怎么在Vitis加速設計中為Kernel創建面積約束

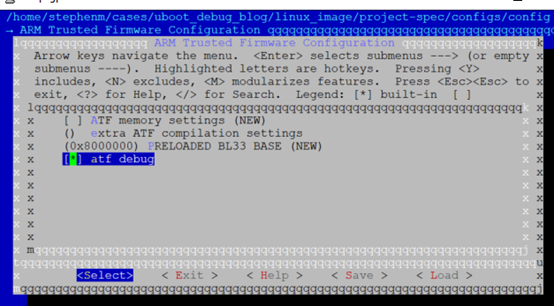

在Vitis中調試ARM可信固件和U-boot

在Windows 10上創建并運行AMD Vitis?視覺庫示例

在Vitis中創建基于ARM的BareMetal程序設計

在Vitis中創建基于ARM的BareMetal程序設計

評論