1. 塊語句有兩種,一種是 begin-end 語句, 通常用來標志()執(zhí)行的語句;一種是 fork-join 語句,通常用來標志()執(zhí)行的語句。

答案:順序,并行

解析:

(1)begin_end順序塊,用于將多條語句組成順序塊,語句按順序一條一條執(zhí)行(除了帶有內(nèi)嵌延遲控制的非阻塞賦值語句),每條語句的延遲時間是相對于由上一條語句的仿真時間而言;

(2)fork-join并行塊,塊內(nèi)語句同時執(zhí)行。

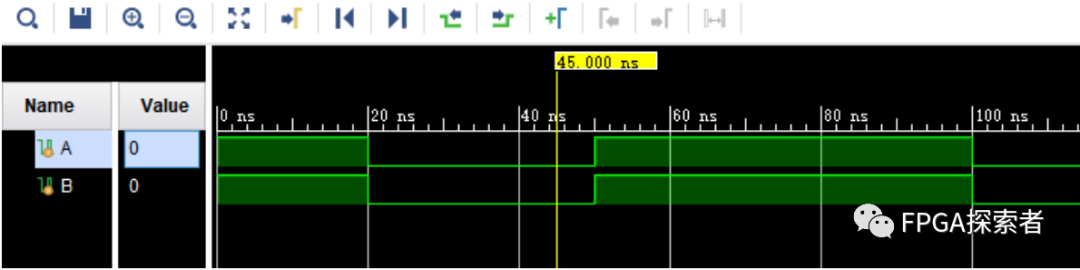

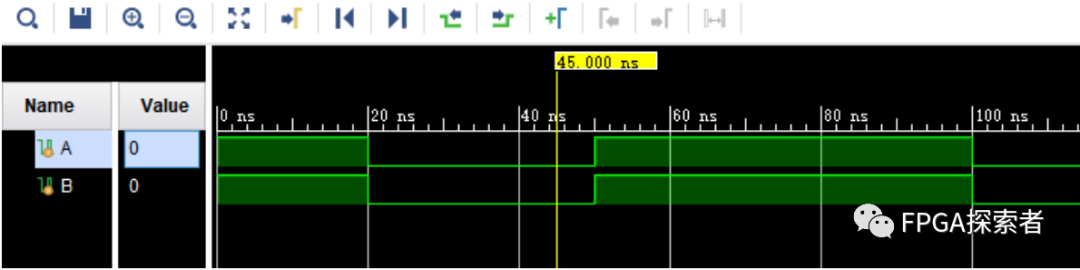

2. 塊語句,下面這段語句中,第 40 時刻上,A、B 的值各是多少?

reg A;reg B;initial begin fork begin A = 1; #20 A = 0; #30A=1; #50 A = 0; end begin B = 1; #20 B = 0; #30 B = 1; #50 B = 0; end joinend

答案:A = 0,B = 0

解析:

塊語句有兩種,begin...end 和 fork...join,其中 fork...join 是并行塊,begin...end 是順序執(zhí)行塊,可以相互嵌套。

上面,兩個 begin...end 之間是并行的,而各自 begin...end 內(nèi)部是順序執(zhí)行,A 和 B 的賦值邏輯是一樣的,所以要么都是 1,要么都是 0。

按照順序執(zhí)行,A 前 20 個時間單位是 1,然后持續(xù) 30 個時間單位的 0,所以 40 時刻是 0,同理 B 也是 0。

審核編輯 :李倩

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標題:Verilog 的塊語句 fork...join 和 begin...end

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

本文繼續(xù)介紹Verilog HDL基礎(chǔ)知識,重點介紹賦值語句、阻塞與非阻塞、循環(huán)語句、同步與異步、函數(shù)與任務(wù)語法知識。

![的頭像]() 發(fā)表于

發(fā)表于 10-24 15:00

?181次閱讀

MX_GPIO_Init初始換函數(shù)結(jié)尾沒有begin end用戶編輯區(qū)域,但是在其他初始化函數(shù)后有編輯區(qū)域,并且在main.c文件每個初始化后方也沒有用戶編輯界面,如果想要在初始化結(jié)尾做一些事情,在

發(fā)表于 09-26 06:08

... default ... endcase

7、連續(xù)賦值:assign, 問號表達式(?:)

8、always模塊:敏感表可以是電平、邊沿信號

9、begin...end(代碼塊?)

10、任務(wù)定義

發(fā)表于 06-23 14:58

,因為always語句塊是并行執(zhí)行的,會產(chǎn)生沖突。

always@(敏感信號)begin

語句;

end

②、assign和always

發(fā)表于 05-31 18:31

條件語句用于基于不同的條件來執(zhí)行不同的動作。

TypeScript 條件語句是通過一條或多條語句的執(zhí)行結(jié)果(True 或 False)來決定執(zhí)行的代碼塊。

![的頭像]() 發(fā)表于

發(fā)表于 04-01 13:51

?712次閱讀

state_next = START;

data_out[9:8] = 2\'b10; // K28.5

end

end

START: begin

state_next = DATA;

data_out[2:0

發(fā)表于 03-26 07:55

else begin

data_a_reg <= data_in_a;

data_b_reg <= data_in_b;

end

end

// 執(zhí)行卷積運算

always

發(fā)表于 03-26 07:51

;lt;= 0;

end else begin

if (sec_cnt == MAX_SECONDS) begin

sec_cnt <= 0;

if (min_cnt

發(fā)表于 03-26 07:48

, mantissa} = a; // 將a中的符號位、指數(shù)部分和尾數(shù)部分提取到對應變量中

end

always @(posedge clk) begin

if (reset == 1\'b1) begin

sum

發(fā)表于 03-25 21:49

Verilog中的模塊端口對應方式,并提供示例代碼和詳細解釋,以幫助讀者更好地理解和應用。 首先,我們來了解一下Verilog中的模塊和模塊端口。一個Verilog模塊被定義為包含一組聲明和語

![的頭像]() 發(fā)表于

發(fā)表于 02-23 10:20

?1641次閱讀

在Verilog中,repeat語句不需要使用begin和end塊。repeat語句是一種循環(huán)控

![的頭像]() 發(fā)表于

發(fā)表于 02-23 10:14

?1104次閱讀

Assign語句和Always語句是在硬件描述語言(HDL)中常用的兩種語句,用于對數(shù)字電路建模和設(shè)計。Assign語句用于連續(xù)賦值,而Always

![的頭像]() 發(fā)表于

發(fā)表于 02-22 16:24

?2291次閱讀

Verilog是一種硬件描述語言(HDL),用于設(shè)計和模擬數(shù)字電路。在Verilog中,關(guān)鍵字initial和always都是用于描述電路行為的特殊語句。它們被用來生成仿真模型,并控制模擬器的啟動

![的頭像]() 發(fā)表于

發(fā)表于 02-22 16:09

?2463次閱讀

單片機中的if語句是一種條件語句,用于根據(jù)不同的條件執(zhí)行不同的代碼塊。在程序執(zhí)行過程中,條件語句用來決定是否執(zhí)行特定的代碼段。在單片機編程中,if語

![的頭像]() 發(fā)表于

發(fā)表于 01-05 14:04

?1637次閱讀

Java中的switch語句是一種用于多重條件判斷的語句,用于根據(jù)不同的條件執(zhí)行不同的代碼塊。在switch語句中,case關(guān)鍵字用來指定不同的取值。 在Java中,switch

![的頭像]() 發(fā)表于

發(fā)表于 11-30 16:05

?1083次閱讀

Verilog的塊語句fork...join 和 begin...end

Verilog的塊語句fork...join 和 begin...end

評論