在當今的數字設計世界中,速度通常是決定產品性能的主要因素。許多設計都包含太多高速接口,其信號速度足夠高,以至于印刷電路板 (PCB) 的走線和布局在整體系統性能中發揮著重要作用。

因此,信號完整性和電源完整性問題往往是各個產品設計階段設備故障的主要原因。除了數字部分之外,設計工程師還應謹慎考慮高速 PCB 設計的模擬特性。必須考慮可能增加數字波形時序不確定性的任何物理現象。

當實施明確定義的 PCB 路徑時,可以實現信號完整性 (SI)。這些路徑允許在正確的時間以干凈的邊緣將信號從驅動器傳送到接收器。SI 較差的設計通常無法滿足時序或抖動要求。在某些情況下,較差的 SI 也可能導致高于可接受的輻射發射。在最壞的情況下,設計根本不起作用。

讓我們討論實現高速 SI 的關鍵設計考慮因素。首先是高頻下的傳輸線行為。在電子產品的早期,由于邊緣速率較慢,SI 并不是一個問題。隨著時鐘速率和信號速度的增加,上升時間因此減少到 PCB 走線長度與通過它們的邊沿速率處于相同長度的點。對于具有 2.97-Gbit/s 數據速率的 HDMI 1.4 信號,關鍵 PCB 長度為 2 mm。因此,必須仔細分析高速 PCB 的傳輸線及其特性阻抗、延遲和損耗。這些傳輸線行為是確定連接組件如何交互的關鍵。最常見的傳輸線阻抗是 50 Ω。

與 PCB 制造廠的溝通決定了 PCB 材料、疊層以及每層中走線寬度/間隙的識別,以滿足所需的阻抗。PCB設計中使用的兩種常見傳輸線類型是帶狀線和微帶線。

帶狀線的信號跡線夾在兩個參考平面之間。微帶線的信號線走線在外層,只有一個參考平面。兩者之間的選擇取決于信號速度要求、設計復雜性以及驅動器 IC 的扇出布置。一般來說,帶狀線不太容易受到噪聲的影響,而微帶線提供更快的信號速度路徑。

一旦定義了 PCB 材料、疊層和傳輸線類型,設計人員就需要決定如何路由高速信號。在考慮信號走線時,重要的是選擇一條干凈且短的走線,其下方有一個未中斷的參考平面。這讓電流以一致的阻抗傳輸到接收器,并通過阻抗最小的路徑返回到源,該路徑是與信號跡線直接相鄰的參考平面。常見的返回路徑問題包括 (a) 當參考平面中存在不連續性時和 (b) 當路由信號改變層時沒有參考平面跟隨。上述中斷返回路徑的后果是信號反射和振鈴。

信號反射和振鈴是信號完整性設計不佳的直接結果。驅動器、傳輸線和接收器阻抗都可能導致信號反射。如果信號在向下傳播時遇到 PCB 瞬時阻抗的變化,部分信號將反射回其源并導致信號失真。這種瞬時阻抗的變化稱為阻抗不連續性。當由于阻抗不連續而出現多次反射時,就會出現振鈴。如果驅動器、互連傳輸線和接收器具有相同的阻抗,則不會出現反射或振鈴。因此,在元件和互連之間匹配相同的阻抗是減少振鈴的關鍵。

串擾是由于 PCB 走線的電容和電感特性導致的信號耦合造成的,它可能是由于多個信號相互耦合而造成的,因為它們的布線太近或信號返回路徑彼此太近。當布線走線和返回路徑與其他信號走線的距離是走線寬度的兩倍時,可以最大限度地減少串擾。振鈴也會導致串擾的可能性;較少的振鈴轉化為較少的串擾。

雖然這里沒有討論,但終端拓撲、走線的長度、信號的傳播速度和走線的形狀都需要考慮。

以下是維護 SI 應遵循的實用設計規則的摘要:

在原理圖設計期間識別所有高速信號。

如果可能,在頂層和底層布線最高速度的信號。

每個高速連接都必須被視為傳輸線對的一部分,以 100 或 90 Ω 差分對和 50 Ω 單端方式布線。

將信號跡線與返回路徑保持一層電介質。任何偏離此值的行為都會增加輻射發射、降低信號完整性并降低抗擾度。

始終為高速信號提供良好的接地參考。

避免返回路徑不連續,例如參考平面中的空隙。

如果高速信號過渡層和改變接地參考平面,則必須在信號過孔旁邊放置一個返回過孔。

對于差分布線,在信號及其返回路徑方面盡可能保持正負走線平衡,并滿足線對內和線對間長度匹配要求。

保持線對間距大于 2 倍的線寬規則。

與其他接口保持大于 3 倍的線寬間距。

沒有直角轉彎,因為它們會在跡線上增加電容。

盡量減少高速信號走線的過孔(層轉換)數量。

盡量減少沿高速信號走線的任何短截線,包括從通孔引入的短截線。

通過使高速信號遠離嘈雜的信號、時鐘和開關模式電源來保護它們。

電源完整性

電源完整性 (PI) 是通過在系統內部提供符合處理器和所有其他組件所需電源條件的電源傳輸網絡 (PDN) 來實現的。PDN 是傳輸平面形式的互連鏈,通過 PCB、封裝和片上路由從穩壓器模塊 (VRM) 向晶體管本身供電。

PI 比 SI 更難可視化,事實證明,有數十個和數百個節點連接在同一電源平面中,每個節點都會影響 PDN 中的整體阻抗,而 SI 僅處理驅動器和接收器。PI 問題難以重復和排除故障。因此,建議在布局前和布局后 PCB 設計階段進行完整的 PI 研究。雖然完整的 PI 分析需要高級且通常昂貴的 PI 仿真工具,但我們將在此處堅持設計基礎。

高速數字設計中的良好 PI 系統有兩個基本目的。首先,它為交換信號提供穩定的電壓參考(接地/返回路徑)。其次,它以可接受的噪聲和容差將電源分配給所有邏輯器件,以保持芯片焊盤上的電壓恒定。

聽起來很簡單,但在高速 PCB 設計中需要實現一些事實。首先,典型的 BGA 處理器通常有數百個電源和接地球,需要數十個電源電壓。其次,所有這些電源引腳都消耗許多安培的電流。因此,當器件工作時,所有這些消耗安培電流的電源引腳同時加載所有高頻電源電壓。

考慮到這一點,PI 研究不再只是單純的直流分析,而是涉及從 VRM 到 IC 焊盤的每個電源軌中高頻瞬態負載的研究。

電源完整性的基本設計考慮從高頻傳輸平面行為開始。與 SI 的傳輸線類似,PI 分析的關鍵是將所有電源軌視為傳輸平面并分析其特性阻抗。為了實現良好的電源完整性,希望 PDN 具有盡可能低的阻抗。可能會產生高頻瞬態噪聲,如果被忽視,可能會傳播到整個電路板。

主要挑戰是 PCB 中的 PDN 互連都具有電感特性。元件安裝、PCB 走線、電容器和過孔都表現出電感。這表明阻抗隨著瞬態頻率的增加而增加。由于 VRM、電容器、PCB 疊層、電源/接地層和 IC 在不同頻率下都有不同的特性阻抗,因此仔細選擇元件和放置位置是降低傳輸層阻抗的方法。

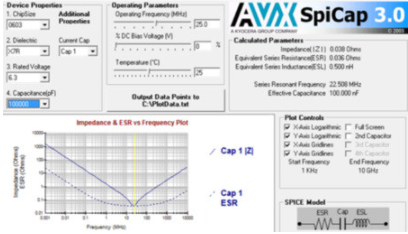

圖 1 和圖 2 展示了電容器在高頻下的電感特性以及典型 PDN 的等效電路。圖 1 是使用 AVX 的 SpiCap 仿真工具的 0603、X7R、1-uF 電容器阻抗與頻率圖的示例。圖的左半部分顯示電容在 0 到 22.5 MHz 之間的特性阻抗中占主導地位,右半部分顯示電感在大于 22.5 MHz 的頻率中占主導地位。

1. 0603、X7R、1-uF 電容器的阻抗與頻率圖示例。

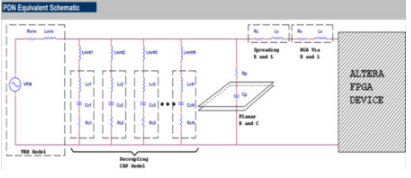

圖 2 是一個 PDN 等效電路,說明了同一傳輸平面的每個互連的電阻、電容和電感特性。所有這些物理現象都需要作為 PI 分析的一部分進行深入研究。

2. 顯示的是從 Altera 的 PDN 工具捕獲的典型傳輸平面的 PDN 等效原理圖。

理想情況下,我們希望使整個傳輸平面的阻抗盡可能低。由于許多因素會影響阻抗,因此需要為電路板上所有芯片的每個電壓軌單獨且獨立地計算目標阻抗。在每個電源軌中,由于芯片的特定電流要求,目標阻抗可能隨頻率而變化。在指定目標阻抗時,應將器件規格表中列出的每個導軌的阻抗和可接受的容差信息用作起始指南。

特定傳輸平面的 PDN 由不同的互連塊組成,從 VRM 到大容量去耦電容器,再到通孔,再到電路板上的走線和平面。然后是額外的去耦帽、封裝的焊球或引線、封裝中的互連以及芯片上的焊線和互連。每個互連塊都有助于傳輸平面的特性阻抗。在分析 PDN 時,首先要研究每個互連軌道,然后是傳輸平面,然后是整個 PDN 系統。

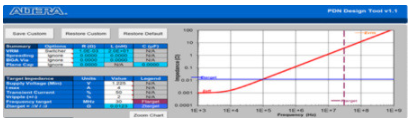

Altera PDN 設計工具可以說明每個 PDN 互連對不同頻率帶寬中同一傳輸平面的特性阻抗的影響。該工具可以通過 Altera 的有效 Quartus II 軟件許可證下載。通過將目標阻抗設置為 12.3 mΩ 開始設計過程,然后通過每個 PDN 互連。

低頻阻抗,范圍從直流到 10 kHz,由 VRM 設置。VRM 輸出通常為毫歐級,從 DC 到 10 kHz。

3. 顯示的是 VRM 特性阻抗。

VRM PCB 布局需要考慮的實用技巧是:

最大化金屬厚度。

使用足夠寬的電源走線。

使用多個并行的電源和接地過孔。

與 VRM 并聯的大容量電容器可將阻抗降低 10 至 100 kHz。

4. 顯示的是大容量電容器的特性阻抗。

選擇合適的大容量電容器的實用技巧是:

遵循大容量電容器值的參考設計。

遵循設計指南以優化大容量電容器的放置。

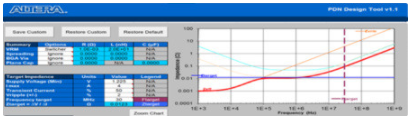

去耦電容可將傳輸層的阻抗降低 0.1 至 10 MHz。在靠近電源焊盤的入口點添加去耦電容可降低環路電感。選擇正確的位置并選擇正確數量和值的去耦電容器在這里起著重要作用。

5. 顯示的是去耦電容特性阻抗。

選擇正確的去耦電容的實用技巧是:

設計電容器值、主體尺寸和放置以滿足阻抗規范。

降低電源接地環路面積以減少環路電感。

緊密堆疊的電源和接地可將 PDN 的特性阻抗提高 10 至 100 MHz。

6. 顯示的是 PCB 電源/接地層特性阻抗。

設計電源/接地層的實用技巧是:

電源層和接地層應盡可能靠近。

放置多個用于電源和接地的過孔。

通常,對于 25 MHz 以上的頻率,特性阻抗主要由 BGA 球、IC 封裝和片上電容的通孔決定。為了對此建模,需要更高級的仿真工具。

關于去耦電容和電源/接地層的其他一些注意事項是:

電流總是走阻抗最小的路徑。在這些高頻下,PDN 環路電感、電容值和連接到電源引腳的電容器的位置決定了阻抗。

本地去耦電容應盡可能靠近處理器電源和接地引腳。使用背面電容器時,每個電容器都應有自己的通孔直接連接到接地層和電源層。

電源和接地過孔和平面應盡可能靠近。

PI 的實用設計規則是:

在相鄰層上使用電源層和接地層,并使用盡可能薄的電介質。

在去耦電容焊盤和通向埋入式電源/接地層的通孔之間使用盡可能短且寬的表面走線。

將電容器放置在回路電感最低的地方。

使用 SPICE 模型來幫助選擇最佳數量的電容器及其值,以使阻抗曲線低于目標阻抗。

本地去耦電容必須盡可能靠近處理器引腳放置。

定向電容器以最小化環路電感。

在返回路徑中放置局部過孔。

由于每個數字設計中的時鐘速率和信號速度都更高,因此對 SI 和 PI 的關注對于設計性能良好的產品至關重要。盡管我將 SI 和 PI 解釋為單獨的主題,但它們密切相關,并且它們的問題可以相互影響。此外,經過仔細考慮 SI 和 PI 設計的高速 PCB 通常具有最小的電磁干擾問題。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17586瀏覽量

249492 -

處理器

+關注

關注

68文章

19165瀏覽量

229123 -

pcb

+關注

關注

4317文章

23006瀏覽量

396276

發布評論請先 登錄

相關推薦

信號和電源完整性基礎對于高速PCB至關重要

信號和電源完整性基礎對于高速PCB至關重要

評論