通用多核處理器已被推廣為網(wǎng)絡(luò)通信處理的解決方案。實際上,它們無法解決下一代網(wǎng)絡(luò)基礎(chǔ)設(shè)施所需的可擴展性、確定性和易于編程的問題。一種將多核處理器與網(wǎng)絡(luò)優(yōu)化加速器引擎和 C 可編程庫相結(jié)合的非對稱多核方法可應(yīng)對下一代網(wǎng)絡(luò)的挑戰(zhàn)。

實現(xiàn)確定性性能是網(wǎng)絡(luò)運營商確保跨各種流量配置文件和應(yīng)用程序的可靠性的關(guān)鍵要求。在單核、雙核或四核處理器上運行應(yīng)用程序時,多核處理器可以應(yīng)對性能挑戰(zhàn)。但是,當(dāng)擴展到八個或更多內(nèi)核時,性能擴展通常會降低。在某些情況下,八核提供的性能并不比四核好,而 16 核的運行速度實際上比八核慢。

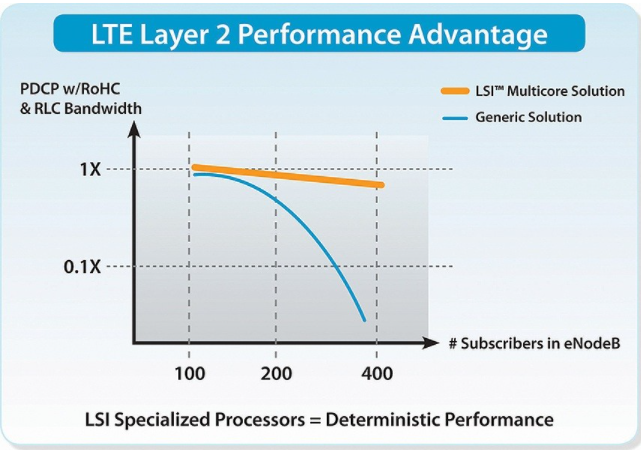

網(wǎng)絡(luò)應(yīng)用程序往往是數(shù)據(jù)密集型的,通用多核處理器極易受到內(nèi)存延遲對性能的影響。與內(nèi)存負載相關(guān)的內(nèi)存延遲的非線性(圖 1)與與內(nèi)存延遲相關(guān)的處理器性能的非線性相結(jié)合,可能導(dǎo)致不可預(yù)測和不可靠的性能。LSI 為解決這個問題而采用的創(chuàng)新方法是非對稱多核處理器,它將通用處理器與專用加速器相結(jié)合,用于特定的數(shù)據(jù)密集型任務(wù),從而形成一個最佳的、可擴展的解決方案。

圖 1:非對稱多核處理器通過結(jié)合通用處理器和加速器來解決內(nèi)存延遲的非線性問題,從而提高性能可預(yù)測性。

網(wǎng)絡(luò)基礎(chǔ)設(shè)施應(yīng)用程序往往涉及復(fù)雜的處理、密集的內(nèi)存利用率和實時的確定性要求。非對稱架構(gòu)通過在通用多核處理器和專用加速引擎之間無縫分配工作來應(yīng)對這些挑戰(zhàn)。這些加速器專門設(shè)計用于容忍內(nèi)存延遲并以可預(yù)測的方式執(zhí)行。這種方法還允許使用更少的通用多核處理器和更少的代碼行來構(gòu)建應(yīng)用程序。不對稱方法簡化了擴展挑戰(zhàn),并以更低的成本和功耗提供了更具確定性的性能。

網(wǎng)絡(luò)應(yīng)用程序需要靈活的操作系統(tǒng)方法。這種靈活性不僅是為了滿足應(yīng)用程序的要求,也是為了支持 OEM 傳統(tǒng)軟件的順利遷移,并使設(shè)計人員能夠為特定應(yīng)用程序選擇正確的操作系統(tǒng)。在不引入開銷的情況下同時支持不同內(nèi)核上的多個操作系統(tǒng)非常重要。在 LSI,我們的硬件和軟件從一開始就考慮到了這一切,為網(wǎng)絡(luò)應(yīng)用程序中使用的各種操作系統(tǒng)提供靈活的支持。

需要編譯器、模擬器和調(diào)試器等軟件工具來支持這些處理器。模擬器必須速度快,支持真實世界的吞吐量和流量類型,并準(zhǔn)確執(zhí)行軟件調(diào)試。理想情況下,集成工具以在單一環(huán)境中實現(xiàn)端到端軟件開發(fā)。

LSI 通過六代通信處理器開發(fā)了一個集成的軟件開發(fā)環(huán)境。這些工具已經(jīng)通過多年的實際部署得到強化。LSI 提供了一個高級開發(fā)工具包 (ADK),它由高度可擴展、客戶可擴展的模塊組成,這些模塊可以組合起來以實現(xiàn)快速、輕松的應(yīng)用程序開發(fā)。這些功能特定的模塊可以無縫地快速開發(fā)利用無線、有線和企業(yè)網(wǎng)絡(luò)的非對稱多核架構(gòu)的應(yīng)用程序。

下一代網(wǎng)絡(luò)和應(yīng)用程序不斷增長的性能需求,加上用戶對可靠性和服務(wù)質(zhì)量的期望,需要專門構(gòu)建的非對稱多核架構(gòu)以最低的功耗和成本實現(xiàn)線速、確定性的性能。用于網(wǎng)絡(luò)基礎(chǔ)設(shè)施應(yīng)用的 LSI 解決方案通過多核處理器和加速器的正確組合進行了優(yōu)化,以提供可擴展、可靠和確定性的性能。我們稱其為“正確完成多核”。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19166瀏覽量

229152 -

操作系統(tǒng)

+關(guān)注

關(guān)注

37文章

6740瀏覽量

123192 -

模擬器

+關(guān)注

關(guān)注

2文章

868瀏覽量

43165

發(fā)布評論請先 登錄

相關(guān)推薦

“雙系統(tǒng)”出爐!瑞芯微RK3562J非對稱AMP:Linux+RTOS/裸機

RK3566高性能低功耗四核應(yīng)用處理器數(shù)據(jù)手冊

旋智多核心處理器助力電機控制應(yīng)用

對稱多處理器的特點是什么

對稱多處理器系統(tǒng)中的進程分配包括

對稱多處理器和非對稱多處理器的區(qū)別

【本周六-上海】SMP對稱多處理 線下培訓(xùn)

線下培訓(xùn) | 瑞薩電子基于RZ/G2L的OpenAMP混合部署實戰(zhàn)培訓(xùn)

單相降壓轉(zhuǎn)換器雙非對稱BG評估板數(shù)據(jù)手冊

單相降壓轉(zhuǎn)換器雙非對稱AG評估板數(shù)據(jù)手冊

Andes晶心科技推出高性能AndesCore AX65處理器IP

“國產(chǎn)雙系統(tǒng)”出爐,RK3568J非對稱AMP:Linux+RTOS/裸機

高性能對稱雙核高性能Blackn處理器ADSP-BF606/ADSP-BF609應(yīng)用筆記

提供非對稱多核處理器提高性能可預(yù)測性

提供非對稱多核處理器提高性能可預(yù)測性

評論