問題:實現 N 位 Johnson Counter。

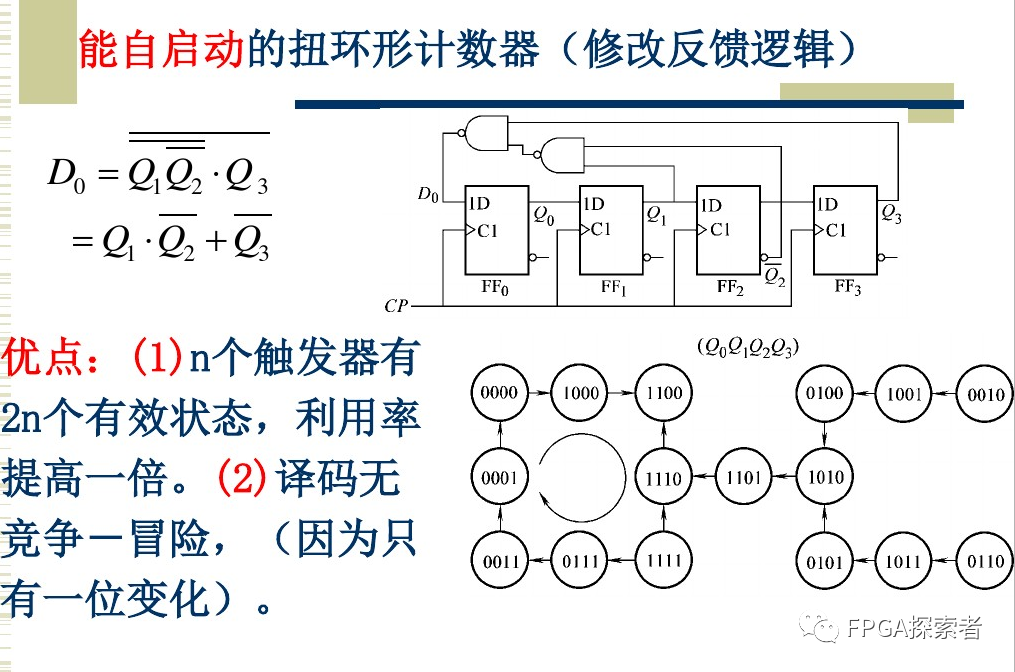

當 N = 4 時,輸出應該是

0000 -> 1000 -> 1100 -> 1110 ->

1111-> 0111 ->0011-> 0001 ->

0000 ->...

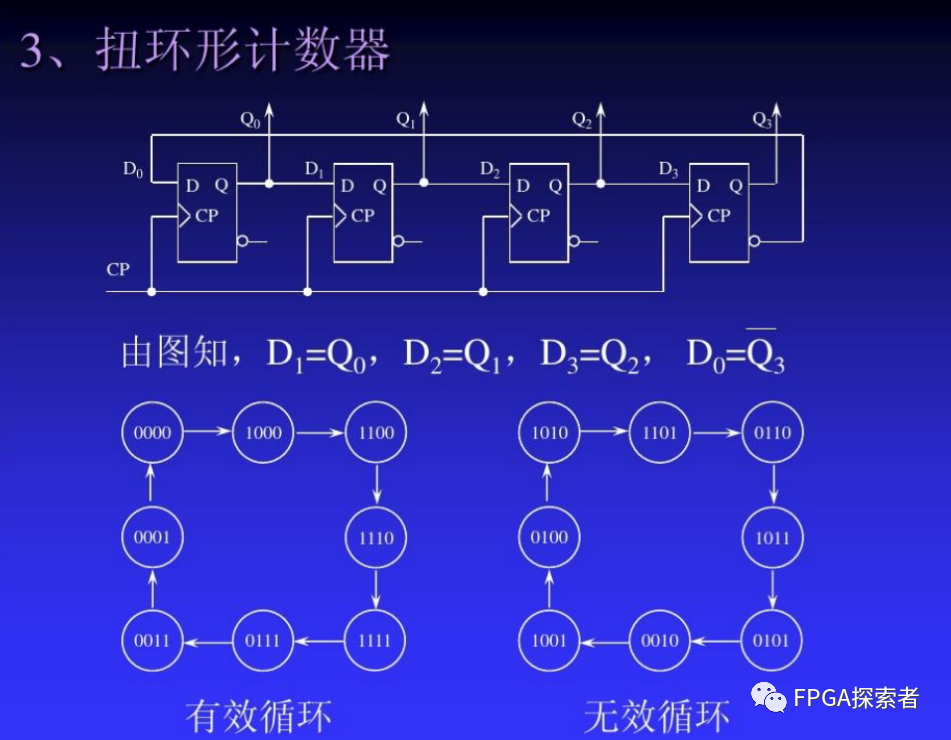

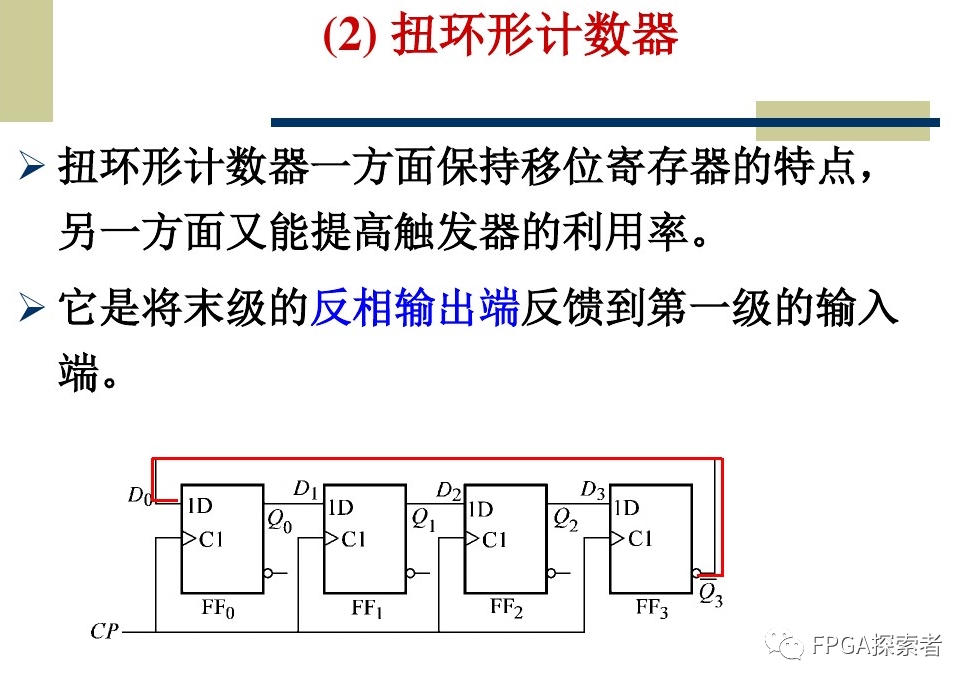

如下圖所示,扭環形(約翰遜)計數器最后一個觸發器的輸出取反~Q3,然后輸入回第一個觸發器的輸入 D(0)= ~Q(N-1),其余觸發器的輸入來自前級的輸出 D(i+1) = Q(i)。

D(0)= ~Q(N-1)

D(i+1) = Q(i)

Johnson 約翰遜計數器Verilog 實現

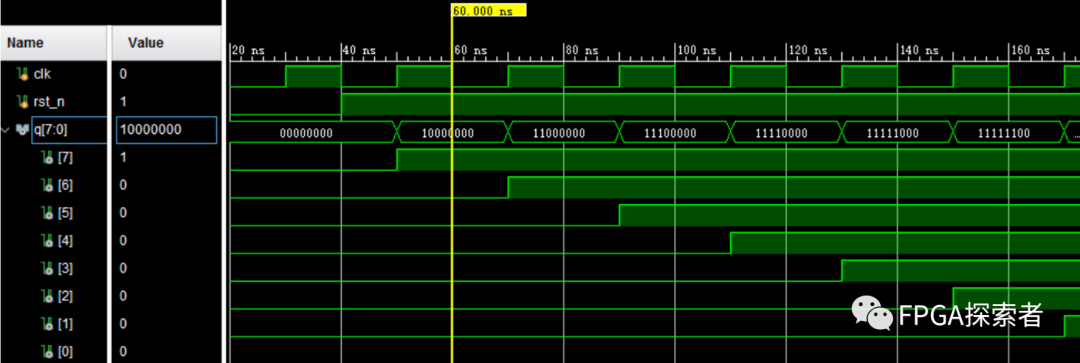

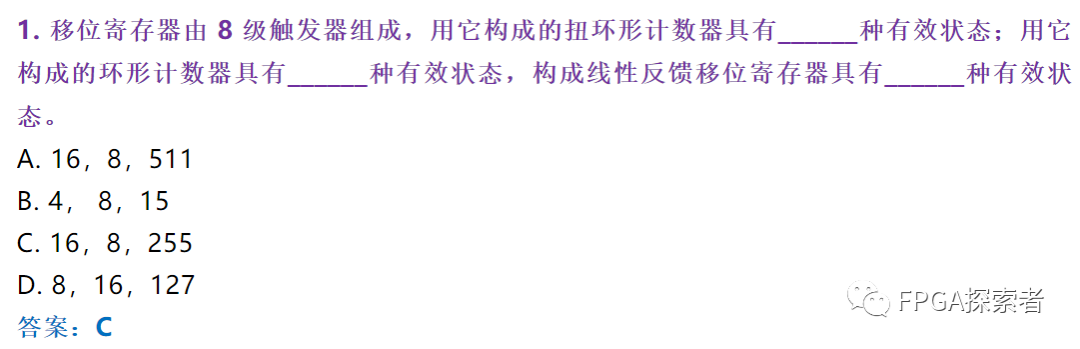

用Verilog HDL寫一個8-bit的Johnson計數器,N = 8。

module johnson#(parameter N=8)(input clk,input rst_n,output reg [N-1:0] q);always @ (posedge clk,negedge rst_n)beginif(!rst_n)q<=?{N{1'b0}};????elseif(!q[0])q <= {1'b1,q[N-1:1]};elseq <= {1'b0,q[N-1:1]};endendmodule

仿真圖:

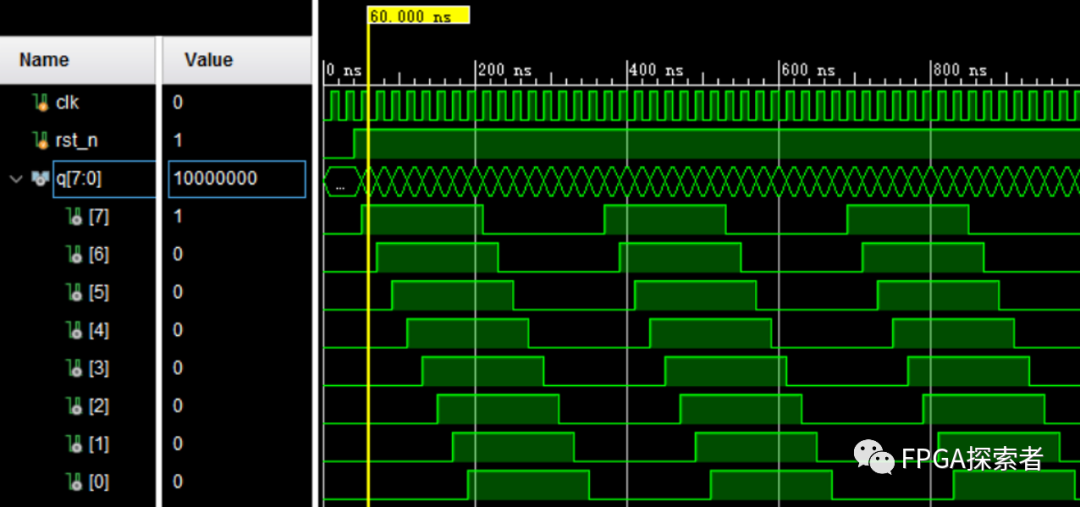

第二種:

module johnson#(parameter N=8)(input clk,input rst_n,output reg [N-1:0] q);always @ (posedge clk,negedge rst_n)beginif(!rst_n)q<=?{N{1'b0}};????elseq<=?{~q[0], q[N-1:1]};endendmodule

Johnson 約翰遜計數器

(1)扭環形計數器,約翰遜計數器,每次狀態變化時僅有一個觸發器發生翻轉,譯碼不存在競爭冒險,在n(n≥3)位計數器中,使用2n個狀態,有2^n-2n個狀態未使用;

(2)環形計數器,正常工作時所有觸發器中只有一個是1(或0)狀態,計n個數需要n個觸發器,狀態利用率低;

(3)n個寄存器的線性反饋移位寄存器LFSR可以產生的最長的隨機序列是2^n?1長度(即m序列)。LFSR常被用來生成m序列,也可產生和校驗CRC。

審核編輯 :李倩

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601873 -

Verilog

+關注

關注

28文章

1344瀏覽量

109986 -

觸發器

+關注

關注

14文章

1996瀏覽量

61052

原文標題:FPGA/數字IC筆試題——Verilog實現 N 位 Johnson Counter【約翰遜計數器】【扭環形計數器】

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

雷擊計數器的概述與應用分析

Johnson約翰遜計數器Verilog實現

Johnson約翰遜計數器Verilog實現

評論