引言

我們華林科納描述了一種與去離子水中銅的蝕刻相關的新的成品率損失機制。在預金屬化濕法清洗過程中,含有高濃度溶解氧的水會蝕刻通孔底部的銅。蝕刻在金屬化后殘留的Cu中產生空隙,導致受影響的陣列電路中的高電阻和功能故障。去離子水中的溶解氧濃度必須最小化,以防止銅的蝕刻。

介紹

與鋁互連相比,銅互連具有更高的電阻率和可靠性,因此在微電子行業獲得了廣泛認可。然而,存在許多與銅金屬化相關的產量問題,尤其是在濕法化學清洗期間的穩定性方面。在與化學機械拋光(CMP) 或通孔蝕刻相關的濕法清洗后(即在蝕刻停止移除之前)[5],經常會觀察到銅的腐蝕或蝕刻。

已經報道了三種不同類型的銅互連腐蝕;光腐蝕、電偶腐蝕和化學腐蝕。要發生腐蝕,至少需要兩個反應;陽極反應和陰極反應。在陽極,金屬表面被氧化,形成金屬離子和電子;

銅(s) d Cu2+ + 2e- (1)

在陰極,電子被幾種可能的電子消耗

此外,陽極和陰極之間必須有電連接,并且必須有電解質與陽極和陰極都接觸。

銅互連的腐蝕通常取決于圖案。當Cu電連接到襯底中的p型Si區時,在光的存在下觀察到光腐蝕。連接到p型硅(陽極)的銅比連接到n型區域(陰極)的銅處于更正的電位,使其更容易受到腐蝕。光允許電流流過硅并完成具有電解質的電化學電池,提供腐蝕發生所需的電荷載體,在等式和中)。

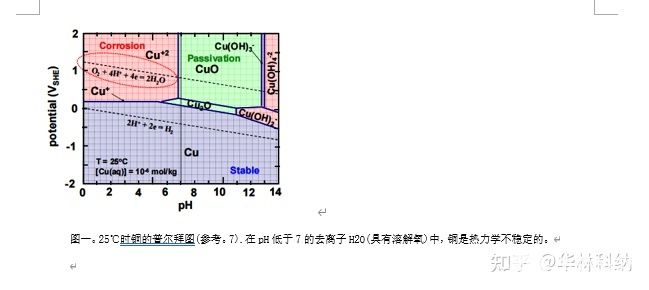

銅的蝕刻通常與去H2O沖洗有關。起初,這似乎是一個令人驚訝的結果,因為迪H2O

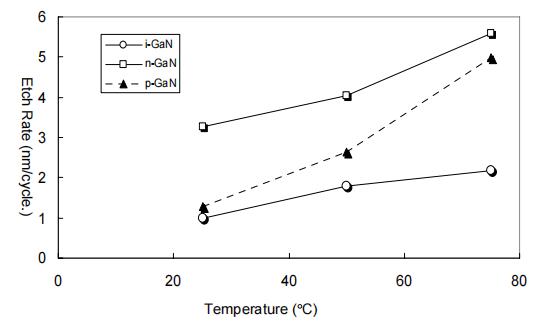

通常被認為是一種無害的清潔處理。然而,在電化學文獻中,眾所周知,在氧氣存在下,銅在H2O中是熱力學不穩定的(圖1)。如果去H2O中存在氧,它會消耗銅溶解產生的過量電子(分別為方程式2b和1),從而使銅腐蝕繼續進行。銅在去離子水H2O中的腐蝕速率取決于溶解氧濃度、溫度和pH值,溶解氧濃度為200至300 ppb時的最大腐蝕速率。在去離子H2O中使用溶解氧被認為是提高化學機械拋光后清洗效果的一種方法(即更有效地去除表面的銅污染物)。然而,去離子H2O中的高氧濃度會在CMP后清洗過程中造成腐蝕。通孔蝕刻后DI H2O沖洗液中銅的蝕刻也與“清洗液中的氧氣”的存在有關。

實驗

樣品采用0.13 ?m CMOS工藝制造,在FSG電介質中采用過孔優先雙鑲嵌Cu。金屬化前的預清洗包括稀HF和去離子水沖洗。

在完全集成的邏輯芯片上檢測到電氣故障。使用掃描鏈方法定位產品芯片中故障的電位置。掃描鏈嵌入在邏輯電路中,以測試電路的小子集。添加額外的測試引腳,為電路的關鍵部分提供輸入和輸出。當在掃描鏈中檢測到故障時,故障區域相對較小,因此可以通過分層技術容易地檢測到。

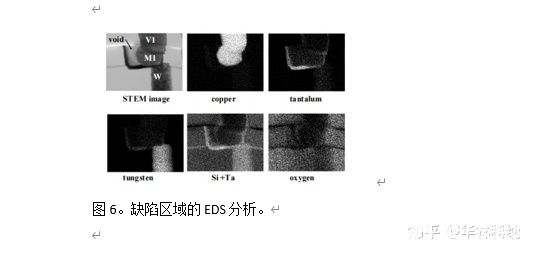

不合格的芯片被分層,然后通過掃描電子顯微鏡(SEM)、透射電子顯微鏡(TEM)和掃描透射電子顯微鏡(STEM)進行分析。使用能量色散譜(EDS)分析了STEM中失效結構的化學成分(JEOL,2010F)。TEM樣品制備包括剝離至V1,用SiO2覆蓋以保護表面,然后使用聚焦離子束(FIB)研磨從感興趣的區域提取薄樣品(150 nm)。

討論

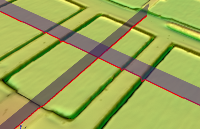

濕法清洗過程中銅的蝕刻是專用陣列電路所獨有的。沒有這種陣列的其他電路具有高產量(圖2)。因此,特殊陣列中的下層硅會導致腐蝕。這一點通過運行一些晶片得到了證實蝕刻不足。自動光學顯微鏡檢查顯示在M1中沒有空隙,表明如果M1是浮動的,就不會發生銅的蝕刻。

已知水中溶解的氧氣會增強銅的腐蝕(圖1)。因此,研究了M1銅中空隙的形成作為去離子水沖洗中O2濃度的函數。自動光學顯微鏡檢查顯示,可以通過最小化去離子水中的O2含量來消除空隙。這通過在具有高百分比的特殊陣列的掃描鏈上的電測量來證實(圖8)。這也是特殊陣列中M1銅的蝕刻顯然與水沖洗中的高O2濃度有關。

然而,確切機制仍不清楚。至少有兩種可能;電偶腐蝕和結強化腐蝕(圖9)。

由于水中氧氣濃度較高,預計銅相對于鉭襯里的電偶腐蝕會增強。所有表現出腐蝕的M1圖案都具有最小寬度的線,因此鉭和銅暴露在通孔底部的預清洗中。對于這種機理,銅是陽極,鉭是陰極。O2的作用是消耗Ta陰極的電子(圖9中的方程式(2b)和反應(a))。然而,還有許多其它部分接地的過孔,其中的M1金屬不會被腐蝕,因此Si中的底層結肯定也起了作用。

下面的硅結的作用類似于光腐蝕中的結的作用。連接到p型結的Cu處于比連接到n型區的Cu更低的電位(因此更高易受腐蝕),如果向結施加偏壓的話。向結施加偏壓的一種方法是用光。

然而,即使在沒有光的情況下也觀察到M1銅的蝕刻,這表明光蝕刻不是機理。更可能的機制是O2在連接到n型區域的Cu處消耗電子,從而偏置結。

結論

我們華林科納描述了一種新的成品率損失機理,它與去離子水中銅的腐蝕有關。在預金屬化濕法清洗過程中,含有高濃度溶解氧的水會蝕刻通孔底部的銅。蝕刻在金屬化后殘留的Cu中產生空隙,導致受影響的陣列電路中的高電阻和功能故障。去離子水中的溶解氧濃度必須最小化,以防止銅的蝕刻。

審核編輯:符乾江

-

半導體

+關注

關注

334文章

27010瀏覽量

216316 -

蝕刻

+關注

關注

9文章

413瀏覽量

15346

發布評論請先 登錄

相關推薦

濕法蝕刻的發展

銅互連,尚能飯否?

基于光譜共焦技術的PCB蝕刻檢測

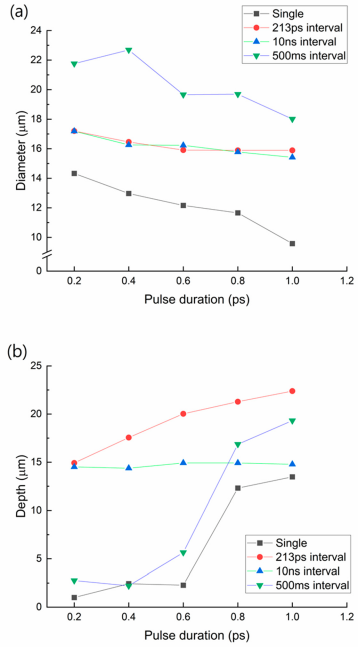

利用貝塞爾光束、超短雙脈沖激光和選擇性化學蝕刻研究玻璃通孔(TGV)

電偶腐蝕對先進封裝銅蝕刻工藝的影響

東京電子新型蝕刻機研發挑戰泛林集團市場領導地位

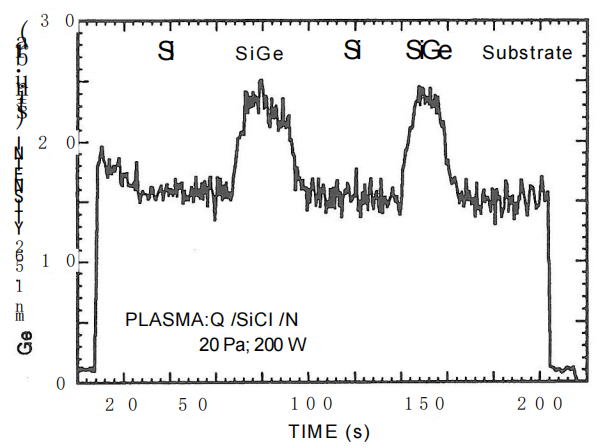

Si/SiGe多層堆疊的干法蝕刻

PCB為什么發生甩銅?這3個原因給說全了

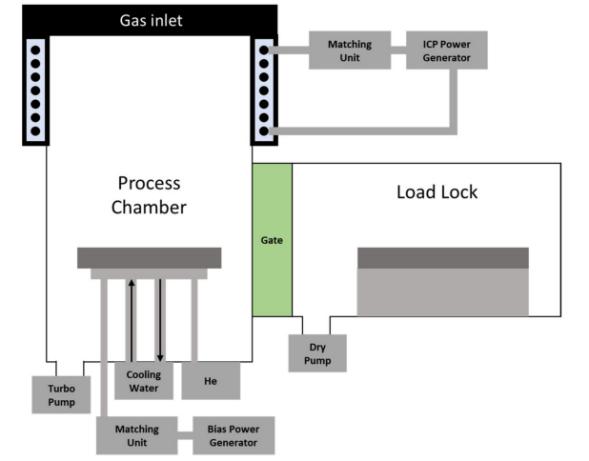

電感耦合等離子刻蝕

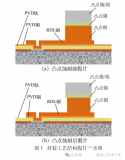

PCB的蝕刻工藝及過程控制

鈉離子電池研究現狀

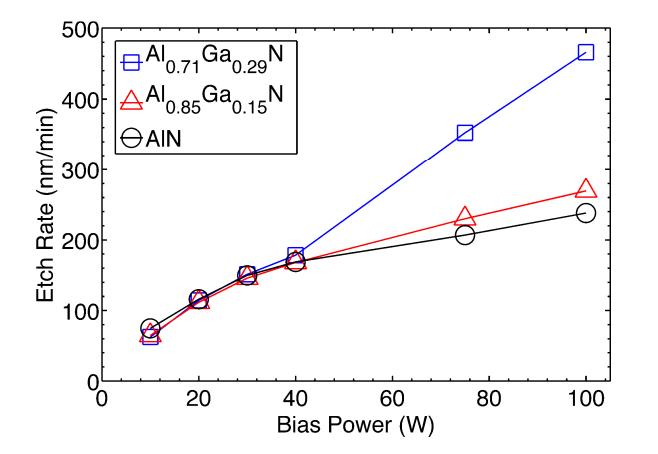

不同氮化鎵蝕刻技術的比較

銅在去離子水中的蝕刻研究

銅在去離子水中的蝕刻研究

評論