1 引言

碳化硅(SiC)材料作為第三代半導體材料的代表之一,其禁帶寬度達到 3.26 eV,是硅(Si)材料的 3 倍,臨界擊穿電場強度是 Si 材料的 10 倍,熱導率接近 Si材料的 3 倍,被認為是下一代超高壓功率器件的理想材 料。SiC 金 屬 氧 化 物 半 導 體 場 效 應 晶體管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)是目前最成熟、應用最廣的 SiC 功率開關器件,然而隨著功率器件的阻斷電壓不斷增大,其導通電阻也會迅速增大,使其很難在超高壓領域發揮重要作用。絕緣柵雙極晶體管(Insulated Gate BipolarTransistor,IGBT) 作為現如今功率半導體器件的主要代表之一,綜合了功率 MOSFET 和雙極型晶體管(Bipolar Junction Transistor,BJT)兩種器件的結構,正常導通狀態下,會在其漂移層中發生電導調制效應,從而很好地降低了其漂移層的導通電阻以及整個器件的導通壓降,極大地克服了高壓 MOSFET 器件的缺點。

早在 2007 年,美國 Cree 公司就報道了阻斷電壓為 9 kV 的平面柵 P 溝道 4H-SiC IGBT 器件,該器件的微分比導通電阻值為 88 mΩ·cm2,當時之所以采用 P 溝道,是因為 P 型 SiC 襯底電阻過大,無法支撐其制備 N 溝道 IGBT 器件。2009 年美國普渡大學利用數 值 模 擬 軟 件 評 估 了 10 kV SiC MOSFET 和 SiCIGBT 器件的性能,指出 SiC IGBT 器件更適合應用于高壓低頻領域。Cree 公司在 2009 年采用厚度為100 μm、摻雜濃度為 3×1014 cm-3 的 N 型外延成功制備了耐壓超過 13 kV 的 N 溝道 IGBT 器件,其微分比導通電阻值僅為 22 mΩ·cm2,遠遠低于 P 溝道 IGBT 器件。2015 年 Cree 公司和美國陸軍實驗室(Army Research Laboratory)共同合作,通過對比阻斷電壓為15 kV 的 4H-SiC MOSFET 和 N 溝道 4H-SiC IGBT 器件,發現 15 kV 4H-SiC MOSFET 器件的比導通電阻高達 204 mΩ·cm2,而同等級下的 N 溝道 4H-SiC IGBT器件僅為 50 mΩ·cm2,同時報道還指出通過在 N 溝道4H-SiC IGBT 器件結構中加入載流子存儲層(Carrier Storage Layer,CSL),可以減小器件 JFET 區域的導通電阻,從而降低正向壓降。

2014 年 Cree 公司還聯合了北卡羅來納州立大學等高校,在 160 μm 的外延層上成功研制了 20 kV SiC N 溝道 IGBT 器件,在導通電流為 20 A 的條件下,其導通壓降為 6.4 V。

2016 年日立(Hitachi)的研發團隊報道了具有極低開關損耗的 N 溝道 4H-SiC IGBT 器件,其漂移層厚度為 60 μm,阻斷電壓能夠達到 6.5 kV,其開關損耗只有 1.2 mJ。在近幾年研究發展過程中,Cree 公司甚至報道了阻斷電壓為 27 kV 的 N 溝道 SiC IGBT 器件,加入三代半交流群,加VX:tuoke08,器件的微分比導通電阻值僅為 123 mΩ·cm2。

由于受 4H-SiC 單晶質量、外延生長技術的制約,國內對于 SiC IGBT 器件方面的實驗研究起步相對較晚。南京電子器件研究所 SiC 團隊于 2018 年成功研制出了 13 kV SiC N 溝道 IGBT 器件,但其導通特性較差。近年來通過對器件結構優化以及關鍵工藝技術的提升,SiC N 溝道 IGBT 器件取得了重大突破,縮短了與國外的差距。本文介紹了團隊 SiC N 溝道 IGBT器件研制的最新成果。

2 器件設計與制造

2.1 器件基本結構

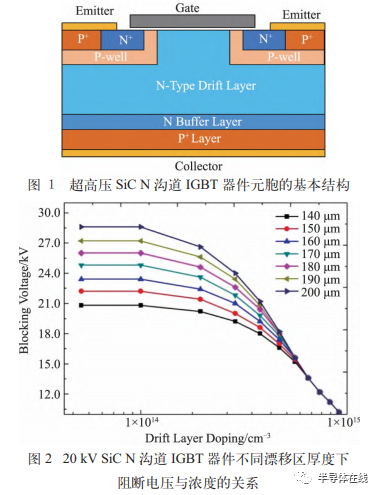

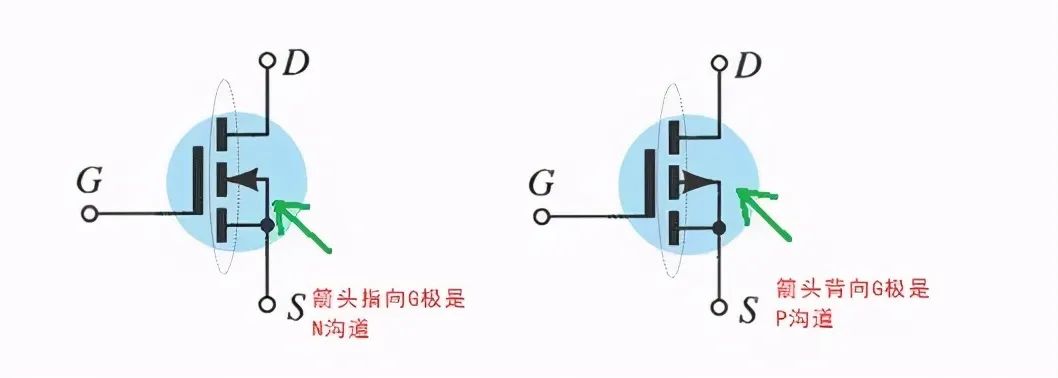

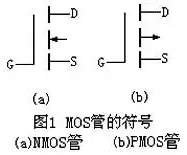

超高壓 SiC N 溝道 IGBT 器件元胞的基本結構如圖 1 所示。N+ 區域定義為源區,相應的電極稱為發射極(Emitter)。背面 P+ 區域定義為漏區,相應的電極稱為集電極(Collector)。超高壓 SiC N 溝道 IGBT 器件與MOSFET 器件一樣都是柵控型器件,柵區是器件的控制區域,相應的電極稱為柵極(Gate)。器件溝道的形成在緊靠柵區邊界處,其長度則由 P-well 區和 N+ 源區的橫向擴散進行定義。場截止層(F-S)為高摻雜濃度的N+ 緩沖層,其主要作用在于使正向阻斷狀態下電場在該層降為 0,從而避免電場對 P+ 襯底的影響。IGBT 器件正面結構與功率 MOSFET 器件正面結構一致,唯一的不同之處在于器件的背面結構。IGBT 器件的背面結構是通過 P+ 外延層實現的,使得 IGBT 器件的背面結構比功率 MOSFET 器件多一個 PN 結,在導通狀態下背面注入的少數載流子和正面的溝道載流子在 N漂移區復合,產生電導調制效應,大大降低了N漂移區的導通電阻。

2.2器件仿真設計

2.2.1 材料結構仿真設計

由于 SiC IGBT 器件的理論擊穿電壓主要由漂移區的厚度和摻雜濃度決定。為了使器件阻斷電壓超過20 kV,研究團隊通過有限元仿真對漂移區的厚度和摻雜濃度進行優化設計,仿真結果如圖 2 所示。觀察得出當器件摻雜濃度較高時其阻斷電壓與外延層厚度無關,而當摻雜濃度較低時阻斷電壓基本正比于外延厚度。這主要是因為外延層摻雜濃度較高時,空間電荷區主要集中在外延層內部,此時外延層內電場為三角形分布且并未達到外延層底部,即使外延厚度發生變化電場的積分也無變化;而當摻雜濃度較低時,此時電場可近似為矩形,積分近似正比于外延厚度。但不能為了提高阻斷電壓一味提高外延厚度,因為過厚的外延層會導致正向導通電阻的增加,所以在保證阻斷電壓的同時要盡量使用較小的外延厚度。考慮到器件終端保護的效率問題和實際的器件應用需求,研究團隊在設計材料參數時,將材料擊穿電壓需求設定為25 kV,預留 20%的設計冗余,在此條件下最終選取厚度為 180μm,摻雜濃度為 2×1014 cm-3的 N 型外延材料。

2.2.2 JFET 區仿真設計

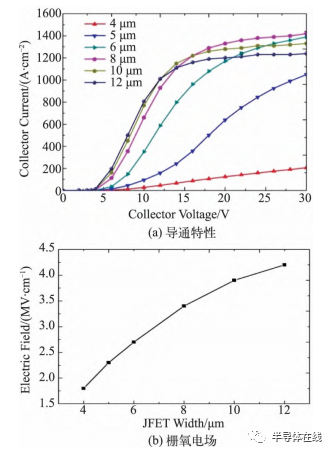

理論上,N 溝道 IGBT 器件的導通電阻主要由溝道電阻、漂移區電阻、JFET 區電阻以及一系列接觸電阻組成。對于擊穿電壓超過 20 kV 的 SiC IGBT 器件而言,對其導通電阻影響最大的是垂直 JFET 區電阻,而垂直 JFET 區設計優化主要是對 JFET 區的寬度和摻雜濃度進行優化。加大 JFET 區的橫向長度和摻雜濃度可以顯著減小器件導通電阻,但在阻斷狀態時,延伸的耗盡區不容易夾斷,對柵氧化層底部電場強度的抑制作用減弱,可能會引起器件提前擊穿。縮小 JFET區的橫向長度和摻雜濃度會增強對柵氧化層底部電場的抑制作用,器件在高電壓下的穩態性變好,但同時會引起器件導通電阻的增加,導致穩態電流的下降,因此需要統籌考慮 JFET 區對于器件導通特性和擊穿電壓之間的關系,不同 JFET 寬度下器件的導通特性以及截取的柵極氧化層電場如圖 3 所示。觀察發現隨著 JFET 區寬度從 4 μm 擴展至 12 μm 時,增大垂直 JFET 區的寬度可以降低溝道導通電阻,使導通電流增大。但隨著 JFET 區進一步增大,元胞尺寸的增大效應也將變得明顯,使得器件導通電流密度隨 JFET寬度增加而增長的速率減緩,同時反向偏置狀態下P-well 區的夾斷作用降低,柵氧化層底部電場提高。理論上,氧化層擊穿是指氧化層電場在反向阻斷時超過自身臨界場強的情況,一般認為 SiO2 的電場不應超過3 MV/cm。因此在保證器件可靠性的同時,為實現盡可能高的器件導通能力,元胞結構最終采用 6 μm 的JFET 區域。

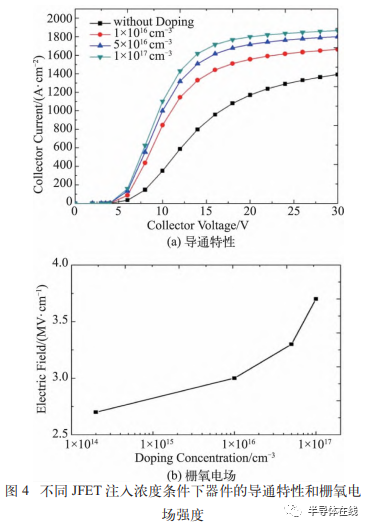

由于 SiC IGBT 器件超高的耐壓要求,器件漂移區一般保持非常低的摻雜濃度,這往往會導致垂直JFET 區電阻大大增加,因此在 20 kV SiC IGBT 器件研制中,通過引入 JFET 區注入摻雜技術,可更有效地提升器件導通特性,仿真結果如圖 4(a)所示。觀察發現隨著 JFET 區摻雜濃度的增大,器件導通電流隨之增大,主要是因為 JFET 區摻雜濃度增大,器件導通時P-well 區兩側的耗盡區寬度大幅度減小,JFET 區電阻減小,器件導通電阻也隨之減小。與此同時該器件反向偏置狀態下 P-well 區的夾斷作用降低,柵氧化層底部電場提高,不同 JFET 濃度下柵氧化層電場如圖 4(b)所示。綜合考慮器件的導通壓降和阻斷電壓,元胞結構采用濃度為 1×1016 cm-3 的 JFET 區注入條件。

2.2.3 載流子壽命仿真設計

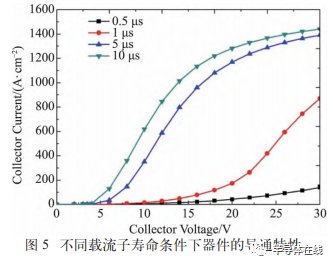

高載流子壽命是實現大功率 SiC 雙極型器件的關鍵技術之一。不同載流子壽命下器件的導通特性如圖5 所示。觀察發現隨著載流子壽命的增加,器件的導通電流增加,主要是因為少數載流子壽命的增強可以顯著改善雙極型器件的電導調制效應,有利于實現較低的器件導通壓降。仿真結果顯示,為了達到較好的導通特性,器件的載流子壽命最好能夠達到5 μs 以上。

2.3 器件制備

2.3.1 器件制備方案及流程

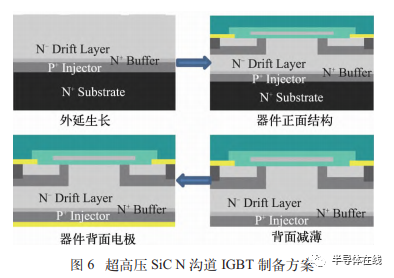

研究團隊設計的 SiC IGBT 器件為 N 溝道 SiC IGBT 器件,N 型 SiC 襯底電阻率約為 0.025 Ω·cm,而P 型 SiC 襯底電阻率約為2.5 Ω·cm,因此如果在350 μm P 型 SiC 襯底上制造 N 溝道 SiC IGBT 器件,此時 P 型襯底電阻值甚至大于所設計器件的導通電阻值,再加上目前國內很難供應 P 型 SiC 襯底,因此團隊提出一種在 N 型 SiC 襯底上進行器件設計與制造的方案。具體的制備方案如圖 6 所示。通過在 N 型4H-SiC 襯底上生長所需的關鍵外延層,包括 N漂移層,N+緩沖層以及 P+ 集電極層;采用 SiO2 作為各區域的注入掩模,由多次 P 型離子注入實現 P-well 區和 P+區域,多次高劑量 N 型離子注入實現 N+ 區域。同時為了有效降低該器件 JFET 區的電阻,單獨對 JFET 區域進行 N 型離子注入,所有注入完成后在 1650 ℃的氬氣(Ar)環境下退火以激活注入離子。退火后,通過犧牲氧化去除表面碳層,濕法表面清洗后放入高溫氧化爐中進行干氧氧化,形成柵氧化層。采用一氧化氮(NO)高溫退火技術,有效降低柵氧界面陷阱密度,最終氧化層厚度控制在 50 nm 左右。在柵氧工藝完成后,通過在柵氧化層上沉積多晶硅實現柵電極的制作。采用氧化硅 / 氮化硅(SiO2/SiN)介質實現柵極和發射極隔離以及表面鈍化。發射極的歐姆接觸由金屬鎳(Ni)實現,介質孔刻蝕后通過加厚鋁(Al)層完成發射極單胞之間的互聯。器件正面結構完成后通過減薄 / 背面研磨的方法去除 N 型襯底,保留部分 P+ 層,接著蒸發背面歐姆金屬,考慮到普通的背面歐姆制作工藝需要相當高的溫度,過程中的高溫會損傷表面器件結構,因此采用激光退火工藝完成背面的歐姆制作。

2.3.2 載流子壽命提升工藝

由于 IGBT 器件電導調制效應的存在,使得載流子壽命高低成為影響漂移區電阻高低的重要因素之一。在 N 型 SiC 材料的早期研究階段,Z1/2 缺陷中心被公認為是載流子壽命的“殺手”。到目前為止,國際上主要采用兩種相對成熟的技術來消除 Z1/2 缺陷中心:

1)從外部引入過量的碳原子,并且通過高溫退火來促進碳原子體區擴散;2)在適當條件下,通過長時間高溫熱氧化消除 Z1/2 缺陷中心。考慮到碳注入結合高溫退火的方法在高能碳離子注入過程中容易引入新的缺陷,同時受碳注入深度的限制,對厚層 SiC 外延來說效果不夠理想,因此本研究采用長時間高溫熱氧化工藝來提升載流子壽命。

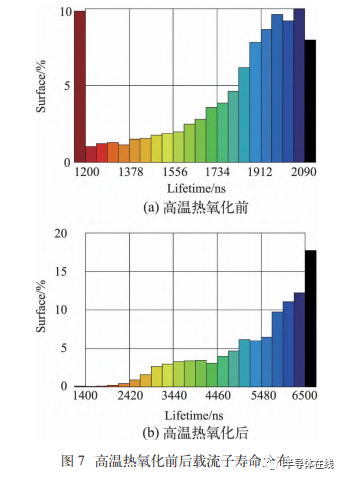

研究團隊首先采用 μ-PCD 測量方法測量 SiCIGBT 厚外延片材料的少子壽命,高溫熱氧化前分布如圖 7(a)所示,其少子壽命平均值大約在 1.76 μs,后續將該外延片經過 10 h 的高溫熱氧化,去除表面氧化層清洗處理后,再次測量其少子壽命,結果如圖 7(b)所示,其平均值提升至 5.42 μs。從實驗結果看,長時間的高溫氧化工藝對于器件的少子壽命有較大的提升作用,主要原因在于高溫熱氧化的過程中,部分碳原子會擴散到體區并填補碳空位,消除 Z1/2 缺陷中心。

3 結果和討論

制備的 20 kV SiC IGBT 器件芯片單胞長度為14 μm,溝道長度為 1.0 μm,器件采用了總寬度為1.4 mm 的場限環終端,總尺寸達到 9.2 mm×9.2 mm,其中有源區面積為 30 mm2。

3.1 阻斷特性

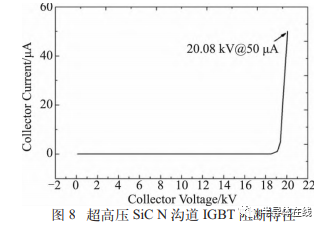

對超高壓 SiC N 溝道 IGBT 器件的正向阻斷特性進行測試,必須將器件的柵極與發射極接地,在集電極加正電壓。而且考慮到設計的器件阻斷電壓大于18 kV,因此在測試過程中,需要將芯片浸泡在高壓測試油中,從而隔絕空氣。室溫下正向阻斷特性測試結果如圖 8 所示,該器件在室溫下擊穿電壓可以達到20 kV。當集電極電壓為 20.08 kV 時,漏電流為 50 μA,為目前國內研制的最高擊穿電壓 SiC IGBT 器件。

3.2 導通特性

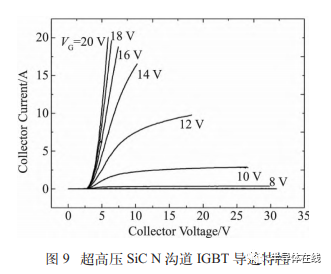

SiC N 溝道 IGBT 器件的正向導通特性測試一般在發射極接地、柵極加正偏壓的情況下進行。不同柵壓下的集電極電流隨著集電極電壓的變化曲線如圖 9所示。室溫下,該器件在柵壓為 20 V,集電極電流為20 A 時,集電極導通電壓為 6.0 V,此時其微分比導通電阻為 27 mΩ·cm2,該值與國際上相同擊穿電壓器件的微分比導通電阻最低值相當。

為了更好地反映載流子壽命對于器件導通特性的影響,本文分析了芯片 A(引入載流子壽命提升工藝)、芯片 B(未引入載流子壽命提升工藝)的實驗結果以及仿真結果,具體高溫熱氧化處理前后超高壓 SiC N 溝道 IGBT 導通特性如圖 10 所示。觀察發現芯片 B在柵極電壓為 20 V、集電極電流密度為 70 A/cm2 的條件下,器件導通壓降為 16.2 V 左右,引入載流子壽命提升工藝后,芯片 B 在同等測試條件下,其導通壓降降至 6.5 V 左右,這一結果也恰好驗證了載流子壽命的提升能有效提高 SiC N 溝道 IGBT 器件的導通能力。

審核編輯 :李倩

-

IGBT

+關注

關注

1265文章

3762瀏覽量

248367 -

碳化硅

+關注

關注

25文章

2702瀏覽量

48893

原文標題:超高壓碳化硅 N 溝道 IGBT 器件的設計與制造

文章出處:【微信號:cetc45_wet,微信公眾號:半導體工藝與設備】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IGBT和SiC封裝用的環氧材料

N溝道結型場效應管的工作原理

P溝道與N溝道MOSFET的基本概念

igbt芯片vce與結溫的關系

igbt必須加吸收電容嗎為什么

如何更好地驅動SiC MOSFET器件?

IGBT是什么類型的器件 IGBT是電壓驅動還是電流驅動

IGBT是什么驅動型器件

1200 V,80 mΩ,N溝道SiC MOSFET初步數據表

NSF040120L4A0:1200 V,40 mΩ,N溝道SiC MOSFET初步數據表

NSF080120L3A0:1200 V,80 mΩ,N溝道SiC MOSFET一般說明

SiC N溝道IGBT器件研制的最新成果

SiC N溝道IGBT器件研制的最新成果

評論