在當今競爭激烈的環境中,將富含嵌入式軟件的復雜電子設備更快地推向市場,同時使它們更便宜、更可靠是一個非常冒險的提議。

不徹底測試硬件設計不可避免地會導致重新設計,增加設計成本并延長網表到布局過程的交付時間,并最終延遲上市時間,從而對收入流產生破壞性影響。缺少市場窗口的更顯著結果隱藏在嵌入式軟件的后期測試中。

毫不奇怪,項目周期的驗證部分占用了不成比例的大量進度。這是因為跟蹤和消除錯誤并非易事,尤其是當片上系統 (SoC) 的軟件內容以每年大約2 0 0 %的速度增長時。相比之下,設計中硬件部分的增長僅為5 0 %左右。

雖然虛擬原型和現場可編程門陣列 (FPGA) 原型在早期嵌入式軟件測試中受到關注,但它們無法幫助實現軟硬件的集成。前者缺乏跟蹤硬件錯誤所需的硬件準確性。后者提供了快速放大錯誤所需的有限硬件調試功能。

因此,開發團隊和項目經理已將硬件仿真作為其驗證策略的基礎。仿真是一種多功能驗證工具,具有許多相關優勢,包括硬件/軟件協同驗證,或測試硬件和軟件集成的能力。軟件開發人員已經注意到了,因為它是唯一能夠確保嵌入式系統軟件與底層硬件正常工作的驗證工具。同樣值得注意的是,對于致力于調試復雜 SoC 設計的硬件工程師來說,它可以將軟件錯誤跟蹤到硬件或軟件行為中的硬件錯誤。其他好處包括它的快速編譯能力,軟件驗證的另一個優點,全面的設計調試和可擴展性,以適應包含超過 10 億個專用集成電路 (ASIC) 門的設計。此外,它可以高速處理數十億個驗證周期,以驗證嵌入式軟件和執行系統驗證。

過去,硬件調試和測試是項目周期驗證部分的唯一原因,這是由硬件描述語言 (HDL) 測試臺驅動的邏輯仿真管理的。傳統的 big-box 仿真僅用于最大的設計。許多開發團隊已采用形式驗證來補充模擬,增加基本覆蓋范圍并確保不會遺漏一些極端情況。然而,只有硬件仿真才能在實際時間內完成 SoC 設計的整個驗證任務,并緩解與基于事件的仿真相關的運行時問題。

一切都與軟件內容有關

SoC 的軟件內容使聯合驗證成為驗證策略中最重要的部分,因為它確認嵌入式 SoC 的硬件和軟件部分同時驗證并在提交到芯片之前正確交互。

過去,如果設計流片到芯片上后出現硬件問題,軟件開發人員必須盡可能地解決如何圍繞它編寫代碼。通過在 SoC 完成之前驗證軟件,設計團隊有機會在硬件問題被安裝到芯片之前修復它們。如前所述,仿真檢查以確保嵌入式軟件根據規范在支持硬件上運行。

過去,軟件調試是使用各種調試引擎完成的。每個內核一個,他們利用了硬件功能,這些功能提供了對處理器內部工作的可見性和控制。雖然提供了一些調試功能,但診斷問題的能力受到處理器提供的訪問類型的限制。此外,由于傳統的軟件調試通常發生在實際系統上,因此軟件開發人員正在以目標系統速度在真實硬件上執行真實代碼。這使他們能夠通過大量代碼快速找到錯誤例程。

這些傳統技術在調試 SoC 時會失效。因為沒有真正的硬件,代碼不能以真正的系統速度執行。假設,可以在執行代碼時模擬硬件,并且所有硬件可見性都將由模擬器提供。問題在于速度——這是一種調試代碼的緩慢方式。

例如,如果 SoC 設計為在 Linux 上運行程序,則軟件開發人員必須以數十億個時鐘周期完成 Linux 啟動,然后軟件才能開始執行。粗略的估計是,使用大約1 0赫茲(Hz) 的典型模擬速度完成Linux引導需要超過2 8 年的時間。

不管是硬件調試還是軟件調試,傳統的硬件和軟件調試工具是互不相識的。對于大型且復雜的 SoC 設計,單獨進行兩種類型的調試以嘗試定位問題是低效的。

讓兩者一起工作是理想的場景,而這正是仿真節省時間的地方。SoC 硬件在硬件中實現,通常是 FPGA 或其他一些可編程元件,使其速度更快。使用此設置,Linux 啟動可以在1 5分鐘內完成,具體取決于運行的實際速度。硬件仿真提供與具有斷點和波形的硬件調試器類似的控制和可見性。

確認 SoC 設計將按預期工作

硬件仿真以其高性能與其他驗證工具區分開來——這是由軟件需求驅動的日益重要的需求。它能夠確認 SoC 設計將按計劃工作,并且適合處理復雜的設計,這些設計可大至 10 億個 ASIC 等效門,并且每月消耗超過 1 萬億個驗證周期。即便如此,在此階段使用硬件仿真進行徹底和詳盡的功能驗證仍然是可用的最具成本效益和最有效的調試方法。

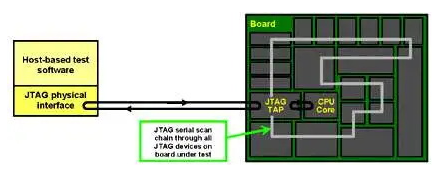

交易級建模 (TLM) 的引入和交易者的可用性可以將硬件仿真轉變為一系列垂直市場的虛擬平臺測試環境。交易者是驗證知識產權 (IP) 組合的一部分,是外圍功能或協議的高級抽象模型。交易者,通常作為現成的 IP 提供,可用于各種不同的協議。典型目錄包括 PCIe、USB、FireWire、以太網、數字視頻、RGB、HDMI、I2C、UART 和 JTAG 組件。

更好地驗證更復雜的系統

以前,硬件設計獨立于要在這些芯片上執行的軟件的創建。情況不再如此。由于 SoC 的處理器數量翻了一番,并且每一代產品包含的軟件內容增加了一倍,因此對軟件的關注成為開發團隊和項目經理的首要任務。現在,在開發團隊證明預期的軟件可以在硬件平臺上運行之前,SoC 是不完整的。

SoC 是一個成熟的嵌入式系統,需要硬件仿真來驗證它是否正常工作。借助硬件仿真,開發團隊可以更有策略地規劃并實施基于多個抽象級別的調試方法。他們可以同時跟蹤硬件和嵌入式軟件之間的錯誤,以確定問題所在。在此過程中,他們以經濟高效的方式節省了時間,大大降低了錯過市場窗口的風險。

審核編輯:郭婷

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601873 -

以太網

+關注

關注

40文章

5377瀏覽量

171126 -

soc

+關注

關注

38文章

4122瀏覽量

217946

發布評論請先 登錄

相關推薦

【「嵌入式Hypervisor:架構、原理與應用」閱讀體驗】+ Hypervisor應用場景調研

嵌入式開發常用軟件有哪些?

嵌入式系統軟硬件基礎知識大全

JTAG在整個嵌入式系統開發生命周期中的系統調試和測試中的作用

用于調試嵌入式系統軟件的硬件仿真

用于調試嵌入式系統軟件的硬件仿真

評論