PCIe 的分層協議帶來了不同的挑戰,因此也帶來了不同的解決方案。

PCI Express (PCIe) 驗證團隊的主要關注點是與前幾代 PCIe 的互操作性和向后兼容性。這需要工具來驗證設計的參數和協議方面,以確保合規性并驗證設計性能。PCIe的分層特性推動了不同的測試挑戰和解決方案,具體取決于關注的領域。

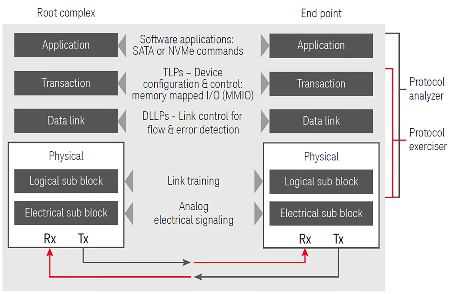

PCIe技術是一種分層協議,如圖1所示:

圖 1:不同層的 PCIe 協議需要不同類型的測試。

協議級驗證挑戰

一旦用戶在物理層級別達到數據有效狀態,這需要驗證鏈路信令和LTSSM 操作,他們就會使用 協議分析儀和練習器在協議級別測試更高層。分析儀連接到處于活動狀態的兩個設備之間的鏈路,以觀察和評估每個級別的數據。鍛煉器作為終端設備連接,以模擬壓力條件并記錄DUT 如何響應。PCIe 數據鏈路層的驗證通過規范測試來執行,這些測試檢查正在傳輸的數據鏈路層協議數據包 (DLLP)、確認、否定確認、重傳、和流量控制。驗證團隊需要能夠從所有錯誤(包括間歇性故障)中恢復的強大系統。

協議驗證的主要挑戰

是快速準確地測試系統功能,以便產品能夠上市。必須以有效的方式檢測、分析和糾正協議錯誤。

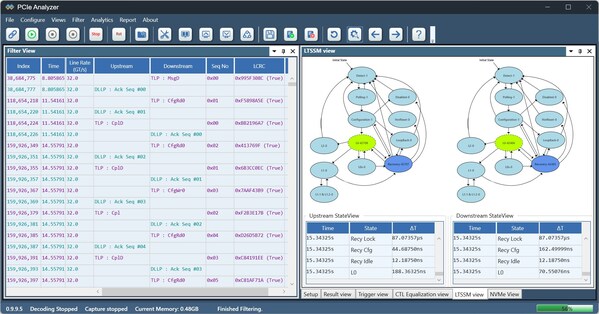

調試 PCIe 協議意味著捕獲高速流量,包括電源管理轉換。協議調試工具需要快速鎖定流量,然后觸發獨特的協議序列。調試較低級別的問題,例如電源管理,需要非常快的鎖定時間。捕獲流量后,查看不同抽象級別的數據可以隔離問題。

PCIe 協議調試中出現的另一個關鍵挑戰是以非侵入 方式訪問信號。連接到 PCIe 總線的探頭不得以影響總線值或操作的方式干擾或更改信號。探測信號的位置和方式取決于每個獨特的系統設計。中間總線探測器提供對流量的訪問,但不得影響信號質量。插槽中介層需要在長跡線上被動地傳遞信號,而不是改變信號。驗證團隊需要具有多種探測選項的靈活訪問權限。

隨著 PCIe 4.0 的到來,將速度提高到 16 GTps 將延續 PCIe 3.0 中 8 GTps 的一些相同趨勢,需要更高的信號質量調諧和均衡能力才能實現驗證。NVMe 協議提出了許多新的測試挑戰。NVMe 為 PCIe 連接的設備創建了一個新的高性能可擴展主機控制器接口,該接口映射來自主機的內存,以便將數據移入和移出存儲設備,具有低延遲和端到端數據保護。該接口利用多個隊列來管理和提供優化的命令提交和完成路徑,并支持并行操作。

協議驗證測試設置

使用分析儀進行驗證的最終目標是測試鏈路和數據傳輸,以確保設備功能和互操作性。為了實現這一點,協議分析器需要提供對每個獨特協議層發生的情況的可見性。在進行故障排除時,用戶必須將特定錯誤跟蹤到適當的層以進行更正。為了驗證設備,協議練習者需要能夠在同一張卡中模擬根復合體或端點。 鍛煉者通過發送適當的 I/O 流量來刺激被測設備,充當理想的鏈接伙伴。 然后,可以通過模擬各種條件和場景來驗證DUT 的錯誤恢復過程,而不會影響 其性能參數。

在這些功能和測試中,用戶必須通過一致的表示來解決信號訪問發生方式和位置的復雜性,以實現準確的數據恢復。探測解決方案需要具有高性能和多功能性,以適應不同類型的系統設計。探測需要保持非侵入性,以便訪問不會影響信號質量或協議操作。

以下每個功能都需要使用練習器和分析器進行測試,以確保數據鏈路和事務層功能正常且合規:

均衡 (EQ) 是訓練兩個終端以可靠地傳輸每個比特的過程。每個單獨的車道都必須經過培訓。在 by-4鏈接中,每個鏈接可以有不同的調整參數。訓練是動態的,需要正確設置每個泳道的前光標、光標和后光標值。信號質量對于成功運行至關重要。EQ 過程對于 PCIe 3.0 8 GTps 速度的成功鏈接至關重要, 對于 16 GTps 的 PCIe 4.0更為重要。

鏈路訓練信令狀態機 (LTSSM) 分析觀察和控制鏈路的不同可能狀態。狀態轉換處理鏈接、恢復和電源管理。LTSSM 的目標是達到稱為 L0 的狀態——鏈路處于活動狀態并且可以傳輸數據。LTSSM 中的其他狀態,例如配置、訓練和錯誤恢復例程,提供鏈路控制和恢復以及電源管理功能。

數據包捕獲查看單個 PCIe 數據包以解碼響應和設備配置和枚舉。從內存讀取和寫入的過程是基于數據包中包含的地址來通過鏈路傳輸數據的。

性能分析和流量控制會影響響應時間和整體吞吐量。流量控制用于防止緩沖區溢出,并且可以清楚地識別可能對數據吞吐量產生負面影響的信用不足問題。

在滿足所有測試以建立穩定的通信通道后,下一步是驗證PCIe 總線上的應用層(例如 NVMe)。對于 NVMe 協議測試,用戶將需要一個工具來觀察不同部分的交互方式。數據鏈路層、確認、流控制、多個隊列和多個命令需要協調。在一次 NVMe 讀取中可能需要分析數千個數據包。一個好的工具將

總結

溝通并幫助深入了解解決任何運營問題所需的細節。隨著 NVMe 規范的發展,協議分析器將繼續成為用戶驗證設計的寶貴工具。

仿真是 NVMe 測試的另一個重要方面。用戶需要能夠在操作中創建多個隊列和命令,以確保控制器可以管理不同類型的配置。這種模擬過程的配套工具稱為 NVMe 練習器。這些工具可以執行識別常見實施錯誤的驗證測試序列。

驗證設備是否符合 PCI-SIG 標準的最終目標是互操作性、可靠性、與先前 PCIe 標準的向后兼容性以及上市速度。協議級測試需要靈活設計的工具,不僅針對當前這一代的挑戰,而且理想情況下具有內置功能,可以預測這些層在未來版本的規范中的演變。無論是基于 PCIe 還是基于 NVMe,正確的綜合測試解決方案集將繼續幫助驗證團隊通過工具克服驗證挑戰,并支持他們進行快速準確的測試。

審核編輯:郭婷

-

控制器

+關注

關注

112文章

16205瀏覽量

177421 -

總線

+關注

關注

10文章

2867瀏覽量

87991 -

PCIe

+關注

關注

15文章

1217瀏覽量

82445

發布評論請先 登錄

相關推薦

PCIe 4.0與PCIe 3.0的性能對比

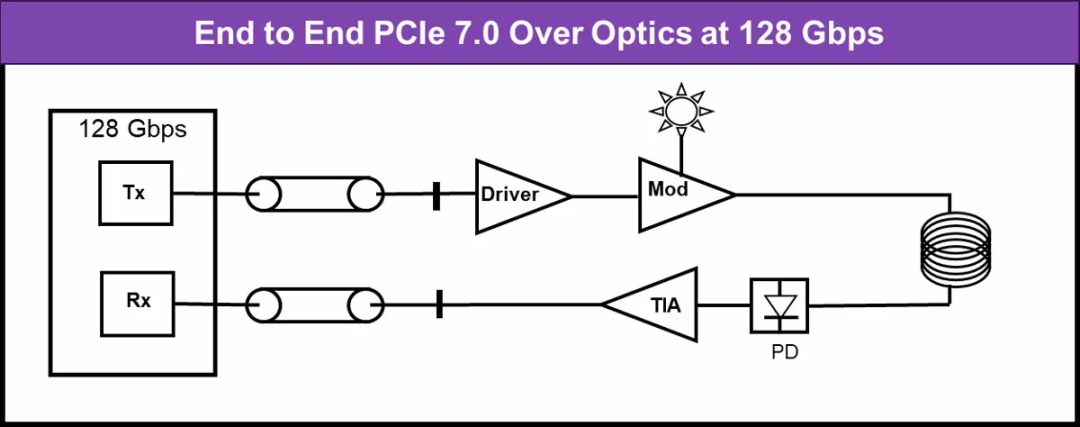

PCIe光傳輸的優勢與挑戰

Prodigy Technovations推出功能強大的PCIe Gen5協議分析儀

新思科技PCIe 7.0驗證IP(VIP)的特性

pcie4.0和pcie3.0接口兼容嗎

FPGA的PCIE接口應用需要注意哪些問題

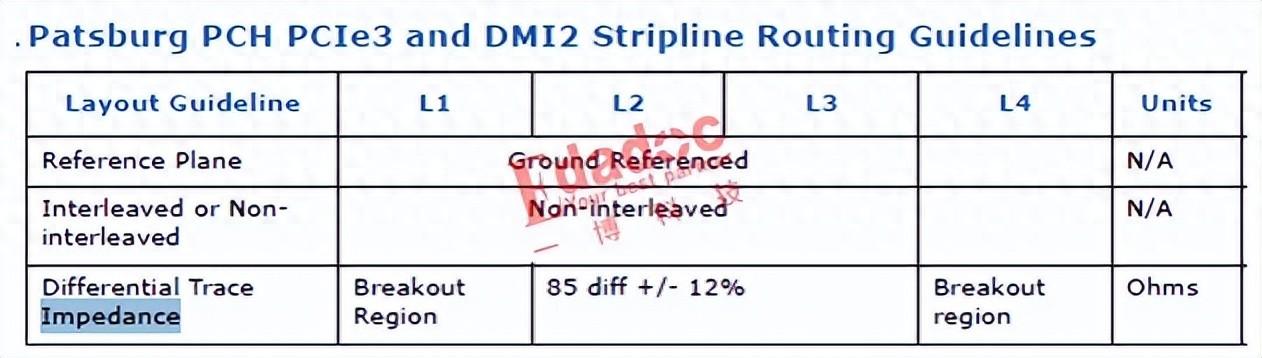

PCIe系統阻抗控制85還是100的驗證

什么是PCIe?PCIe有什么用途?什么是PCIe通道

PCIE的阻抗控制,到底是選擇85還是100歐姆好?

解決PCIe協議驗證挑戰

解決PCIe協議驗證挑戰

評論