引言

在半導體芯片的物理和故障分析過程中(即驗證實際沉積的層,與導致電路故障的原因),為了評估復雜的半導體結構,擁有適當的處理工具至關重要。為制造的每件產品開發了去加工技術,涉及多步pfo程序,揭示芯片的逐層秘密。隨著制造工藝的變化和半導體結構的變化,這些技術需要在時間和程序上不斷調整。雖然有許多工具有助于這些分析,如RIE(反應離子蝕刻-一種干法蝕刻技術)、離子銑削和微切割,但鎢的濕法化學蝕刻有時比RIE技術更具重現性。

鎢是MOS(硅上金屬)器件中用于互連和電路的常用沉積金屬。襯里材料用于橋接金屬-硅,或防止金屬和摻雜硅襯底之間的相互作用。耐火互連襯里可以包括MoSi或WSi,而阻擋材料包括TiW和TiN。在某些情況下,制造過程中引入的外來物質(FM)會腐蝕桿或襯墊材料。FM會形成不必要的連接(短路)或不必要的絕緣(開路)。在對芯片進行電氣測試后,失敗的信號通常指向導致電路故障的缺陷源。作為一個例子,如果電測試信號指示鎢層下面有缺陷,則希望僅去除鎢,同時保持襯墊的完整性,以評估缺陷的來源。在其他方面例如,需要高亮蝕刻以使鎢稍微凹陷并限定襯里層。在這兩種情況下,鎢的一些表面(自上而下或橫截面)必須在鎢蝕刻之前暴露。

腐蝕劑描述

兩種相當快速和容易的濕法蝕刻將去除鎢但保留大部分襯墊完整,它們是:1)次氯酸鈉(na0ci)和2)1∶1比例的氫氧化銨(NH?0H)和過氧化氫(H2Oz)。蝕刻劑如下,并且基于最終得到可溶產品,為這些蝕刻劑中的每一種提供化學反應。

1)使用家用漂白劑(5.25%次氯酸鈉)。試劑等級也可以,但通常不值得花費。在Pyrex燒杯中加熱約50至100 mL至60°c。該蝕刻劑可使用6小時而無明顯降解,但在此之后應進行處理和補充。

所得的可能反應產生二氧化二氯鎢(W02CIz)的溶度積:

3 NaCI 0+W+Hz0-> Woz ciz+NaCl+2 na0h

2)在室溫下,在Nalgene、玻璃或teflon燒杯中混合試劑級NH?0H與Hz0z的1:1溶液(使用35% H2O2)。為獲得最佳可靠性,請在混合后2小時內使用,因為Hz0t會分解。可能發生的反應產生仲鎢酸銨((nh?)zw 0236 H2O)的溶度積:

7w+21hz+6nh?0h-->(nk?)?w 023 ' 6h 0+18hq

不銹鋼或耐化學腐蝕的鑷子也可以。將芯片放在邊緣并靠在燒杯上,以幫助從燒杯中取出芯片。確保芯片足夠大,能夠被Geezers抓取,而不會損壞有缺陷的區域。鎢在受到攻擊時會嘶嘶作響。根據去除鎢的厚度,試驗2到10分鐘,或者只需5到15秒進行高亮蝕刻。蝕刻后,將芯片浸入干凈的去離子水燒杯中,然后在去離子水流中沖洗幾秒鐘。仍然拿著芯片,用干N2吹干。如果你的結構能夠承受,超聲波清洗是可以的,但是通常不需要。

優化技巧:

為了確定“完美”的蝕刻時間,使用這些蝕刻的增量時間,并用掃描電鏡檢查以確定蝕刻的深度。嘗試使用大致相同的芯片尺寸和去加工狀態,以最大化蝕刻的再現性。在精密的環境中,缺陷區域周圍可消耗的鎢的量會影響蝕刻時間。

為了加快這一程序的發展,使用低電壓SEM(即2 KeV,500 pA -最好是FESEM)進行無涂層自上而下和簡單的切除截面評估。在優化這些程序的時間時,請始終使用新鮮樣品。即使在低電壓下,SEM樣品也可能被電子束沉積的碳、回流的油和室中的污染物覆蓋,如果這種類型的樣品被再次蝕刻,這將顯著改變蝕刻時間和質量。雖然用氧等離子體灰化有助于去除SEM產生的沉積物,但結果并不理想。即使如此,如果只有一個樣品,有時也需要灰化和重新蝕刻樣品。蝕刻完成后,盡快進行SEM評估,因為新蝕刻的表面容易受到持續蝕刻和環境侵蝕的影響。當脫層發生時,光學顯微鏡將顯示顏色變化,并且共焦顯微鏡有助于評估去除深度,而SEM在去除過程中提供最單一的信息。

濕法蝕刻與干法蝕刻

有幾個原因可以解釋為什么去加工甚至去高光被認為是一門“藝術”而不是一門“科學”。金屬沉積技術、外形、密度、結構和微結構都將在金屬蝕刻方式中發揮重要作用。今天有效的蝕刻時間和配方并不能保證對明天生產的產品也有效。在鎢互連的情況下,互連中心的金屬密度或微結構的接縫或變化創建一條比金屬探針阻力最小(因此蝕刻速度更快)的路徑。互連的核心首先被蝕刻掉,留下襯在互連周邊的逐漸變薄的金屬殼,并且在清除互連之前,下面的鎢線可能發生不希望的蝕刻。

為什么選擇濕法蝕刻技術而不是反應離子蝕刻(RIE)?理論上,RIE技術對鎢沉積規律的敏感性應該低于set蝕刻。RIE可以被優化用于具有不同縱橫比的蝕刻(各向同性或各向異性蝕刻),理論背后的事實是通過RIE完全單一形式的鎢去除是最好的精細操作。氣體流量、比率、壓力和時間都是需要連續測試才能開始優化過程的變量。此外,在大多數情況下,金屬圖案的變化(密集區域與非密集區域)對RIE技術的影響比化學蝕刻更深遠。周圍的結構會遮蔽RIE工藝,并且RIE腔室的臺板通常具有“蝕刻圖案”,即,根據腔室內的位置,RIE蝕刻速率可以是定向的,甚至是有角度的。

RIE室的裝載也影響去除速率,因為完整的八英寸晶片的蝕刻速率比裝載到室中的幾個一厘米的芯片要慢得多。這就是“負載系數”,指的是待蝕刻材料的表面積。當氣流、時間和功率保持不變時,消耗的表面材料的量受到存在的反應氣體量的限制。一個完整的8 '晶圓的蝕刻方式與從該晶圓上切下的幾個芯片的蝕刻方式不同(即,你不能用一雙杯狀的手清空銼刀,但你可以清空水槽)。

與濕法蝕刻不同,即使在最嚴密監控的RIE系統中,盤形夾也總是具有從芯片邊緣向中心的蝕刻梯度。也不同于濕法蝕刻,RIE室受到反應組分和吸收氣體在室內壁上的積聚的困擾,特別是如果工具不僅僅用于鎢蝕刻,這些積聚需要在均勻蝕刻之前進行清潔和室調節。雖然這些都是影響RIE工具的考慮因素、室內蝕刻特性的仔細評估和RIE蝕刻結果的分析可以產生在某些情況下優于濕法蝕刻的技術。

雖然濕法和RIE蝕刻技術都可以提供成功的結果和顯著增強的分析能力,但是這兩種技術都不能提供最佳的現成結果。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27014瀏覽量

216339 -

MOS

+關注

關注

32文章

1247瀏覽量

93482 -

蝕刻

+關注

關注

9文章

413瀏覽量

15346

發布評論請先 登錄

相關推薦

鋰電池行業中干法研磨與濕法研磨的應用

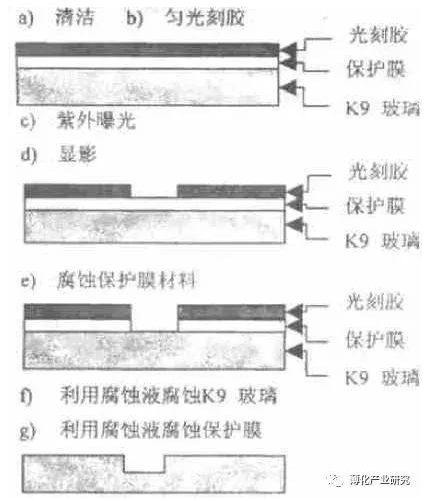

玻璃基電路板的蝕刻和側蝕技術

玻璃電路板表面微蝕刻工藝

基于光譜共焦技術的PCB蝕刻檢測

利用貝塞爾光束、超短雙脈沖激光和選擇性化學蝕刻研究玻璃通孔(TGV)

關于兩種蝕刻方式介紹

影響pcb蝕刻性能的五大因素有哪些?

半導體濕法技術有什么優勢

電偶腐蝕對先進封裝銅蝕刻工藝的影響

Si/SiGe多層堆疊的干法蝕刻

揭秘***與蝕刻機的神秘面紗

基于深氮化鎵蝕刻的微米尺寸光子器件的研制

在氮化鎵和AlGaN上的濕式數字蝕刻

濕法蝕刻與干法蝕刻有什么不同

濕法蝕刻與干法蝕刻有什么不同

評論